FPGA芯片IO口上下拉電阻的使用

- 為什么要設置上下拉電阻

- 一、如何設置下拉電阻

- 二、如何設置上拉電阻

為什么要設置上下拉電阻

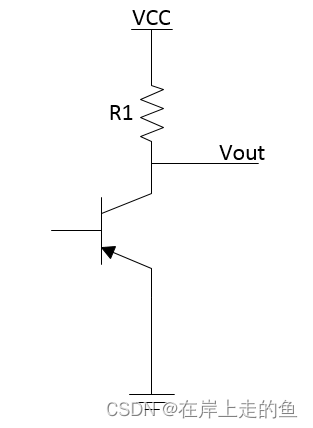

這里以高云FPGA的GW1N-UV2QN48C6/I5來舉例,這個芯片的上電默認初始化階段,引腳是弱上來模式,且模式固定不能通過軟件的配置來改變。如下圖所示:

上圖只是為了說明IO口的工作原理,其真實的IO口硬件架構需要去官網看對應的說明文件,通過上圖我們可以知道在FPGA初始化階段,三極管是默認不導通的,此時VCC通過R1連接Vout,Vout相當于初始化階段就輸出一個幅值為VCC的高電平;如果你的負載是高電平導通,則一上電負載就會導通,這個狀態一般是我們不想要的,有的FPGA的上拉下拉可以通軟件配置來解決,但是有的架構精簡的FPGA則只有單純的上拉模式且不能通過軟件更改上下拉配置,如GW1N-UV2QN48C6/I5。對于自帶上拉且不能通過軟件配置解決的FPGA,我們可以通過直接在IO口上掛下拉電阻來解決。

一、如何設置下拉電阻

掛一個下拉電阻就能讓弱上拉變成弱下拉,但是對所掛電阻的阻值確有要求,如下圖:

)

下載圖文教程(超詳細))

)