前一篇博客我們提到在線調試的時候, 可執行文件只要燒進板子,程序它就會自己跑起來,不會等你點

這個按鈕,它才開始跑。我們測試的模塊中,里面可能有幾個我們關心的信號,它會在程序剛運行很短的時間內發生狀態跳變。 當我們打算去捕獲它的狀態變化的時候,這個時候程序已經跑過了,這導致我們無法抓取到。那這個時候我們應該怎么辦呢? 引入VIO這個工具,用VIO的輸出信號作為我們測試模塊的使能信號,這樣我們就能控制待測試的模塊什么時候運行。

?VIO是個特別簡單的IP核,絲毫不用有畏難情緒。

1 VIO是什么

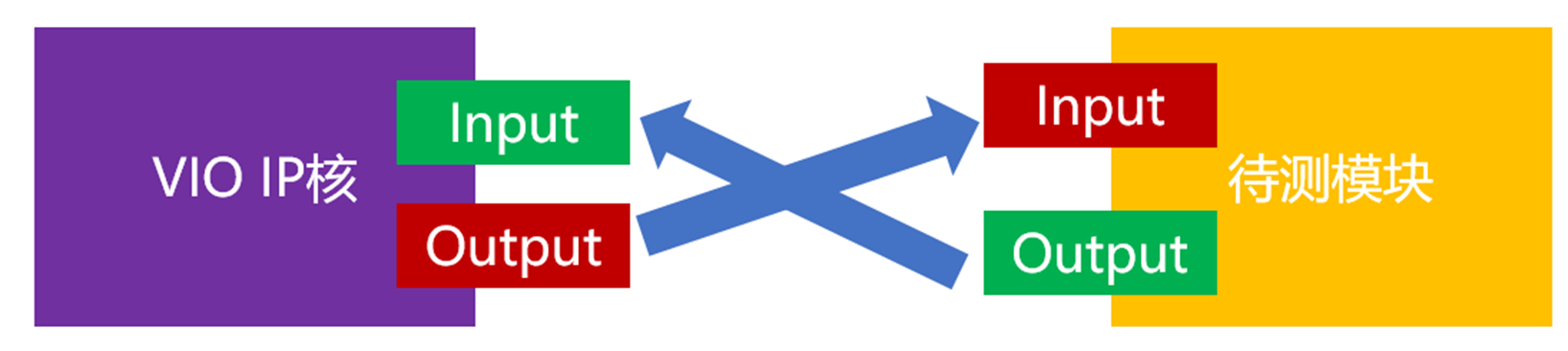

VIO是虛擬輸入/輸出(Virtual Input/Output),可以實時監測和驅動FPGA內部信號。 在線調試的時候,Vivado會提供一個VIO的界面,你可以修改VIO對待測模塊的輸出,也可以監測待測模塊對VIO的輸入。VIO和待測模塊的信號如下圖所示,就行串口通信一樣,你的Tx要接到我的Rx,

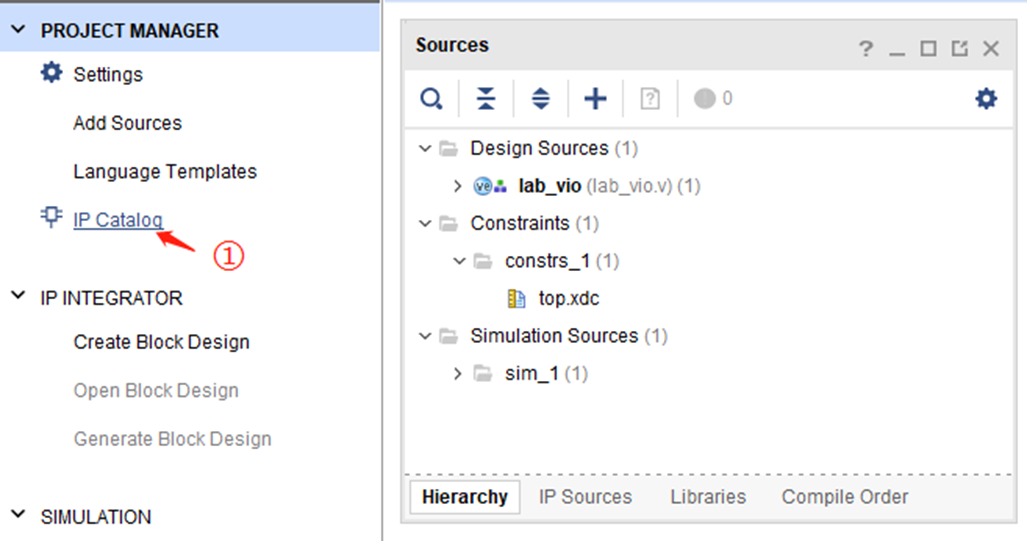

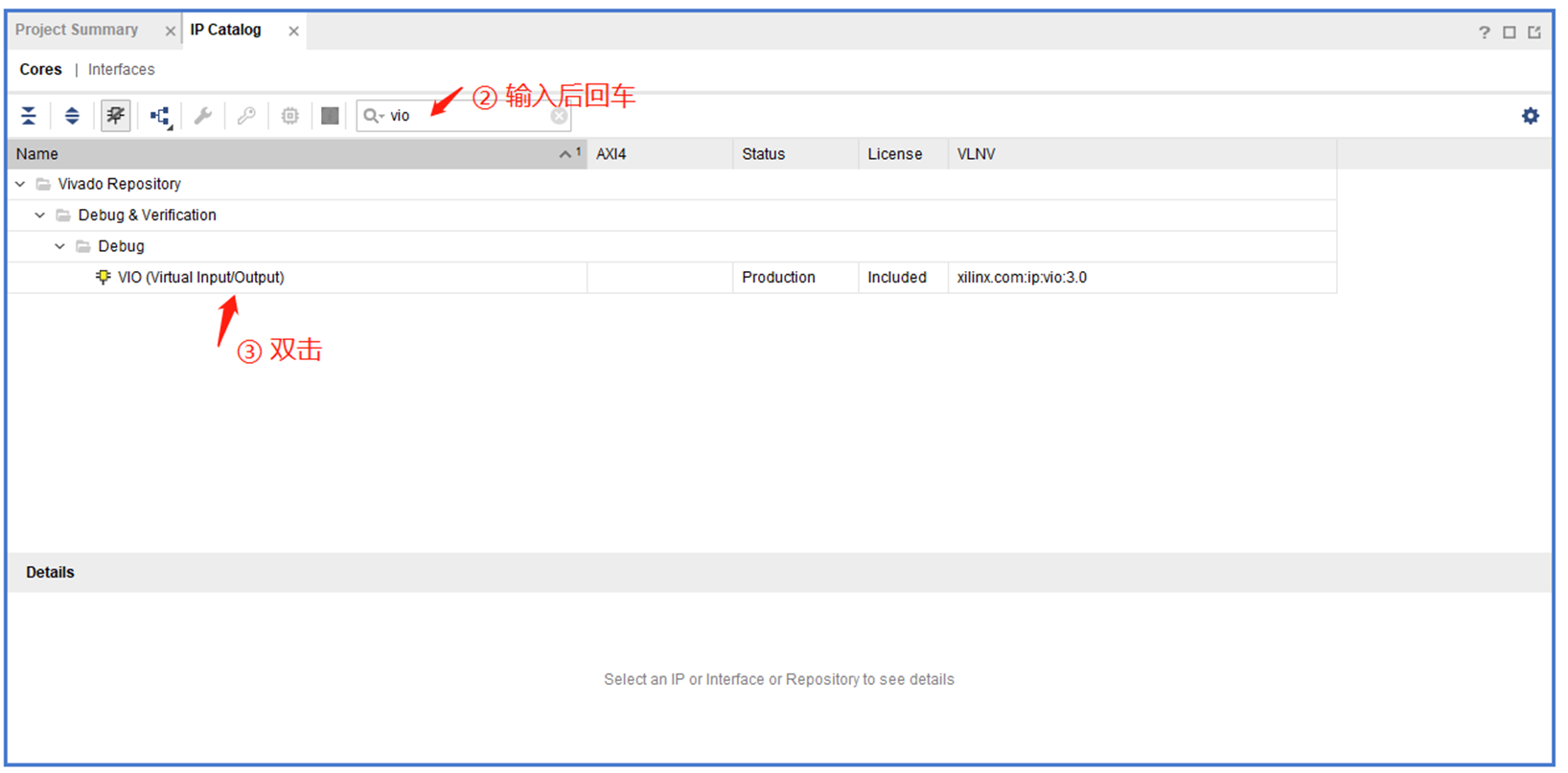

2 VIO IP 配置

截圖警告!

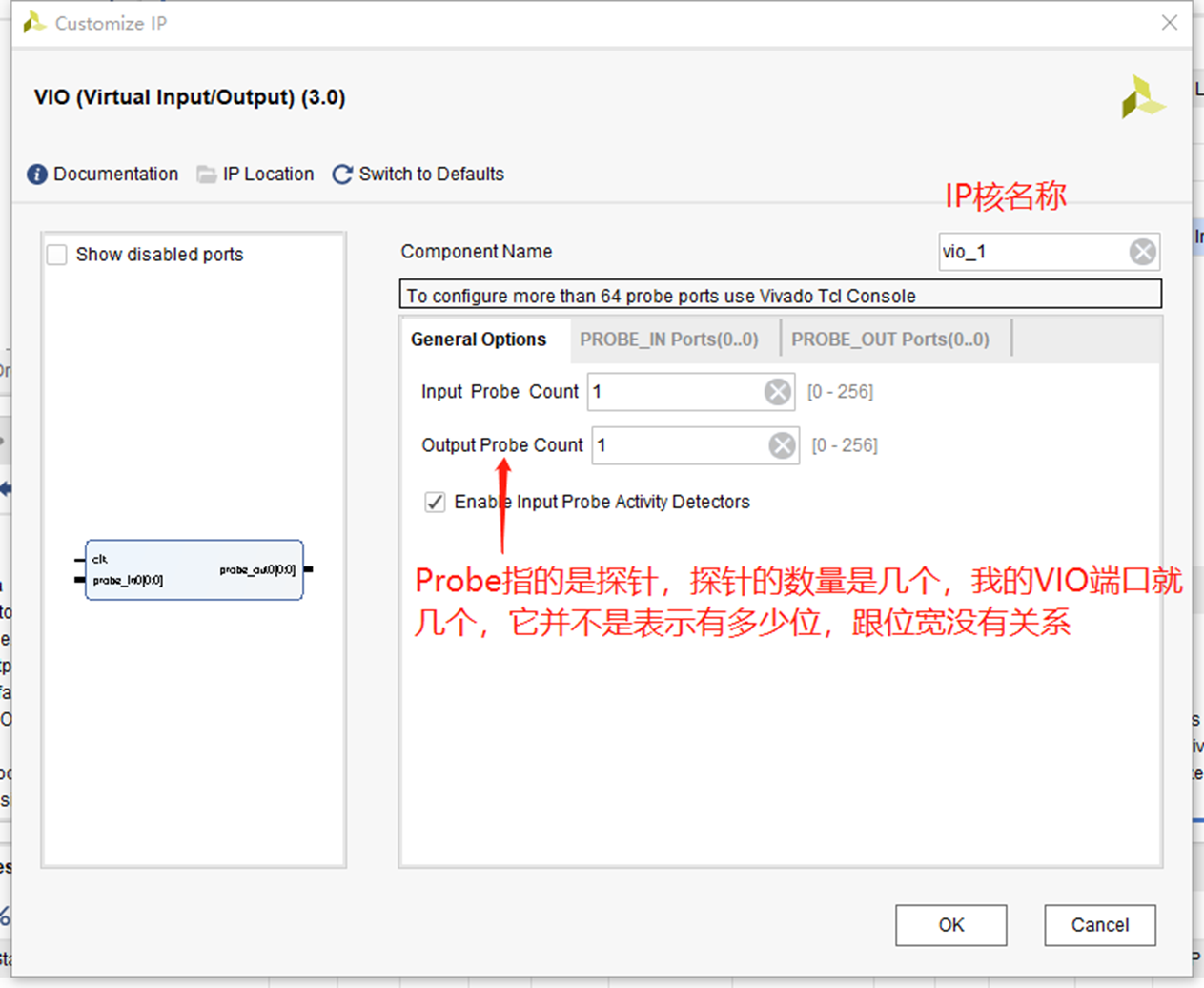

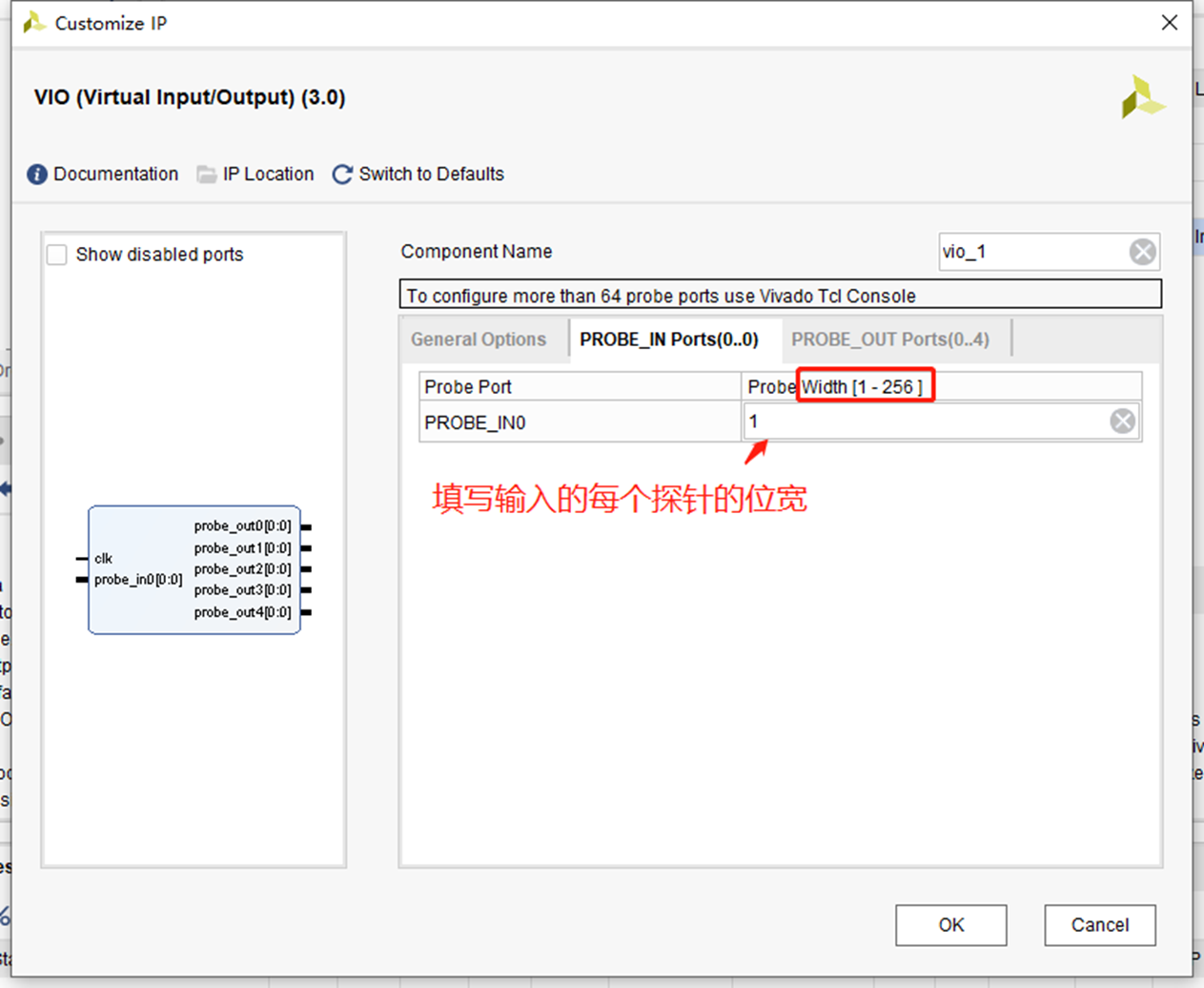

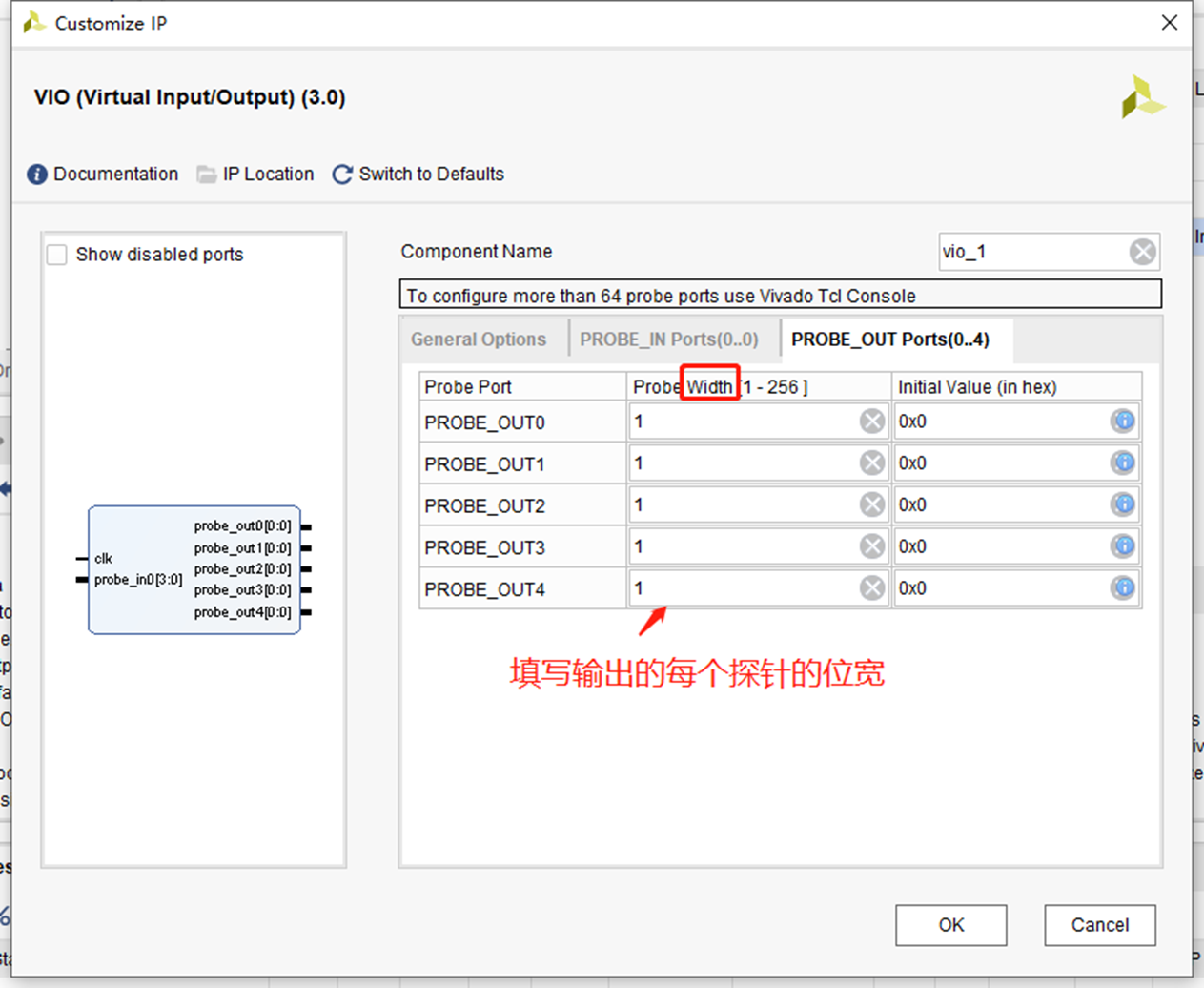

?我對下面這個截圖稍微補充一下哈, 截圖只是在介紹這個東西是什么,而我們的VIO例程里,這輸入探針數量是1,輸出探針數量是5。 IP核名稱是vio_0。

??我對下面這個截圖稍微補充一下哈, 截圖只是在介紹這個東西是什么,而我們的VIO例程里,這輸入探針位寬是4。

???我對下面這個截圖稍微補充一下哈, 截圖只是在介紹這個東西是什么,而我們的VIO例程里,這5個輸出探針位寬是2。

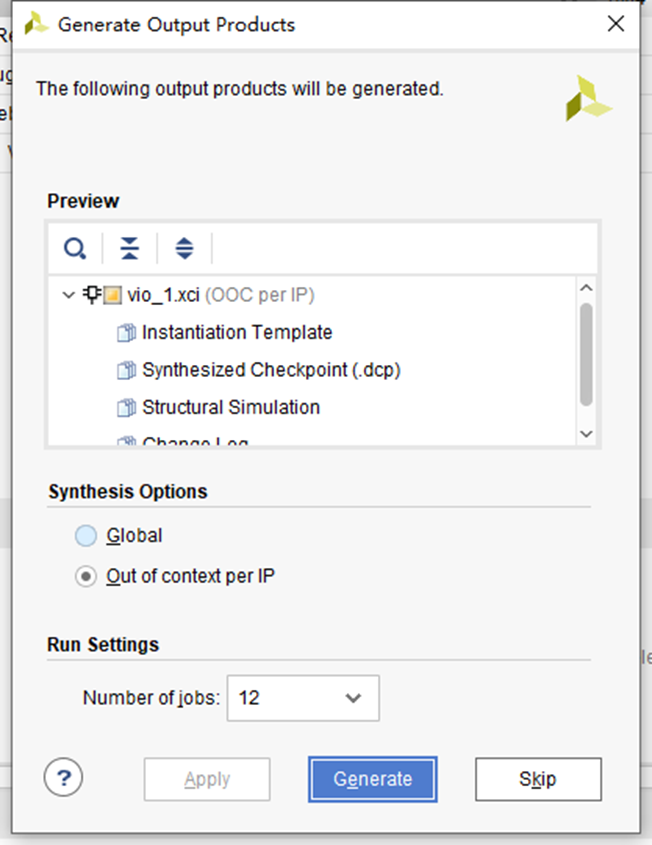

?Ok之后直接Generate

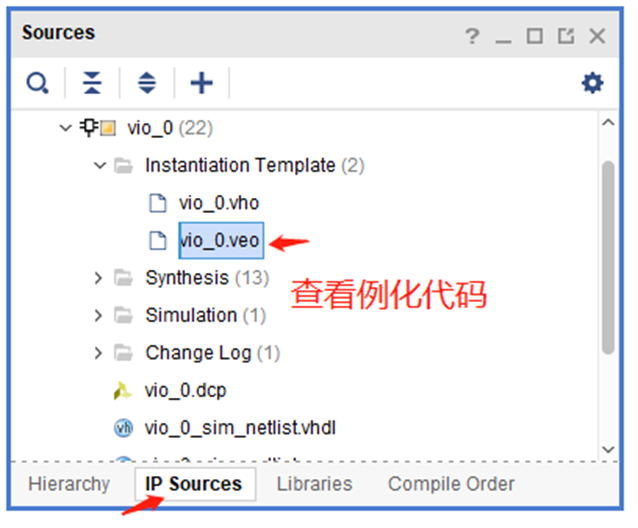

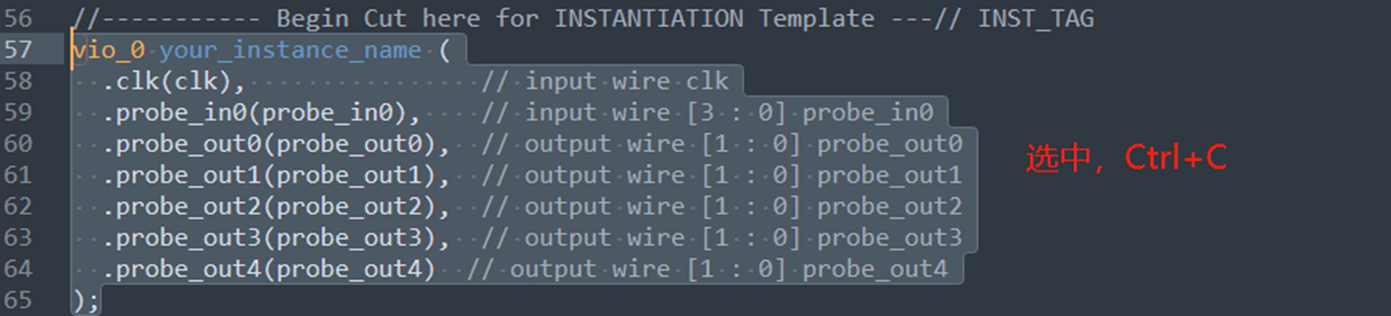

?IP核生成完了之后,都要去抄一下怎么例化。

?3 VIO測試用例:4選1-選擇器

`timescale 1ns / 1psmodule lab_vio(input wire clk

);reg [3:0] out; // 待測模塊的輸出 VIO的輸入

wire [1:0] a, b, c, d; // VIO的輸出 待測模塊的輸入

wire [1:0] sel; // VIO的輸出 待測模塊的輸入 always @(*) begincase(sel)2'b00: out <= a;2'b01: out <= b;2'b10: out <= c;2'b11: out <= d;default: out <= 2'bx; endcase

end vio_0 vio_0_inst (.clk(clk), // input wire clk.probe_in0(out), // input wire [3 : 0] probe_in0.probe_out0(a), // output wire [1 : 0] probe_out0.probe_out1(b), // output wire [1 : 0] probe_out1.probe_out2(c), // output wire [1 : 0] probe_out2.probe_out3(d), // output wire [1 : 0] probe_out3.probe_out4(sel) // output wire [1 : 0] probe_out4

);

endmodule

管腳約束代碼,我們只用到了clk

create_clock -period 20.000 [get_ports clk]

set_property PACKAGE_PIN N18 [get_ports clk]

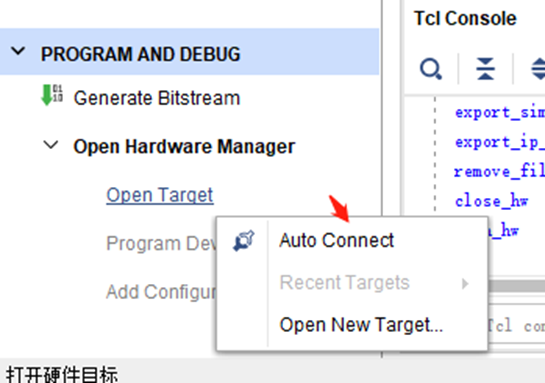

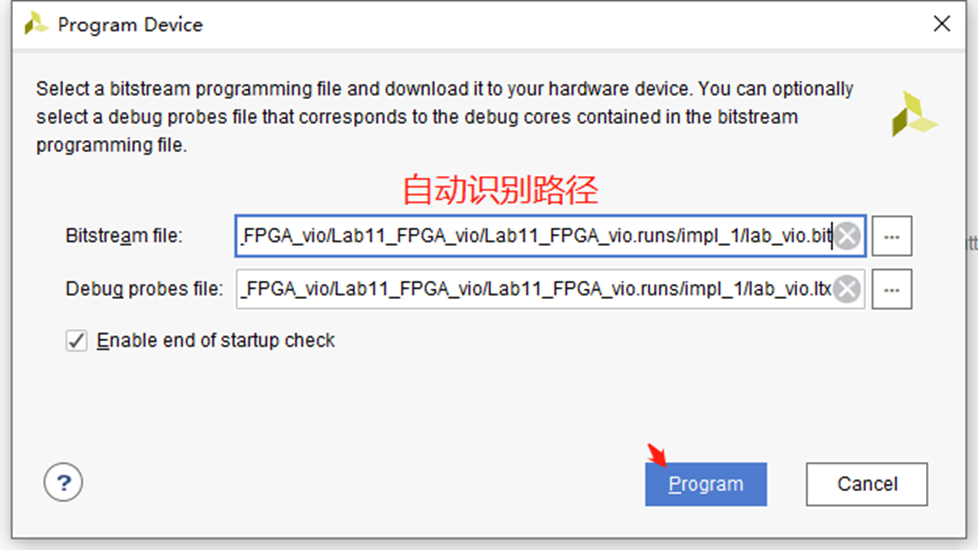

set_property IOSTANDARD LVCMOS33 [get_ports clk]4 在線調試

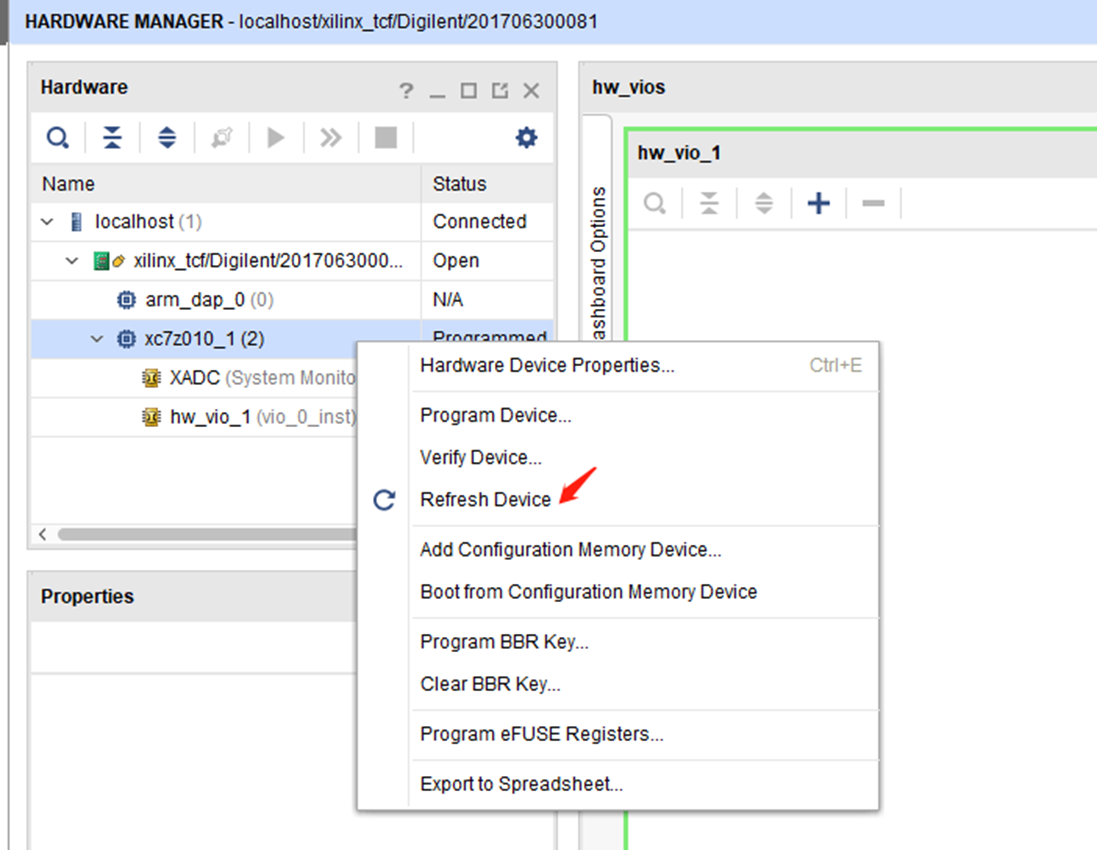

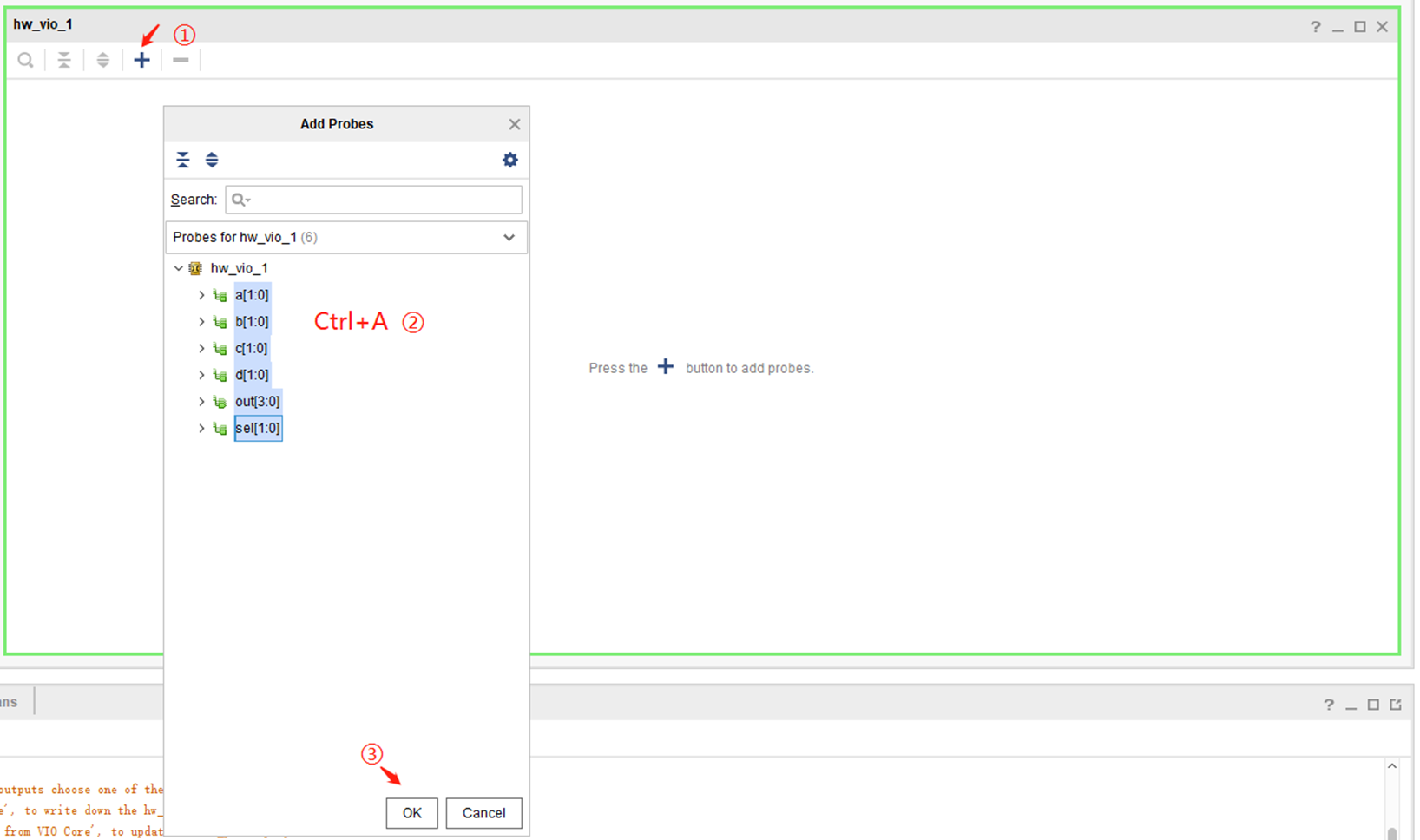

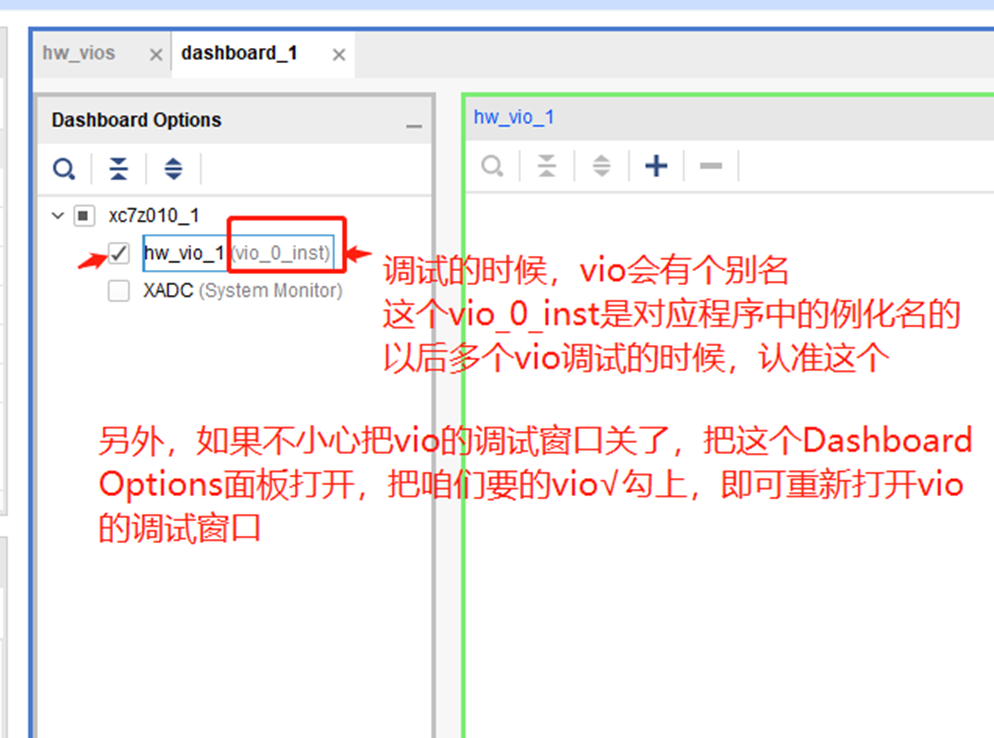

截圖警告!

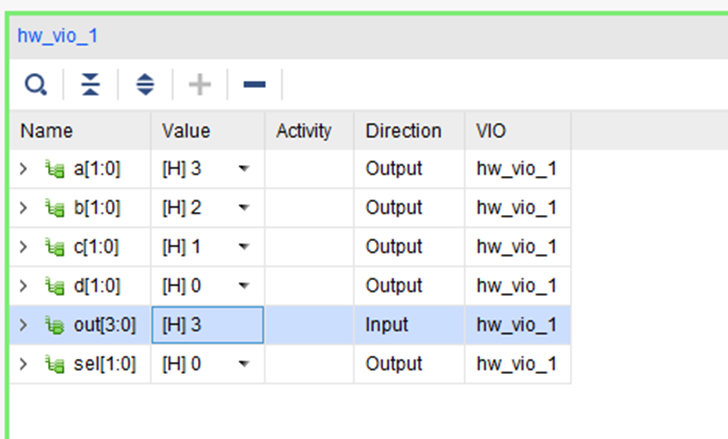

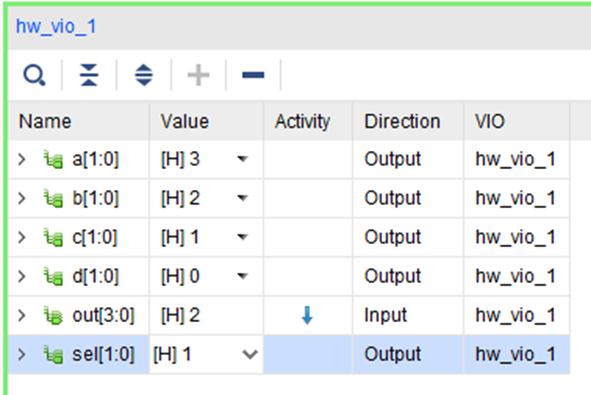

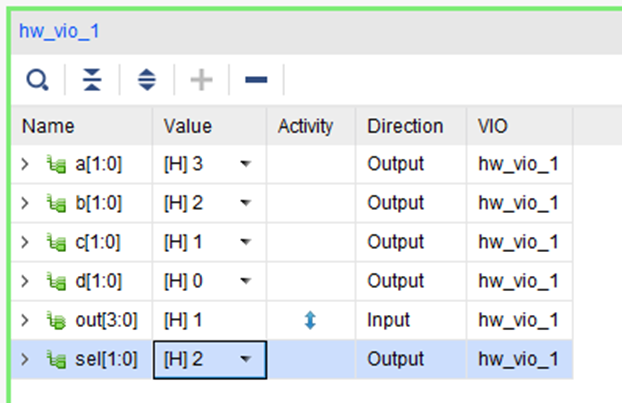

假設我設置 a b c d 分別為3 2 1 0, 然后分別設置sel為0 1 2 3,檢測out的變化

|  |

|  |

?通過以上的小實驗呢,我們就算是基本掌握VIO的用法了,是不是很簡單呢?

參考文獻

Vivado調用VIO核_vio vivado_素年錦什的博客-CSDN博客

- 使用label組件)

---死鎖和Synchronized加鎖流程)

: 數據倉庫與ETL的關系及ETL工具推薦)

)