1 Overview

This section introduces someting that maybe you need to know before learning.

Note:This CPU is based on MIPS instruction set.

1.1 Tools

- Logisim

- CS 3410 Components

- MARS MIPS simulator

- Win10 or Mac OS

1.2 Courses

- 自己動手畫CPU《計算機組織與結構實驗》

- 計算機硬件系統設計

1.3 Front Knowledge & Reference Books

- Computer Organization and Design

- Degital Logic Applications and Design

- See MIPS Run

2 Core Thinking

本小節將會介紹設計單周期CPU的核心思想和重要觀念。

注:本文討論的單周期CPU完全理想化,不考慮時間延遲問題。

2.1 基于組合邏輯的單周期CPU

我們先來談談 組合邏輯器件 和 存儲器件

- 組合邏輯器件:就像一個兩邊開口的水管,水進水口(輸入端)進入,經過水管“處理”(指組合邏輯器件的功能),從出水口(輸出端)流出,沒有任何的阻攔

- 存儲器件:就像兩邊都帶閥門的水管,在閘門沒有開的時候,既不能進入,也不能出去

- 讀取:將出水口(輸出端)的閥門打開

- 寫入:將進水口(輸入端)的閥門打開

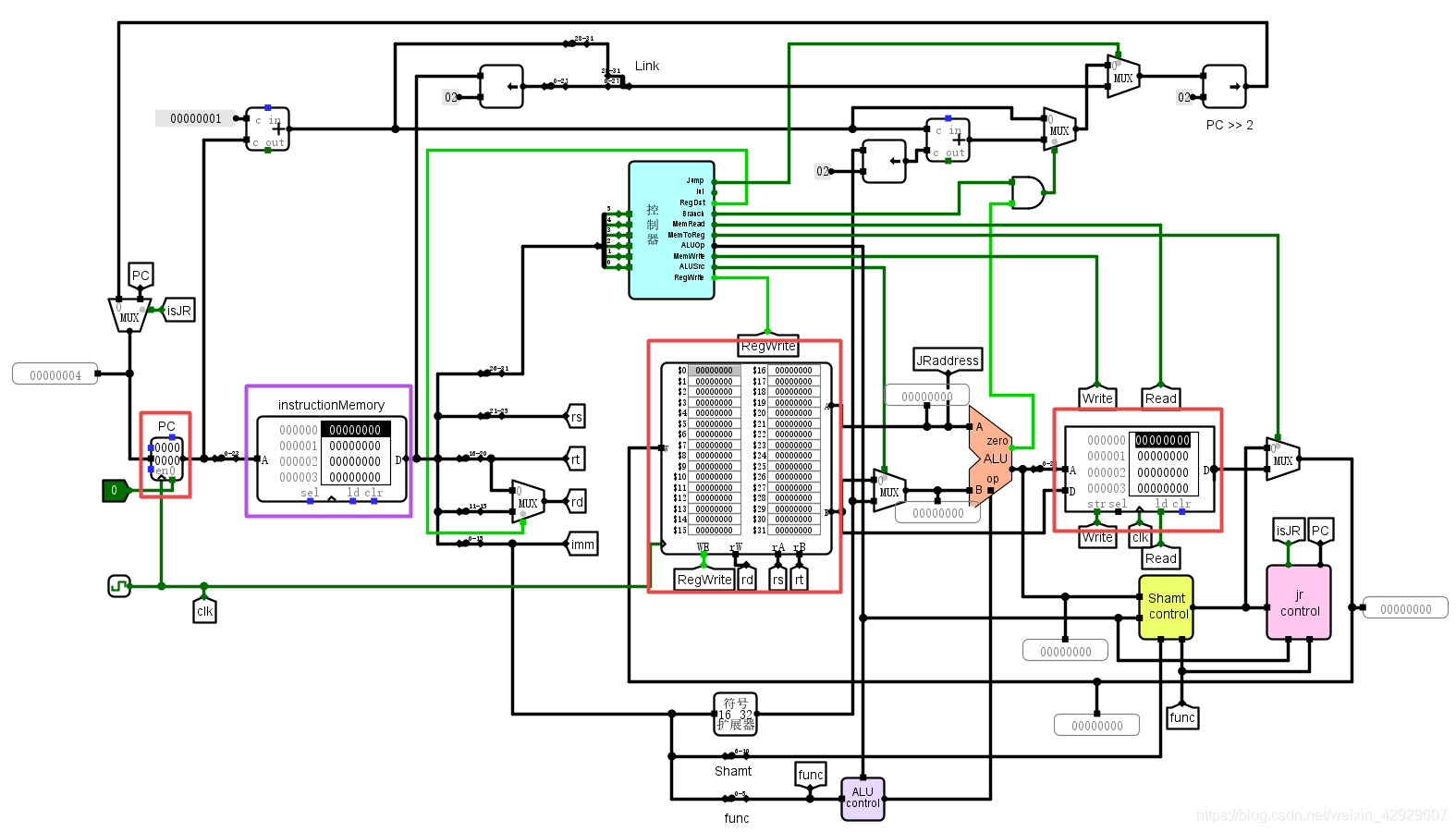

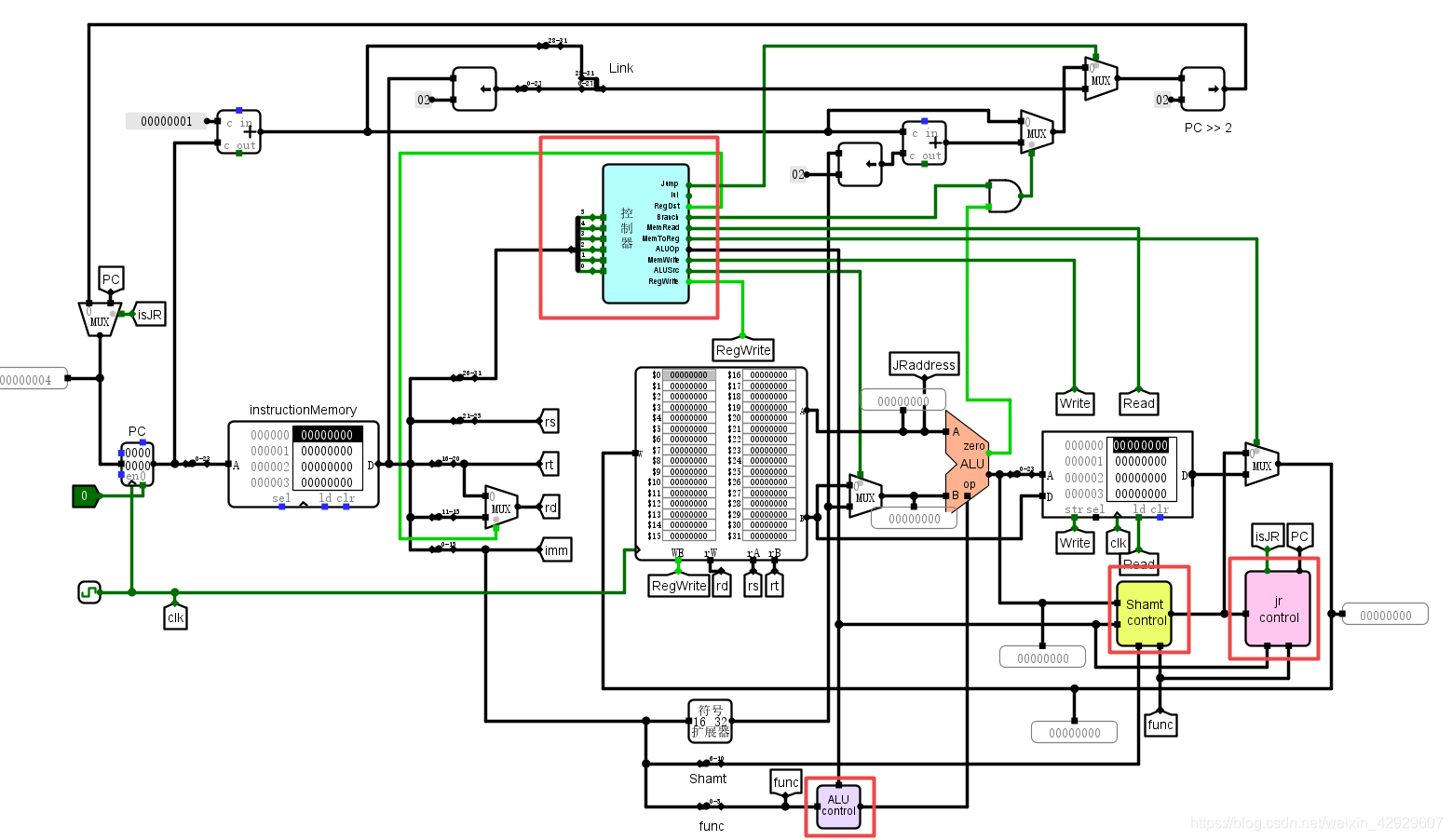

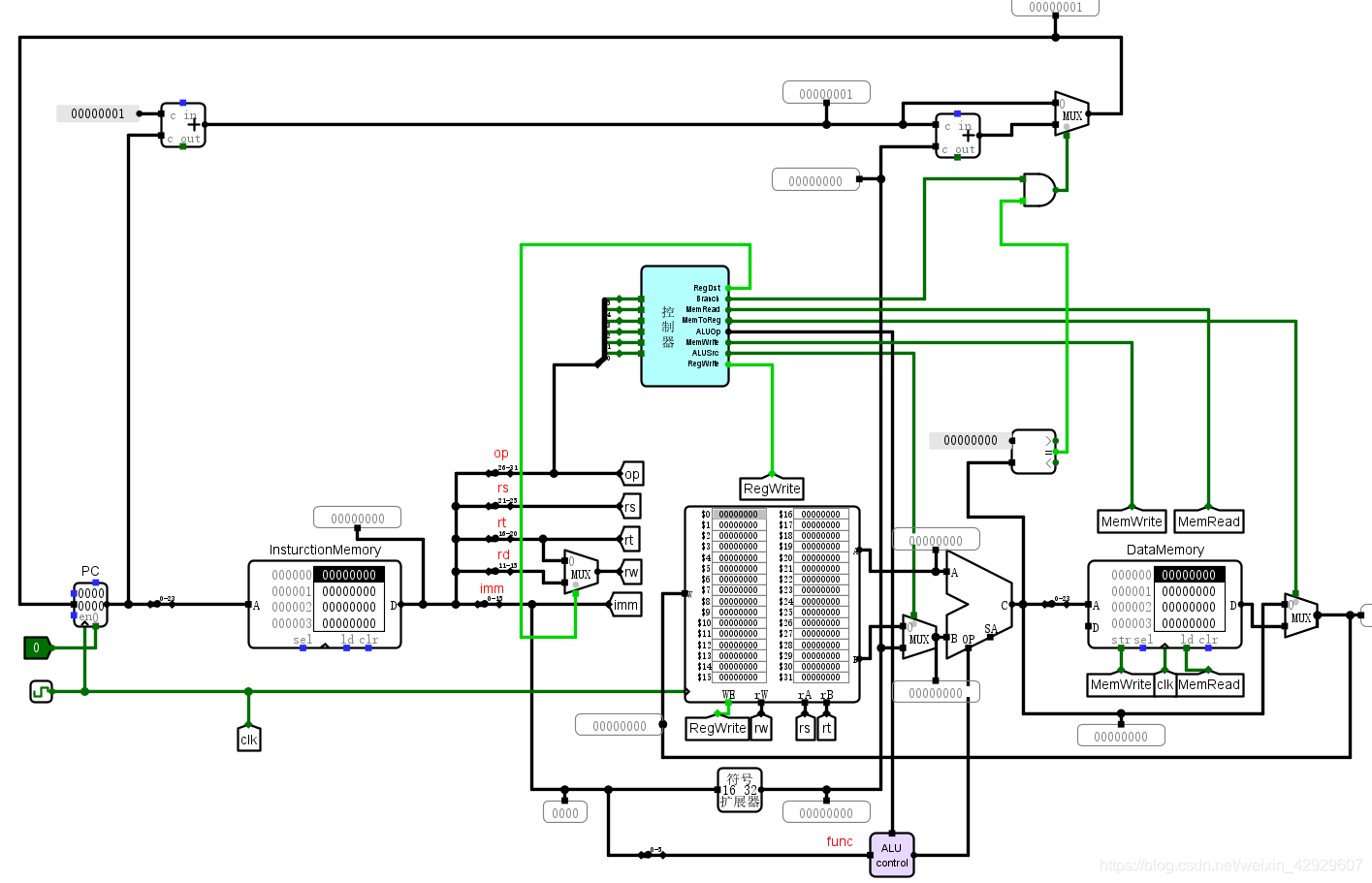

我們再來看一個做好的單周期CPU

圖中框出的部分是存儲器件,其余部分全是組合邏輯器件。

紫色框的器件是指令存儲器,它的讀取是不受限制的,給出地址就能立即讀出,因此它的功能可以理解為一個組合邏輯。

紅色框的器件自左到右分別是PC寄存器、寄存器堆和數據存儲器,它們的讀取是不受限制的,但是寫入受到限制,這些確實發揮了存儲器件的功能。

- PC寄存器的寫入是下降沿觸發,當時鐘變化為

1-->0的時候,能夠寫入新的值 - 寄存器堆和數據存儲器是上升沿觸發,寫入控制信號為

1且時鐘變化為1-->0的時候,能夠寫入新的數據

顯然,這個系統是一個由時鐘控制、由組合邏輯器件和存儲器件共同構成的時序邏輯電路,它的工作情況是(以add指令為例):

- 當時鐘

1-->0的時候,PC寫入新的值,這個值就是指令的地址,指令由指令寄存器輸出 - 指令被譯碼,發送給中心控制器,ALU控制器,以及寄存器堆

- 寄存器堆的數據被讀出,送給ALU,ALU根據譯碼結果運算,得到的結果被送到寄存器堆的門口,等待寫入

以上的過程,都是在時鐘信號為0的時候,以極快的速度,按順序地、無阻攔地執行和完成的。 很明顯,這具備組合邏輯器件的特征,看起來,這就像是一個復雜的組合邏輯器件而已。

簡化來說,這就像是

- 將指令碼輸入該器件

- 該器件直接輸出

add的結果,該結果會被攔在寄存器堆的“入口”

當然,如果是sw指令的話,數據一樣會被運算出來,然后被攔在數據存儲器的“入口”。

以上過程,是近乎完全的組合邏輯,這也就意味著,它非常容易設計,甚至,只需要給出輸入和輸出,就能被自動地生成,現代計算機完全可以做到這點。

接下來,我們再看看被攔在寄存器堆(Register Files)入口的數據吧。

- 時鐘信號變化:

0-->1,如果允許寫入的信號有效,“門”就會被打開 - 之后數據就能夠被寫入進去了

再之后,時鐘1-->0又開始重復之前的過程……

回看本小節的標題,我像你能夠理解什么是基于組合邏輯的單周期CPU了。

2.2 信號的設計:受外部約束的信號 與 自由設計的內部信號

在CPU的設計中,我們需要指令譯碼,通過控制器生成控制信號,來控制CPU各部件的工作,因此,我們就需要設計合理的控制信號。

我們來看看CPU的控制部件:

這里的CPU設計了4個控制部件

- 中心控制器

- ALU控制器

- 移位操作控制器

- jr操作控制器

我們這里只說關注兩種,了解后兩種。

分治思想

首先,我們要分清楚,必須遵循的MIPS指令集信號和自行設計的內部信號。

我們的CPU要實現MIPS指令集的一部分,因此,必須遵循它的設計規范,例如

- 中心控制器的輸入端必須是MIPS的Op字段中的信號

- ALU控制器的func輸入端必須是MIPS的func字段的信號

- 移位控制器的輸入必須是MIPS的Shamt字段的信號

而我們內部信號的設計,是可以自己決定的,只要能夠正確地完成指令規定的功能就可以,當然要考慮復雜度等問題,這點我們先不關注,例如:

- 中心控制器的輸出信號,控制著各部件的運行狀態,必須與指令功能匹配

- ALU控制器的輸出信號,決定了ALU的運算類型,必須與指令功能匹配

- ……

這里,我們也可以將中心控制器和ALU控制器合并在一起,拆開是為了硬件設計的降低復雜度,你可以看到,我們還拆開出了移位控制器和jr控制器,事實上,都可以任意地合并,甚至ALU本身也可以集成進去,這完全取決于你的設計,這很自由,唯一可能的constraint可能就是你要讓器件邏輯清晰并且性能較好。

3 Design a CPU: A Top-Down Approach

本節介紹了設計CPU的核心方法,我們采用自頂向下和知識屏蔽的方法,快速完成一個簡易CPU的設計。

3.1 CS 3410 Components Guide

- CS 3410 Components Guide

我們先來簡要地介紹一下我們需要使用的CS 3410器件,在此特別感謝加利福尼亞大學提供的寶貴資源!

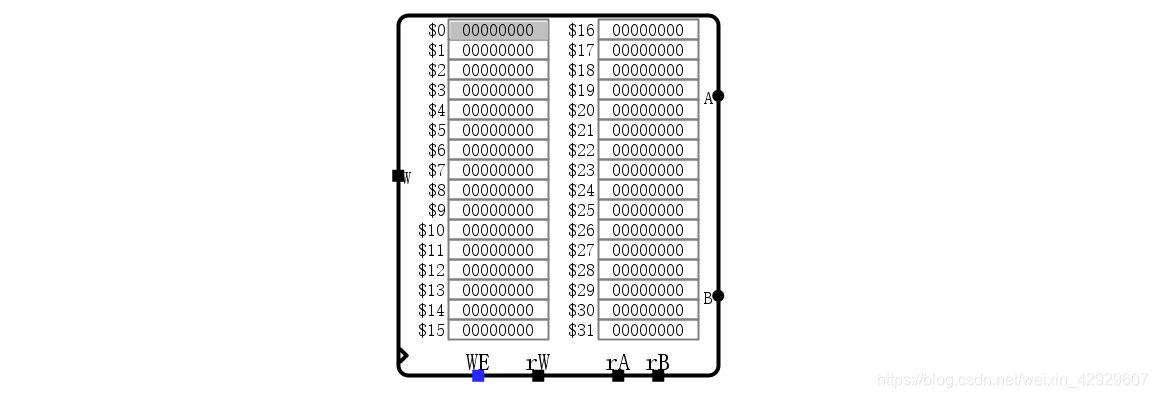

3.1.1 Register Files

A 32-bit wide by 32-registers deep register file. Register

$0is hard-wired to zero at all times, and writes to$0are ignored. You can rely on register$0always containing 0, and do not need to test that its value does not change. InputsrAandrBare used to select register values to output on theAandBoutputs. When the clock is triggered, ifWEis high, the data value at inputWis stored in registerrW. The register file can be configured to use rising clock edges as trigger (the default), falling edge, or to be level sensitive.

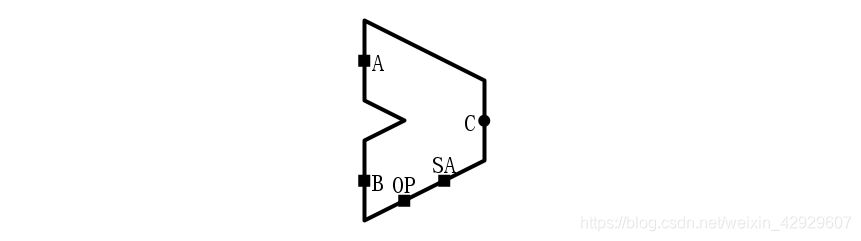

3.1.2 MIPS ALU

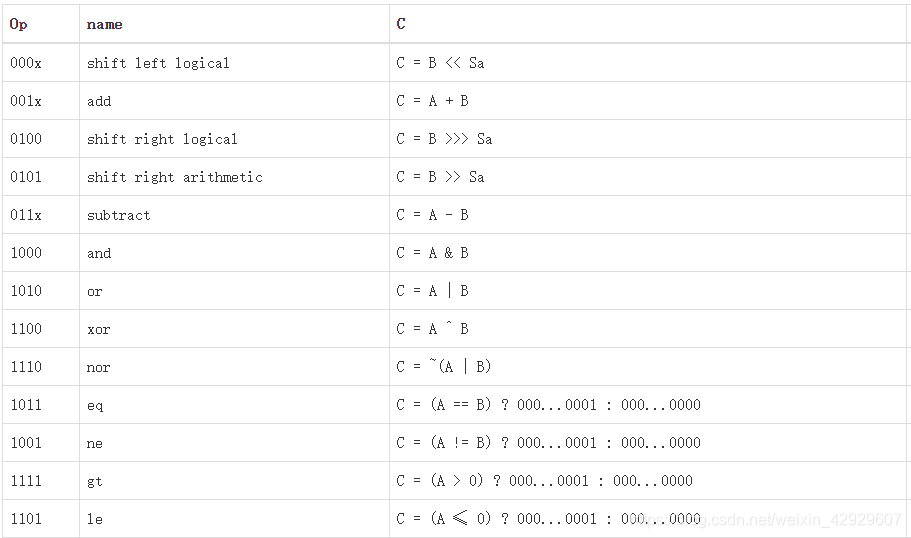

Computes a result as follows. You do not need to test the provided ALU, and can assume it will work exactly as specified.

為簡化起見,我們最開始只使用這兩個器件,其余的使用Logisim自動的就好。

3.1.2 MIPS Program ROM

我們不使用提供的指令ROM器件,但是,有一些重要的東西需要強調,非常重要!

An interesting aspect of the ROM is that the offset for branch instructions must be a multiple of 4, which assembles to an output offset divided by 4. This output offset follows the MIPS specification and needs to be left shifted by 2 to be added to PC. For example, given an instruction BEQ $0, $0, 4, the outputted offset in binary is 1.

我們采用的ROM是存儲單元是32位的,并不是8位,這也就意味著我們的指令地址是1的倍數而不是4的倍數,我們的PC自動機,先PC << 2,然后+4,之后再PC << 2,而對于branch指令,我們需要先offset << 2然后與PC + 4相加,之后再>> 2,最后賦給PC,這一點在設計的時候要尤為注意,后面的示例中,這個地方的設計是錯誤的,請讀者來修改。

3.2 The soul of CPU design:Abstract and Logic Design

CPU設計最重要的就是邏輯和抽象設計,實現是將抽象轉化為現實,并且反過來驗證它,毫無疑問的是,無設計,無實現,這可不可能像你最開始學習C語言那樣,隨便想想就開始寫,一個復雜系統的實現,必須:

- 先有現實世界的需求

- 再有抽象的邏輯設計

- 再進行計算機世界的實現

- 反復迭代上述3個過程

讓我們來看看CPU的設計,需要做哪些工作吧。

現在我們擁有的

- MIPS Instruction Set

- ALU Control Signal

我們需要設計的

- 中心控制器的信號

- ALU控制器的信號

我們只需要將這幾個控制器協調好,幫助我們完成MIPS指令的功能,就能夠讓CPU執行對應的指令了。

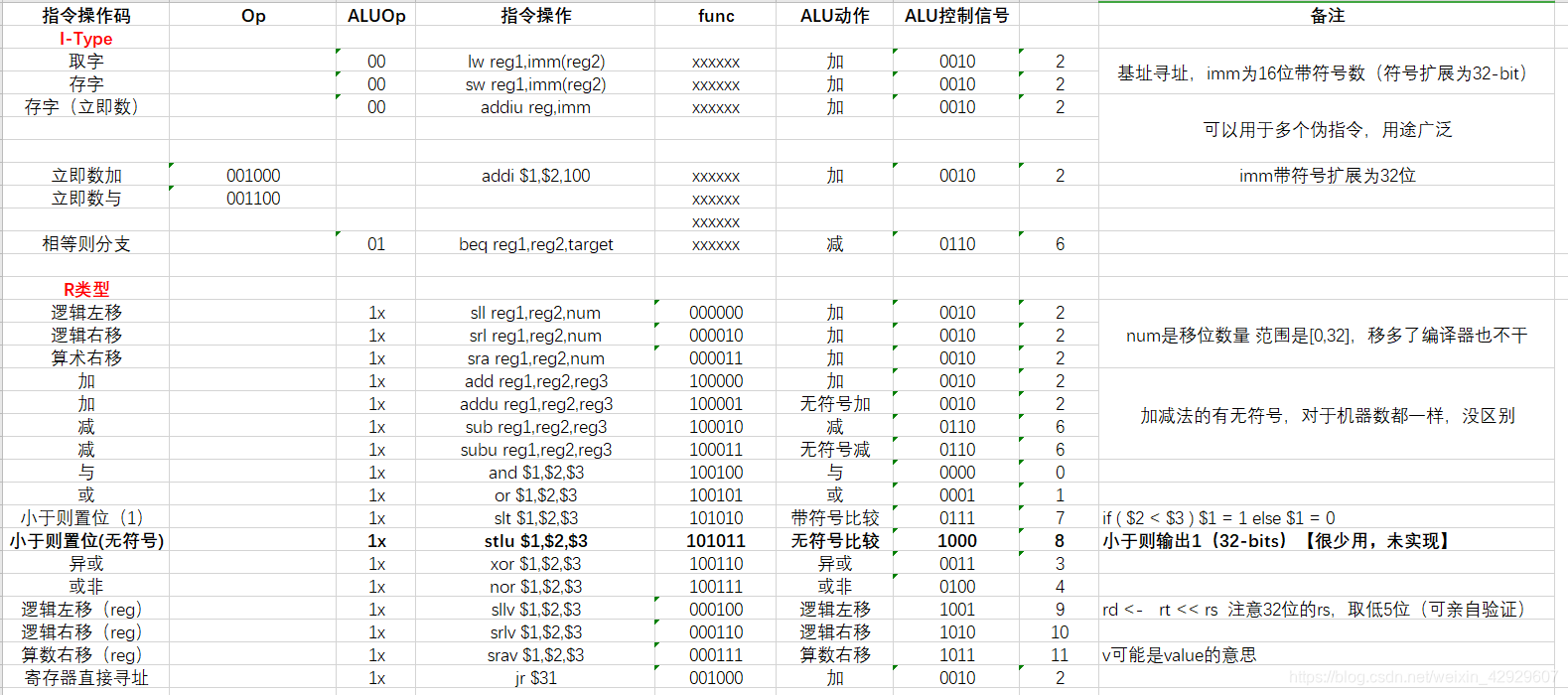

我們可以使用Excel表格來記錄,這很方便,并且很清晰,例如:

具體CPU的設計,你可以在開頭提及的MOOC的CPU設計的章節進行學習。

3.3 Implement our design: A Minimum System

讓我們先來實現一個最小的,最簡單的CPU,并且驗證它的正確性,之后我們可以根據成功的經驗,來實現更多的指令了。

完成了CPU的邏輯設計,我們就可以按照邏輯設計進行實現了,對于組合邏輯我們完全可以使用自動生成電路功能來完成它,沒有必要手動完成。

看示例:

這是一個極簡功能的CPU,甚至可能,它的設計是有些問題的,但是不妨礙我們真的實現了一個CPU,你可以參考它完成自己的CPU。

注意:我們前面提到的ROM器件中特別強調了地址是4的整數倍的問題,這里的設計有問題,在branch指令中并沒有移位就直接加了PC,請讀者自行學習改進。

3.4 Verify our design using MARS MIPS simulator

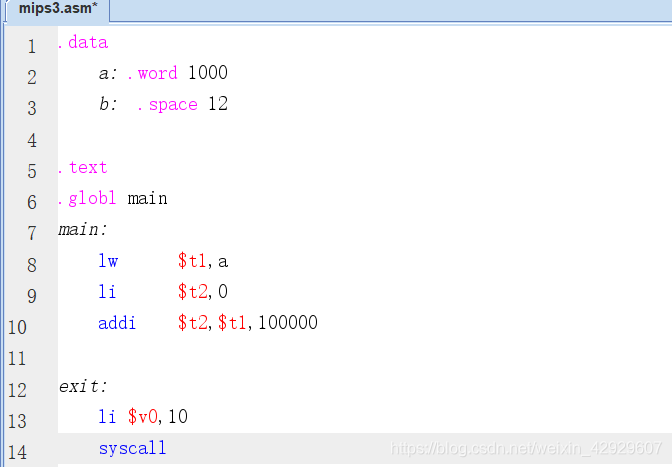

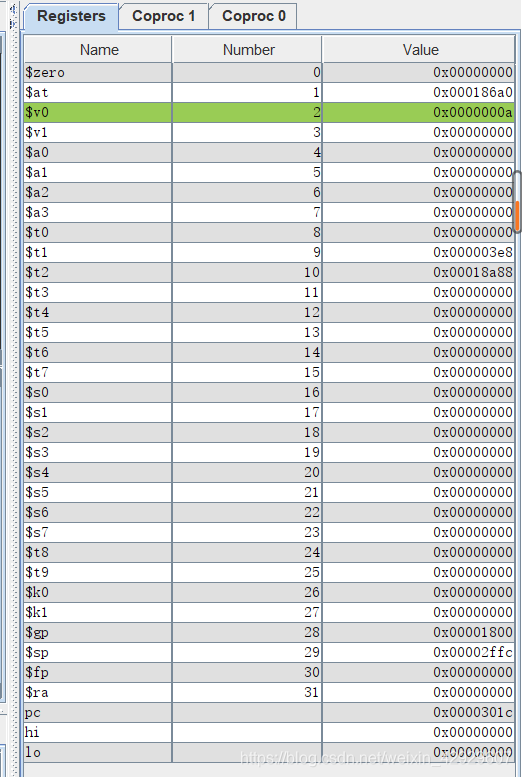

現在,我們設計了一個簡單的CPU,現在需要驗證正確性了,我們需要使用MARS模擬器,編輯一些簡單的MIPS指令。

然后我們將其編譯,運行

這樣,我們就可以獲得寄存器堆和數據存儲器的值了。

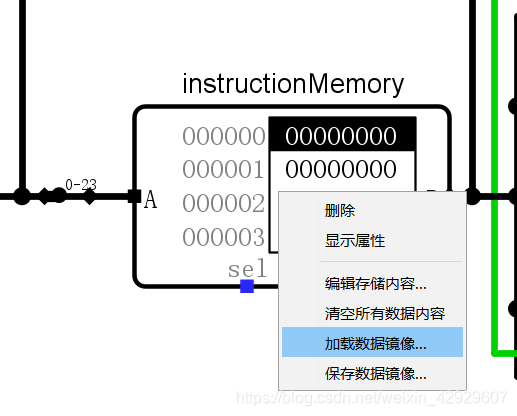

之后我們將指令導出,加載到我們剛剛設計的CPU的存儲器中去,執行指令,看看結果與MARS的結果是否一致,如果一致,就設計正確,不一樣就依次查找,找到出錯的信息,然后糾正它。

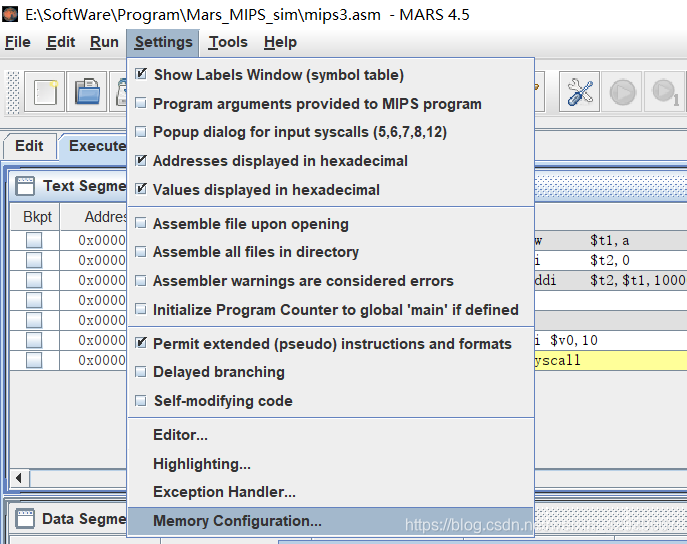

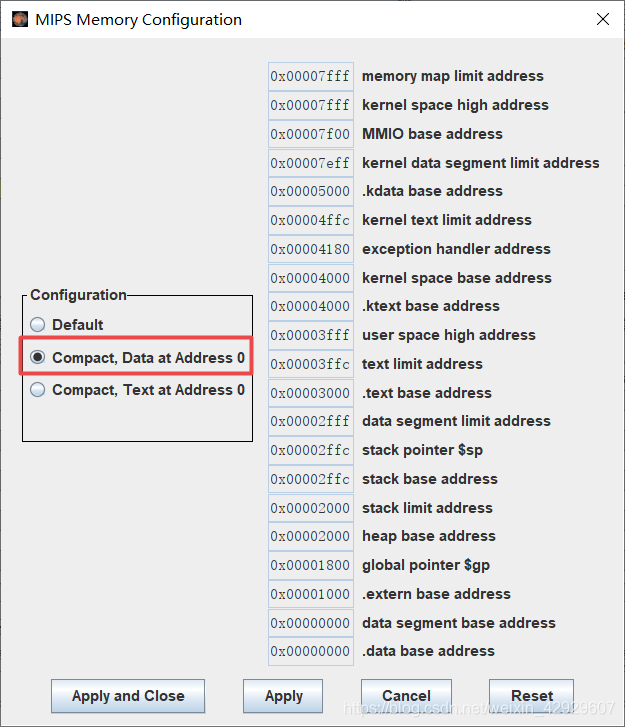

在導出之前,我們需要設置一下MARS,將其數據段地址從0開始。

然后,我們就可以導出了

可以分別導出.text和.data,以十六進制形式,然后加載到我們的Logsim指令存儲器和數據存儲器中去。

右鍵單擊,選擇加載即可。

4 Surprise

好吧,我想現在還沒有驚喜……后續我會將一些可參考的CPU上傳,這樣大家就可以參考學習了。

)

)

)

:FIFO(先進先出)算法 原理與實踐)

:SJF(短任務優先) 算法 原理與實踐)

:STCF(最短完成時間優先) 算法 原理與實踐)

:RR(輪轉) 算法 原理與實踐)

:I/O、不可預測的運行時間)

)

03,04)