基本分段存儲管理

與分頁最大的區別:離散分配時所分配地址空間的基本單位不同

進程的地址空間:按照程序自身的邏輯關系劃分為若干個段,每個段都有一個段名,每段從0開始編址

內存分配規則:以段位單位進行分配,每個段再內存中占連續空間,但各段之間可以不相鄰。由于時按照邏輯功能劃分,用戶編程更方便,程序可讀性更高。

編譯程序會將段名轉換為段號

分段系統的邏輯地址由段號和段內地址(段內偏移量)組成

段號的位數決定了每個進程最多可以分多少個段,段內地址位數決定了每個段的最大長度是多少

段表:記錄各個邏輯段在內存中存放的地址

每個段表由三部分組成:段號+段長+基址

段號可以隱藏,假設段號16位,段內地址16位,32位操作系統,按字節尋址,則每個段表項的長度為16+32=6B。如果段表存放的起始地址為M,則第k號段的地址為M+6*k

段表寄存器:存放在PCB中,當進程將要運行的時候會恢復。保存段表始址F和段表長度M

- 根據邏輯地址得到段號S、段內地址W

- 比較段號和段表長度,如果超過產生越界中斷

- 查詢段號對應的段表項:F+S*段表項長度得到段基址b

- 檢查段內地址W和段長C,如果超過產生越界中斷(與分頁管理不同)

- 根據段基址b+段內地址W

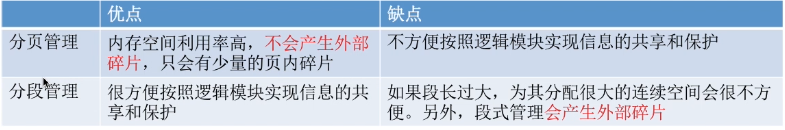

分段、分頁管理的對比:

- 頁是信息的物理單位,分頁的主要目的是為了離散分配,提高內存利用率。分頁僅僅是系統管理上的需要,完全是系統行為,對用戶是不可見的。

- 段是信息的邏輯單位,分段的主要目的是為了更好地滿足用戶需求,一個段同行包含著一組數以億個邏輯模塊的信息,分段對用戶是可見的,用戶編程時需要顯式地給出段名

- 頁的大小固定且由系統決定,段的長度不固定,決定于用戶編寫的程序

- 分頁的用戶進程地址空間是一維的,程序員只需要給出一個記憶符就可以表示一個地址

- 分段的用戶進程地址空間是二維的,程序員在標識一個地址時,既要給出段名,又要給出段內地址。

- 分段比分頁更容易實現信息的共享和保護。不能被修改的代碼稱為純代碼或可重入代碼(不屬于臨界資源 ),這樣的代碼是可以共享的。可修改的代碼是不能共享的(比如一個代碼段中有很多變量,各個進程并發地同時訪問可能造成數據的不一致)。頁面因為不是按照邏輯模塊劃分的,這就很難實現共享。

- 分頁(普通)需要兩次訪存,分段也需要兩次訪存。分段存儲同樣也可以引入快表機構

段頁式管理

分段管理產生外部碎片的原理和動態內存管理產生外部碎片的原理相同,因此同樣也可以通過緊湊技術,但是緊湊技術需要較大的時間代價。

分段管理產生外部碎片的原理和動態內存管理產生外部碎片的原理相同,因此同樣也可以通過緊湊技術,但是緊湊技術需要較大的時間代價。

將進程按邏輯模塊分段,再將各段分頁

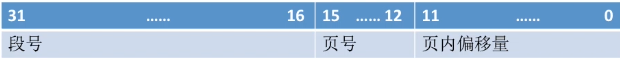

段頁式系統的邏輯地址:段號、頁號、頁內地址(頁內偏移量)組成

段號的位數決定了每個進程最多可以分幾個段

頁號位數決定了每個段最大有多少頁

頁內偏移量決定了頁面大小、內存塊大小

分段對用戶是可見的,程序員編程時需要顯式地給出段號、段內地址。而將各段分頁對用戶是不可見的。系統會根據段內地址自動劃分頁號和頁內偏移量。因此段頁式管理的地址結構是二維的。

每一個段對應一個段表項,每個段表項由段號、頁表長度、頁表存放塊號(即就是頁表起始地址)組成。每個段表項長度相等,段號是隱藏的。相當于每一個段表項都是一個PTR(頁表寄存器)

這里的段表不同于分段管理中的段表(段號(隱藏)+段長度+段基址)

每一個頁面對應一個頁表項,每個頁表項由頁號、頁面存放的內存塊號組成(頁號隱藏)

邏輯地址轉換為物理地址

PCB中包含段表寄存器:段表始址F + 段表長度M

- 根據邏輯地址得到段號S,頁號P,頁內偏移量W

- 判斷段號是否合法,若S>=M則產生越界中斷

- 查詢段表,找到對應的段表項,段表項存放地址為F+S*段表項長度

- 判斷頁表長度和頁號,如果頁號>=頁表長度則產生越界中斷

- 查詢頁表項=頁表起始地址+頁號*頁表項長度

- 根據頁表項得到的內存塊號*內存大小+頁內偏移量W得到物理地址

三次訪存:訪問段表->訪問頁表->訪問物理地址

可以引入段表機制,用段號和頁號作為查詢的關鍵字,則只需要一次訪存