注:本文翻譯自Constraining Logically Exclusive Clocks in Synthesis

邏輯互斥時鐘的定義

邏輯互斥時鐘是指設計中活躍(activate)但不彼此影響的時鐘。常見的情況是,兩個時鐘作為一個多路選擇器的輸入,并根據sel信號決定哪一個時鐘被激活。一個處理邏輯互斥時鐘的重要指導思想就是邏輯互斥時鐘不應該在mux以外的地方發生交互。

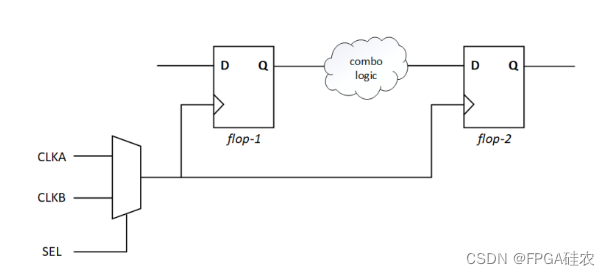

如上圖所示,設計中共有兩個時鐘,分別是CLKA和CLKB,兩個時鐘是多路選擇的,某一時刻,只有一個時鐘對電路起作用。一種約束的方法是使用set_case_analysis約束,即假定SEL恒為0或者1,然后進行時序分析。否則,若不進行任何約束,則flop-1和flop-2的發起時鐘和捕獲時鐘分別有兩種可能,因而綜合工具總共會分析四條路徑,如下表所示:

| flop-1發起時鐘 | flop-2捕獲時鐘 |

|---|---|

| CLKA | CLKA |

| CLKB | CLKA |

| CLKA | CLKB |

| CLKB | CLKB |

然而,事實上,表中中間的兩種情況永遠不可能發生。因此,為了杜絕這一問題,我們可以采用下面所示的約束方式:

set_clock_groups -logically_exclusive -group CLKA -group CLKB

通過上述約束,綜合工具只會分析CLKA–>CLKA和CLKB–>CLKB這兩條路徑。

事實上,我們也可以通過設置偽路徑來實現:

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB]

set_false_path -from [get_clocks CLKB] -to [get_clocks CLKA]

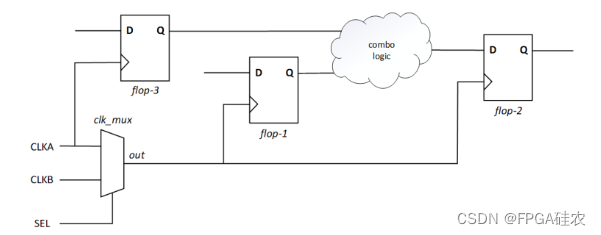

現在考慮另一種情況,如上圖所示,CLKA直接驅動了flop-3,因此,如果我們仍然采用set_clock_groups -logically_exclusive -group CLKA -group CLKB約束,那么綜合工具只會分析CLKA–>CLKA和CLKB–>CLKB之間的路徑,而事實上,flop-3和flop-2之間可能存在CLKA–>CLKB這種情況。

因此,為了解決上述問題,我們需要為CLKA和CLKB創建生成時鐘,如下所示:

create_generated_clock -name -CLKA_GEN -source CLKA [get_pins clk_mux/out]

create_generated_clock -name -CLKB_GEN -source CLKB [get_pins clk_mux/out]

然后,我們設置生成時鐘之間是邏輯互斥的:

set_clock_groups -logically_exclusive -group CLKA_GEN -group CLKB_GEN

經此約束后,原先遺漏的路徑CLKA(flop-3)–>CLKB(flop-2)也會被綜合工具分析了。

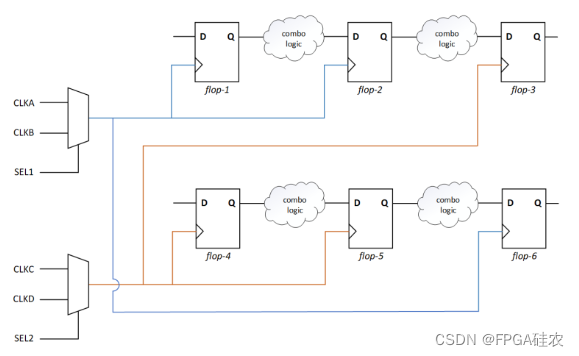

考慮上圖所示的情況,由圖可知,CLKA和CLKB被信號SEL1 MUX,CLKC和CLKD被信號SEL2 MUX,flop-1和flop-2以及flop-6被CLKA和CLKB MUX后的時鐘驅動,而flop-4、flop-5以及flop-3被CLKC和CLKD MUX后的時鐘驅動。

為了對上述設計進行約束,我們有:

set_clock_groups -logically_exclusive -group CLKA -group CLKB

set_clock_groups -logically_exclusive -group CLKC -group CLKD

我們也可以通過設置偽路徑實現上述效果:

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB]

set_false_path -from [get_clocks CLKB] -to [get_clocks CLKA]

set_false_path -from [get_clocks CLKC] -to [get_clocks CLKD]

set_false_path -from [get_clocks CLKD] -to [get_clocks CLKC]

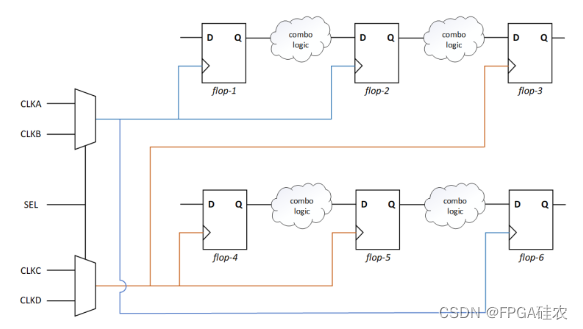

我們在上述例子的情況再作了一些改變,即兩個MUX的SEL信號是相同的,此時CLKA和CLKB以及CLKD不能交互,CLKC也不能和CLKD以及CLKB交互,因此,我們可以做如下約束:

set_clock_groups -logically_exclusive -group “CLKA CLKC” -group “CLKB CLKD”

上述約束中,同一組內的時鐘可以交互,而不同組間的時鐘不能交互,其效果正是我們想達到的。

)

)

利用有限制通配符來提升 API 的靈活性)

VOC劃分數據集、VOC轉YOLO數據集)

)

)