Timing Borrow技術又稱為cycle stealing技術,主要是利用latch的電平敏感特性,通過有效電平獲取數據,通過無效電平保持被鎖存的數據,主要用于解決路徑時序不滿足電路要求的情況。

通過TimingBorrow可以對電路進行加速,當路徑延遲較大時,可以通過借用latch的部分時間實現數據的鎖存從而可以提高設計運行的頻率。采用TimingBorrow設計時,一定要注意前級電路借用時間與后級電路剩余時間之間的關系,某些情況下,timing borrow的錯誤理解會對綜合和后端實現產生嚴重的時序問題,需要正確理解和規范使用。

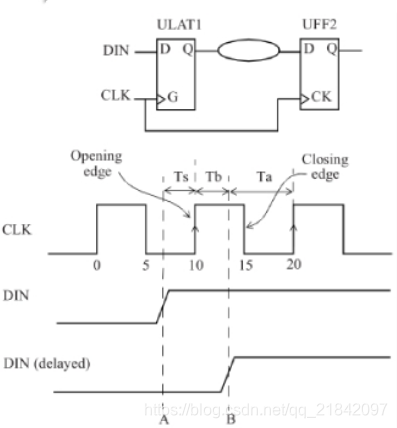

我們先從鎖存器說起:在一個鎖存器中,時鐘的一個沿之后,會使得鎖存器變得透明(即這個時鐘沿打開了鎖存器,使得鎖存器的輸出與數據輸入相同),我們把這個沿叫做opening edge;時鐘的另一個沿之后,會關閉鎖存器(即這個時候數據輸入即使有任何變化,鎖存器輸出也不會改變),我們把這個沿叫做closing edge。

一般來說,鎖存器的輸入數據應該在時鐘有效沿之前準備好,但是由于鎖存器在時鐘有效電平時是透明的,因此,數據能在時鐘有效沿之后到達,可以向下個時鐘周期“借時間”(borrow time)。需要注意的是,一旦“借時間”,用于后級電路的時間會減少。

以上圖為例,如果輸入數據在B時刻到達,那么相當于向下一個時鐘借了Tb時間。但是,這樣減少了鎖存器到下一個寄存器UFF2的時間,時間只剩下了Ta。

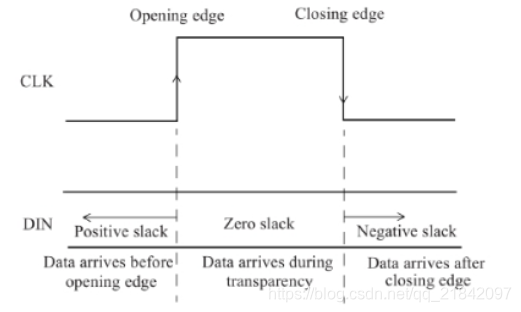

- 如果數據在鎖存器的opening edge之前到達,那么其行為與寄存器類似。opening edge會捕獲數據并且opening edge作為下一時序路徑的起點將數據傳輸出去。

- 如果數據在opening edge與closing edge之間(鎖存器透明)到達,那么會產生timing borrow。借出的時間會決定下一時序路徑的起點。

對于Timing borrow的情況,我們會依據下圖分為三種:

如果數據在negative slack到達,那么timing borrow技術也失效了,會導致時序違背(violation)。

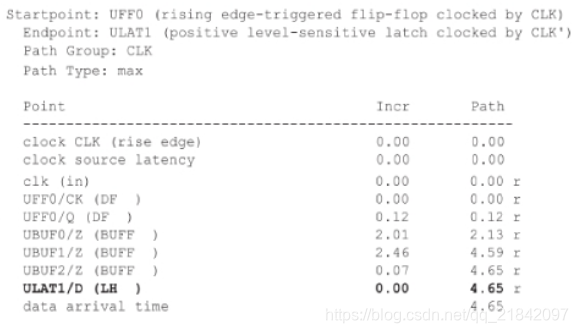

我們來看看在positive slack的時序報告:

? ?

這里我們不需要進行time borrow。

)

)

Hibernate高級配置)

)