- 實驗目的

(1)熟悉Multisim 電路仿真軟件的操作界面和功能;

(2)掌握邏輯電路綜合設計,并采用仿真軟件進行仿真。

- 實驗內容

1.試設計一個簡易CPU功能的數字電路,實驗至少要求采用4個74HC/HCT194作為4個存儲單元(可以預先對存儲單元存儲數據),74HC283作為計算單元。請實現通過第1個時鐘脈沖信號取出存儲單元中的數據1,第2個時鐘脈沖信號取出存儲單元中的數據2,第3個時鐘脈沖信號計算數據1和數據2求和,第四個時鐘脈沖求和數據存回存儲單元。使用用Multisim進行邏輯功能仿真。

一、實驗過程及分析

(一)設計前準備

1.明確每個時鐘脈沖要做哪些事情

第1個時鐘脈沖信號取出存儲單元中的數據1,第2個時鐘脈沖信號取出存儲單元中的數據2,第3個時鐘脈沖信號計算數據1和數據2求和,第4個時鐘脈沖求和數據存回存儲單元。

注:Multisim仿真實驗中的時鐘脈沖頻率怎么調

(1)打開Multisim軟件,創建一個新的電路設計。

(2)從元器件庫中選擇時鐘脈沖元件,并將其拖入電路圖中。

(3)右鍵單擊時鐘脈沖元件,選擇“屬性”命令,打開元件屬性對話框。

(4)在屬性對話框中,找到“頻率”選項,將其值修改為所需的頻率。例如,若原頻率為1kHz,調慢為 100Hz,則將頻率值改為0.1kHz(即100Hz)。需要注意的是,Multisim中時鐘脈沖的頻率單位是赫茲(Hz)。

2.了解設計所需要的核心元件

(1)74HC194:

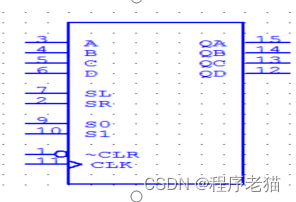

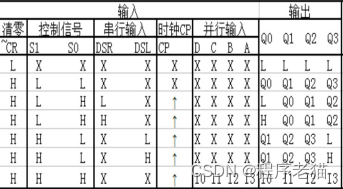

| 如圖 DSR端是右移串行數據輸入端,DSL是左移串行數據輸入端~CLR 為異步清零輸入端。下表3為74HC194的功能表,表中第一行表示寄存器異步清零操作;第二行為保持狀態; 第三、四行為串行數據右移操作;第五、六行為串行數據的左移操作;第七行為并行數據同步置數操作。

| 74HC194是一個4位雙向移位寄存器,具有以下主要功能: MR:數據清零端,低電平有效。 D0~D3:并行數據輸入端。 Q0~Q3:并行數據輸出端。 SR:右移串行數據輸入端。 SL:左移串行數據輸入端。 S0和S1:運行方式控制。S0=S1=1時,數據并行輸入;S1=0,S0=1時,數據右移輸入;S1=1,S0=0時,數據左移輸入;S1=S0=0時,寄存器處于保持狀態。 CLK:時鐘脈沖輸入端,上升沿有效1 2。 使用方法: 將MR置高電平,選擇控制方式。 若選擇并行輸入,則將S0和S1置1,給D3到D0數據,并使CP接收到一個上升沿,數據將被寫入輸出端Q3到Q0。 若選擇串行左移輸入,則將S0設為0,S1設為1,給SR數據a,CP輸出一個上升沿,數據a將被寫入D0;接著給SR數據b,CP輸出一個上升沿,數據b將被寫入D0,并依次移位。 若需要取消輸出數據,可以使用MR置0的方式。 |

(2)74HC283:

| A3A2A1A0:四位二進制加數。B3B2B1B0:四位二進制加數。S3S2S1S0:和數。C-1:低位來的給A0的進位信號。C0:A3B3向高位的進位信號。 |

python門面模式)

)