面向5G/6G科研應用

USRP專門用于5G/6G產品的原型開發與驗證。該系統可以在實驗室搭建一個真實的5G 網絡,基于開源的代碼,專為科研用戶設計。

軟件無線電架構,構建真實5G移動通信系統

X410 采用了目前流行的異構式系統,融合了FPGA、ARM、GPU和x86多種處理器,支持單獨升級和擴展,為算法評估提供強大算力支持。

高性能與靈活性的完美平衡

支持流行的開源5G項目,也可以運行商業5G協議棧,可用于搭建工業5G專網,實現云化管理。L1/L2/L3都可以二次編程,能支持FPGA級別的硬件編程和開發,充分發揮開發人員的主動性和創造力。

真正可編程移動通信系統

支持5G FR1頻段,可以通過擴展組件,支持FR2(毫米波)頻段,適用于6G平臺開發,同時也兼容2G/3G/4G通信系統。如果需要覆蓋距離元,也可以配合外部功放模塊。

硬件平臺

可編程射頻單元 X410

NI Ettus USRP X410 是一款高性能、多通道軟件定義無線電。 SDR 設計用于 1 MHz 至 7.2 GHz 的頻率,可調至 8 GHz,采用兩級超外差架構,具有 4 個獨立的 TX 和 RX 通道,每個通道的瞬時帶寬為 400 MHz。 用于數據卸載和控制的數字接口包括兩個支持 100 GbE 的 QSFP28 接口、一個 PCIe Gen3 x8 [1] 接口以及標準命令、控制和調試接口:USB-C JTAG、USB-C 控制臺、以太網 10/100 /1000。 USRP X410 是一款基于 Xilinx Zynq Ultrascale+ ZU28DR 射頻片上系統 (RFSoC) 構建的一體化器件,具有內置數字上下轉換和板載軟決策前向糾錯 (SD-FEC) IP。

使用您選擇的軟件

NI Ettus USRP X410 完全支持流行的開源 USRP 硬件驅動程序 (UHD) 版本 4.1 或更高版本[2]。 UHD 4.1 旨在支持 400 MHz 帶寬和板載多個通道所帶來的大數據移動要求。 USRP X410 支持開源 SDR 設計流程,例如 C/C++ 和 GNU Radio 以及 LabVIEW FPGA [1]。 與其他基于 RFSoC 的系統不同,USRP X410 已完全準備好移植您以前的 UHD 設計,以便通過簡單的重新編譯來利用高性能功能。

聯網/單機運行

由于 USRP X410 基于 ZU28DR 射頻片上系統 (RFSoC) 器件構建,因此它配備了四核 ARM Cortex-A53 處理子系統,主頻高達 1.2 GHz,可滿足獨立應用要求。 此外,RFSoC 還包含一個雙核 ARM Cortex-R5 實時處理單元,用于板載監控。

內置IP

USRP X410 上的板載 RFSoC 包含的 FPGA 可編程邏輯資源是上一代 X 系列 USRP 器件的兩倍多。 此外,ZU28DR還配備8個軟判決前向糾錯(SD-FEC)硬IP核,非常適合無線通信系統。 鑒于 RFSoC 內置 ADC 和 DAC 的高速特性,Zynq 器件具有 8 個數字上變頻和數字下變頻 IP 內核,可實現快速帶內重新調諧或信號減弱。

多電臺同步

通過內置 GPSDO(GPS 規范振蕩器)或 10 MHz 參考和 1 PPS(每秒脈沖)輸入信號接口,可以實現多無線電時鐘和定時同步操作。 不支持多無線電相位對齊和相位相干操作,因為 USRP X410 不支持 RF 鏈 LO 導入和導出功能。

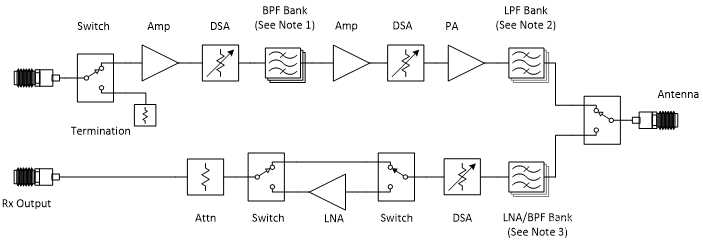

5G NR 信號調理模塊

SC2430 NR 信號調理模塊 (SCM) 是一款前端解決方案,可為軟件定義無線電 (SDR) 系統提供信號調理和放大。它專為與 NI Ettus-USRP X410 結合使用而設計。在此配置中,其輸入和輸出無線電特性符合 5G NR 用戶設備 (UE) 和 gNodeB (gNB) 實施的精選 3GPP 5G/NR 標準。

典型應用

- 5G NR FR1 開發

- 軟件定義無線電應用

- 先進無線通信研究

- 大批量生產測試和測量

SC2430 SCM 包含兩個前端 (FE) 模塊。每個模塊在時分雙工 (TDD) 配置中包含兩對獨立的發送 (Tx) 和接收 (Rx) 通道。對于需要頻分雙工 (FDD) 操作的應用,可以將一個無線電通道配置為連續發送路徑,將第二個無線電通道配置為連續接收路徑。

綜上所述,SC2430可以同時支持4個TDD或2個FDD通道。

這些通道在 Tx 和 Rx 路徑中包含信號調理和放大模塊,與多個 5G NR 頻段(n34、n38、n39、n40、n41、n46、n47、n48、n77、n78、n79、n90 和 n96 )。此外,旁路路徑可用于在這些頻段之外運行的應用程序。

通過 8 個 SMA 連接器建立與 SDR 的射頻連接。Tx 和 Rx 端口采用交流耦合,支持 350 MHz 至 7.125 GHz 范圍內的信號。這些通道提供 100 MHz(350 MHz 至 600 MHz)、200 MHz(600 MHz 至 800 MHz)和 400 MHz(800 MHz 至 7.125 GHz)的瞬時帶寬 (IBW)。

傳輸路徑可在 1.9 GHz 下產生 34 dB 增益,在 3.5 GHz 下產生 30 dB 增益。峰值輸出功率 (P1dB) 約為 27 dBm,三階截取點 (OIP3) 為 41 dBm。在最大增益下,所有頻率下的噪聲系數通常為 8 dB 或更好。帶通濾波可提供超過 50 dB 的帶外抑制。

在接收路徑中,1.9 GHz 時可獲得 27 dB 增益,3.5 GHz 時可獲得 23 dB 增益。噪聲系數范圍為 4 dB (1.9 GHz) 至 7 dB (3.5 GHz)。輸入三階壓縮點為-5 dBm (1.9 GHz) 至-1 dBm (3.5 GHz)。該裝置可承受最大+10 dBm 的無損壞輸入功率。設計中融入了兩組 5G NR 特定頻帶濾波器,可提供超過 50 dB 的帶外抑制。

控制接口是用戶訪問以配置和編程 SCM 的數字端口。有兩種控制選項可供選擇。

第一個是基于 SPI 的接口,與前面板 HDMI 連接器上提供的其他 GPIO 相結合。SPI 信號存在于引腳 1、4、6、7 和 9 上。其余引腳用于 GND、自動發送/接收或 ATR(引腳 10、12)以及衰減器鎖存(13、15)。提供 ATR 和鎖存引腳是為了促進 5G 規范中定義的高速 TDD 操作。SPI 端口可以在 40 MHz 的寫入頻率和 16 MHz 的讀取時鐘頻率下運行。

NI Ettus-USRP X410 SDR 的用戶可能更喜歡這種控制選項。與其他 USRP 兼容硬件一樣,SC2430 可以設置為 UHD 設備并通過 X410 進行控制。SC2430 驅動程序與 UHD 擴展框架兼容。當啟用 SC2430 擴展時,X410 配置將包括 SCM 性能。例如,設置 X410 增益將導致 X410 和 SCM 增益設置最適合當前操作條件。

標準 HDMI 電纜可用于互連。另外,SCT 還提供短的機械鎖定電纜。這些電纜包含扼流圈以最大限度地減少排放。為每個模塊提供單獨的接口。

第二個控制選項允許用戶通過機箱后部 USB-C 連接器上的 UART 控制臺接口訪問 SC2430。現場固件更新期間需要 USB 端口。

SCT 網站的支持頁面上提供了完整的 API 規范:https://www.signalcraft.com/support。

外部電源輸入需要 12 V DC、16 A 電源。SC2430 附帶通用交流/直流電源塊。如果需要高密度或機架安裝操作,則可以使用其他兼容電源。SC2430 可通過前面板按鈕開機,或設置為在施加 12 伏輸入時自動啟動。前面板按鈕還可用作 SC2430 電源狀態的指示器。

在前面板上,SC2430 每個通道配備一個 LED 來指示其狀態(發送或接收)。

單射頻通道(總共 4 個可用通道)

協議棧開發平臺 超高性能服務器

用于開發5G系統的基站功能,包括物理層和協議棧等。可以預裝開源的OAI參考設計,也支持第三方或者用戶自己開發的協議棧。處理單元采用Intel酷睿i9多核處理器,支持FPGA實現協議棧加速。

高性能

- 應對高性能和關鍵任務系統最多支持 8個Intel? Xeon?處理器7500系列

- 高帶寬和低延時實現了高性能

高可擴展性

- 從1個開始可擴展至 8CPU (64 核心/128線程)

- 最多128個DIMM插槽 (最多2TB內存使用16GB DIMM)

- 最多14個 PCI-Express Gen2插槽

高可靠性

- “無縫架構”, 直接連接CPU,減少部件數量,降低故障率

- 通過冗余部件和在線維護功能(fan, PSU, and HDD)最小化宕機時間

- 內置服務處理器與NEC的BIOS以及Intel的機器校驗架構(MCA)恢復功能配合作用,簡化服務器資源管理

- 通過使用BID快速確定錯誤部分,在UNIX 服務器上最小化恢復時間

節能

- 使用輕型材質,減輕14%重量

- 高效的PSU認證 80 PLUS 金牌認證電源

- 通過使用電力消耗管理最先進技術,降低運行成本

核心網開發平臺 普通性能服務器

開發平臺基于高性能Intel多核處理器,支持萬兆網口與協議開發平臺互聯,預裝開源的5G核心網,提供 AMF、SMF、AUSF、UDM、UPF 等功能單元。平臺支持第三方或者客戶自己的核心網,也可以根據需要,用于邊緣計算或者作為應用服務器實現業務組件集成。

性能

? 支持四顆全系列英特爾 至強 可擴展處理器,單CPU最高支持28個計算核心

? 支持48條DDR4內存,內存速度最高達2666MT/s,內存容量可達6TB

? 智能內存巡檢,內存故障率降低95%

? 支持6個熱插拔存儲設備,支持多種存儲配置模式,可以支持RAID6

? 支持配置4塊PCIe NVMe SSD 盤+2塊M.2硬盤

? 智能硬盤巡檢,故障預警保護數據安全

? 支持8個PCI-E槽位

管理

? 自動監控模塊,實時監控固件信息

? 自動部署模塊,自動發現并納管基礎設施

? 自動生命周期管理模塊,固件/驅動一鍵升級

? 支持OS批量安裝,每臺平均耗時縮短到分鐘級

? 支持錯峰上電功能

? 裸金屬虛擬化,對服務器實現配置采集、鏡像制作、鏡像分發等功能,自動實現服務器裸金屬虛擬化

? 智能日志分析,分析系統日志,智能優先級排序,主動上傳上級運維系統

開源5G項目(Open Air Interface 5G)

隨著第五代通信技術迅速發展,基于5G的應用以及學術研究需求逐漸增大,對于開源5G的研討迫在眉睫。開源5G平臺可用于探索5G領域新技術、新趨勢,對下一代核心網、新型智能終端、mIoT、NB-IoT等領域進行深入學術研究與工程實踐,促進5G的全球化發展。

基于開源5G無線技術和實驗環境的部署,系統原型和標準化硬件實現,可以作為接入網早期測試與驗證工具,支持下一代核心網新型智能終端的研發。

USRP 5G研發平臺預裝開源的5G協議Open Air Interface 5G(OAI),支持新的版本移植和運行。平臺可以為OAI提供穩定運行經過驗證的軟硬件環境,也可以根據需求定制軟件和硬件來滿足科研項目需求。

一般參數

· 靜態時分雙工

· FDD正常CP

· 30 kHz 子載波間隔

· 帶寬高達 80MHz(217 個物理資源塊)

· 與 IF 設備接口的中間下行鏈路和上行鏈路頻率

· 單天線端口(單波束)

· 時隙格式:上行或下行 14 個 OFDM 符號

· 高效的3GPP兼容LDPC編碼器和解碼器(支持BG1和BG2)

· 符合3GPP標準的高效極性編碼器和解碼器

· 短塊的編碼器和解碼器

gNB 物理層

· FR1 為 30KHz SCS,FR2 為 120 KHz SCS

· NR-PSS/NR-SSS的生成

· NR-PBCH支持多個SSB和靈活的周期

· SIB1的NR-PDCCH的生成(包括DCI的生成、極性編碼、加擾、調制、RB映射等)

· MIB配置的公共搜索空間

· RRC配置的用戶特定搜索空間

· DCI格式:00、10(集成中的01和11)

· NR-PDSCH的生成(包括分段、LDPC編碼、速率匹配、加擾、調制、RB映射等)。

· 單符號 DMRS、DMRS-TypeA-Position Pos2、DMRS 配置類型 1

· PDSCH映射類型A

· NR-CSI PHY 序列生成(集成中)

· NR-PUSCH(包括分段、LDPC編碼、速率匹配、加擾、調制、RB映射等)。

· NR-PUCCH

· 格式0(2位,主要用于ACK/NACK)

· 格式2(最高64位,主要用于CSI反饋)

· NR-PRACH 格式 0,1,2,3, A1-A3, B1-B3

· 高效的3GPP兼容LDPC編碼器和解碼器(支持BG1和BG2)

· 符合3GPP標準的高效極性編碼器和解碼器

· 短塊編碼器和解碼器

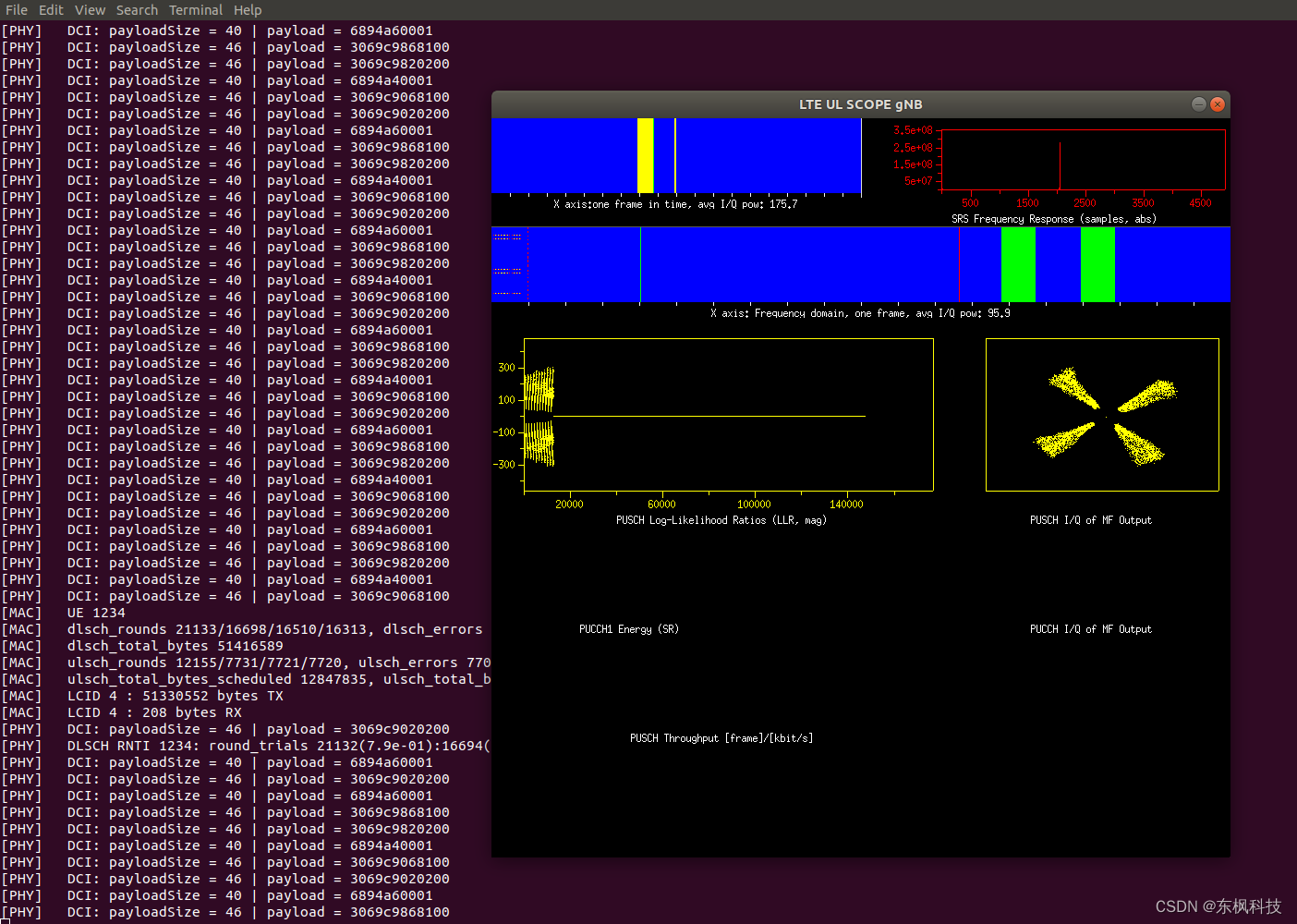

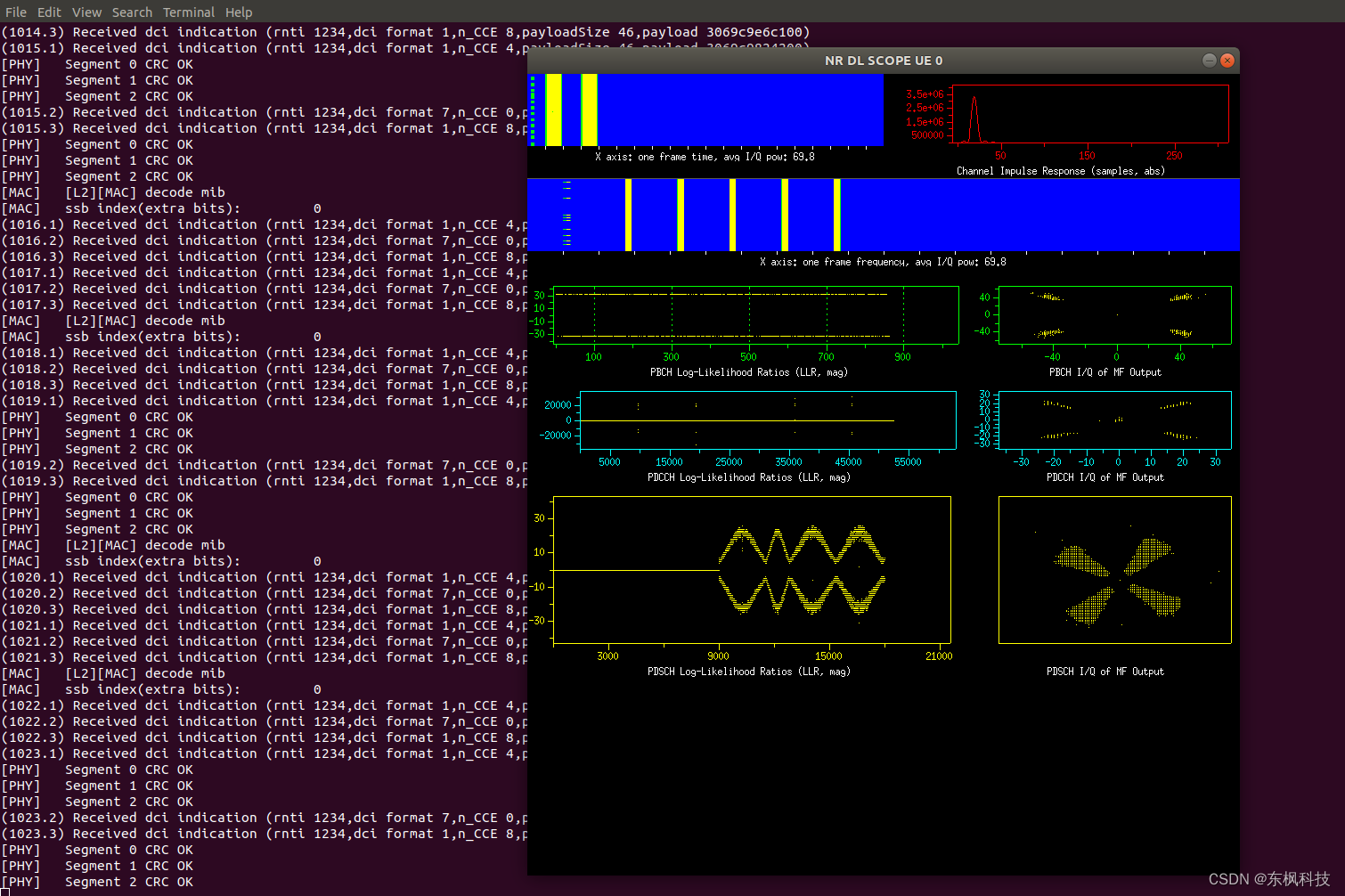

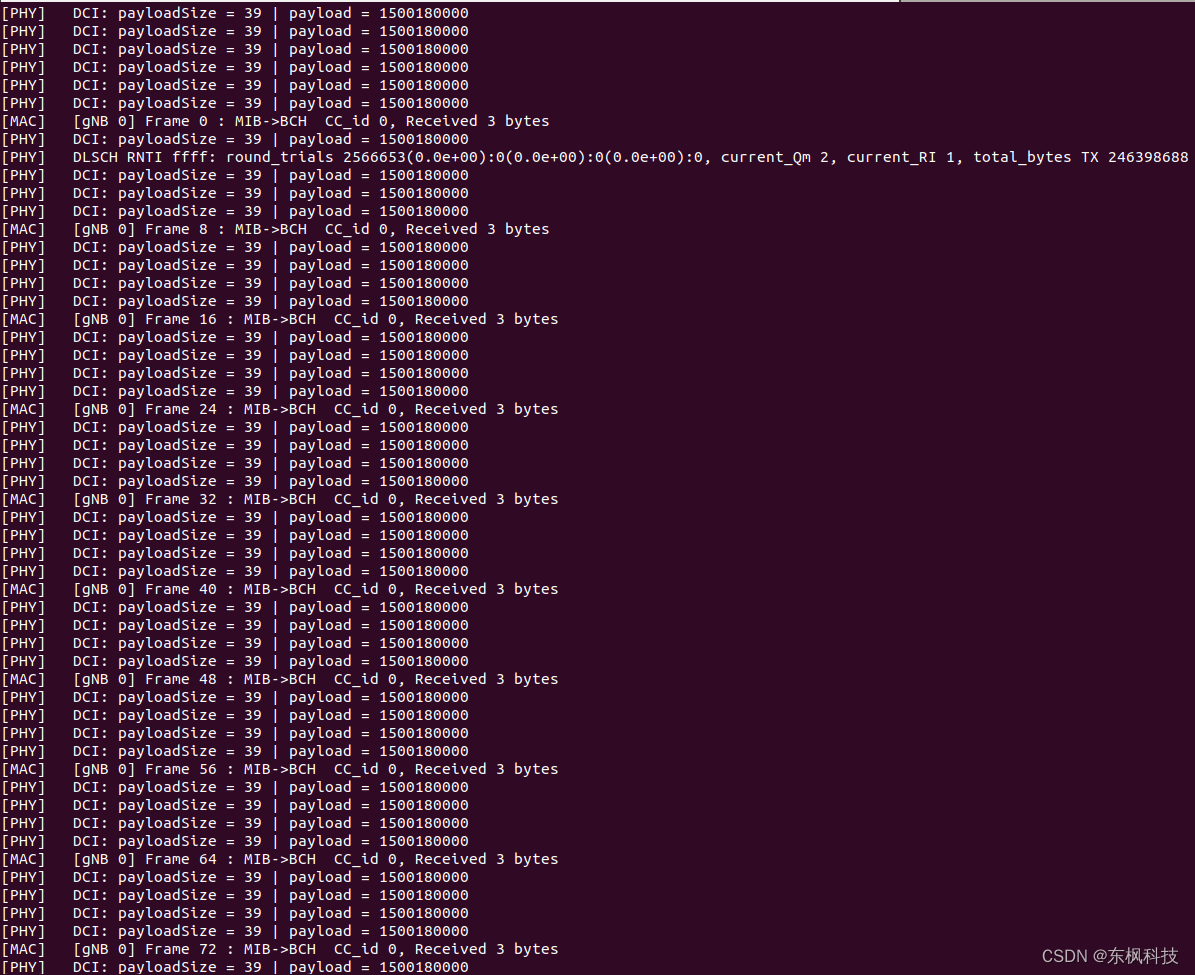

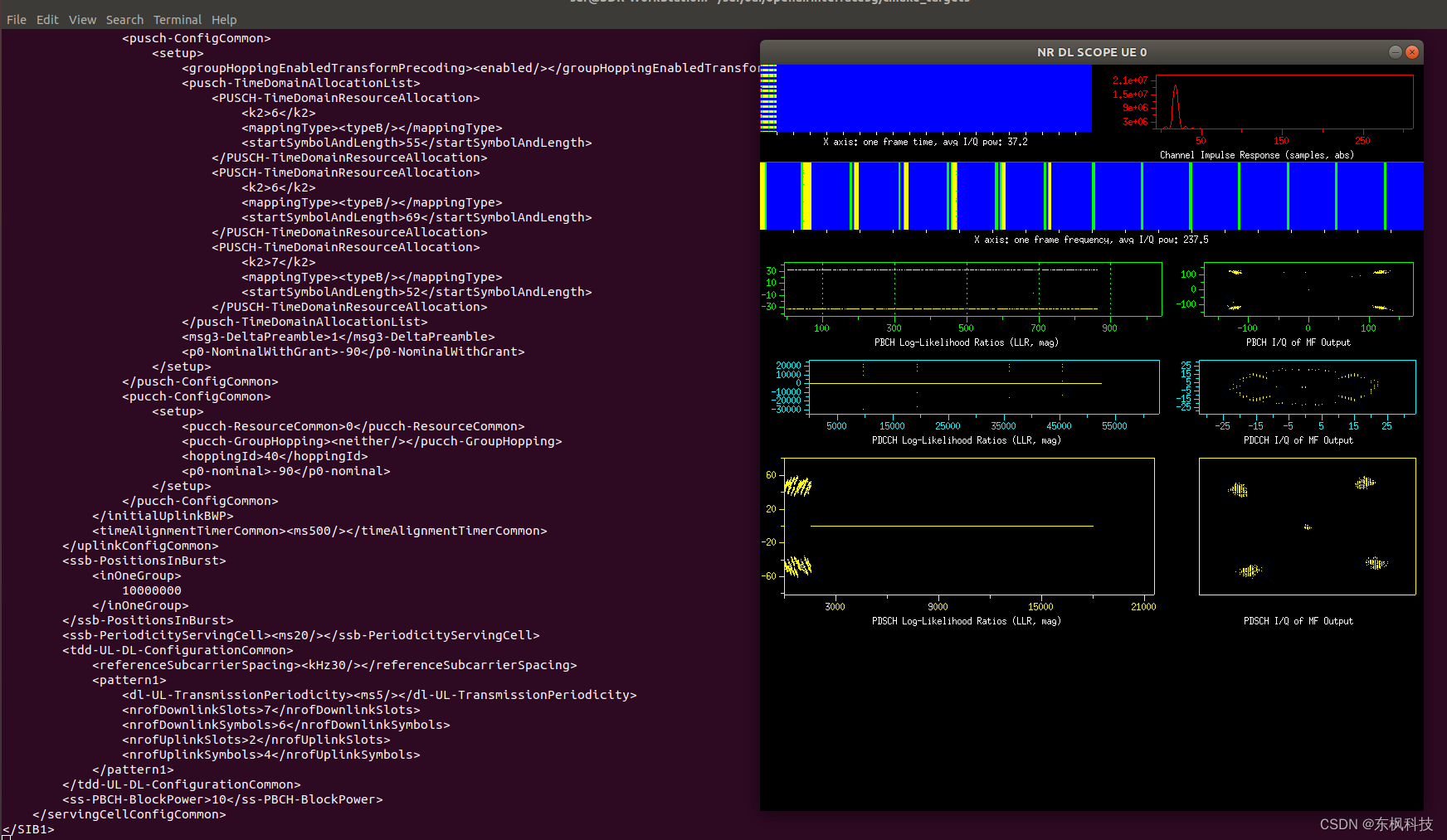

運行效果

5GNR PHY Test–5GNR gNB運行界面

5GNR PHY Test–5GNR UE運行界面

5GNR SA Mode–gNB運行界面

5GNR SA Mode–UE運行界面

頻率查詢表

| NR | Band Frequency |

|---|---|

| n34 | 2010 MHz – 2025 MHz |

| n38 | 2570 MHz – 2620 MHz |

| n39 | 1880 MHz – 1920 MHz |

| n40 | 2300 MHz – 2400 MHz |

| n41 | 2496 MHz – 2690 MHz |

| n46 | 5150 MHz – 5925 MHz |

| n47 | 5855 MHz – 5925 MHz |

| n48 | 3550 MHz – 3700 MHz |

| n77 | 3300 MHz – 4200 MHz |

| n78 | 3300 MHz – 3800 MHz |

| n79 | 4400 MHz – 5000 MHz |

| n90 | 2496 MHz – 2690 MHz |

| n96 | 5925 MHz – 7125 MHz |

Zynq UltraScale+ RFSoC

射頻模擬集成

將直接射頻采樣數據轉換器單片集成到自適應 SoC 上,無需外部數據轉換器,從而實現靈活的解決方案,與多組件解決方案相比,功耗和占用空間減少高達 50%,包括消除高耗電的組件FPGA 至模擬接口,例如 JESD204。這種方法還實現了高度靈活的解決方案,將大部分射頻信號處理轉移到數字域。

標清前向糾錯

Zynq? UltraScale+? RFSoC 集成了具有低密度奇偶校驗檢查 (LDPC) 和 Turbo 編解碼器支持的軟決策前向糾錯核心 (SD-FEC) IP 模塊。與軟邏輯實現相比,硬化核心可在低延遲下提供超過 1Gb/s 的性能,并且功耗更低、面積更小。

硬化數字前端

Zynq RFSoC DFE 是最新的自適應 RFSoC 平臺,它集成了比軟邏輯更多的硬化 IP,用于關鍵的 DFE 處理。Zynq RFSoC DFE 為 5G 新無線電提供靈活的解決方案,輸入/輸出頻率高達 7.125GHz,具有高功效和成本效益。

硬件適應性

Zynq UltraScale+ RFSoC 架構集成了 FPGA 結構,可利用相同的基礎硬件靈活地滿足各種要求。利用同一平臺來滿足不同需求和新興標準的能力使供應商能夠對新的市場機會做出快速反應。

用于單芯片無線電的完整 SoC

作為一種異構計算架構,包括完整的 Arm 處理子系統、FPGA 結構以及整個 RF 信號鏈的完整模擬/數字可編程性,Zynq UltraScale+ RFSoC 為各種應用提供了完整的單芯片軟件定義無線電平臺,并且能夠隨著市場動態的發展產生無線電變體。

Zynq UltraScale+ RFSoC 產品組合

)