目錄

1 中斷控制器

?編輯

2 Exynos4412下的中斷控制器

2.1 概述

2.2 特征

?編輯

2.3 中斷狀態

2.4 中斷類型

2.5 中斷控制器GIC中斷表

3 中斷控制器寄存器詳解

3.1 ICDDCR(Interrupt Controller Distributor Control Register)

3.2?ICDISER_CPU(Interrupt Controller Distributor Set-Enable Register for CPU)

3.3 ICDIPTR_CPU(Interrupt Controller Distributor Interrupt Processor Targets Register for CPU)

3.4 ICCICR_CPUn(Interrupt Controller CPU Interface Control Register for CPU n)

3.5 補充:中斷控制器優先級設置寄存器

4?GPIO中斷編程?

4.1 外設層次設置

4.2 中斷控制器層次設置

4.3 程序代碼

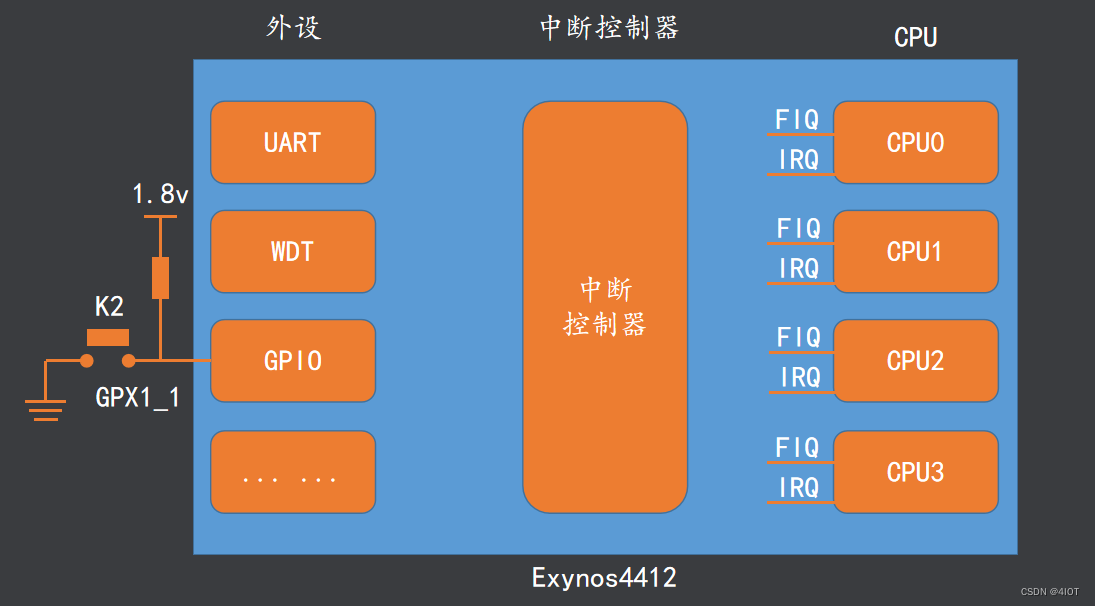

1 中斷控制器

cpu本身是沒辦法區分中斷來自哪個外設,無法應對同時產生的中斷等等許多問題。

三星公司設計了中斷控制器來解決問題

?中斷控制器作用

- 多個中斷同時產生時可對這些中斷掛起排隊,然后按照優先級依次發送給CPU處理 ?

- 可以為每一個中斷分配一個優先級 ?

- 一個中斷正在處理時若又產生其它中斷,可將新的中斷掛起,待CPU空閑時再發送 ?

- 可以為每一個中斷選擇一個CPU處理 ?

- 可以為每一個中斷選擇一個中斷類型(FIQ或IRQ) ?

- CPU接收到中斷信號后并不能區分是哪個外設產生的,此時CPU可查詢中斷控制器來獲取當前的中斷信號是由哪個硬件產生的,然后再進行對應的處理 ?

- 可以打開或禁止每一個中斷 ?... ...

2 Exynos4412下的中斷控制器

中斷控制器內容較多,只進行簡單分析,實際開發很少去配置中斷控制器,因為crotex-A系列處理,一般開發的時候會安裝大型操作系統,操作系統內部會把中斷控制器相關代碼會實現好。包括中斷控制器寄存器的配置等,我們只需要使用中斷函數即可。

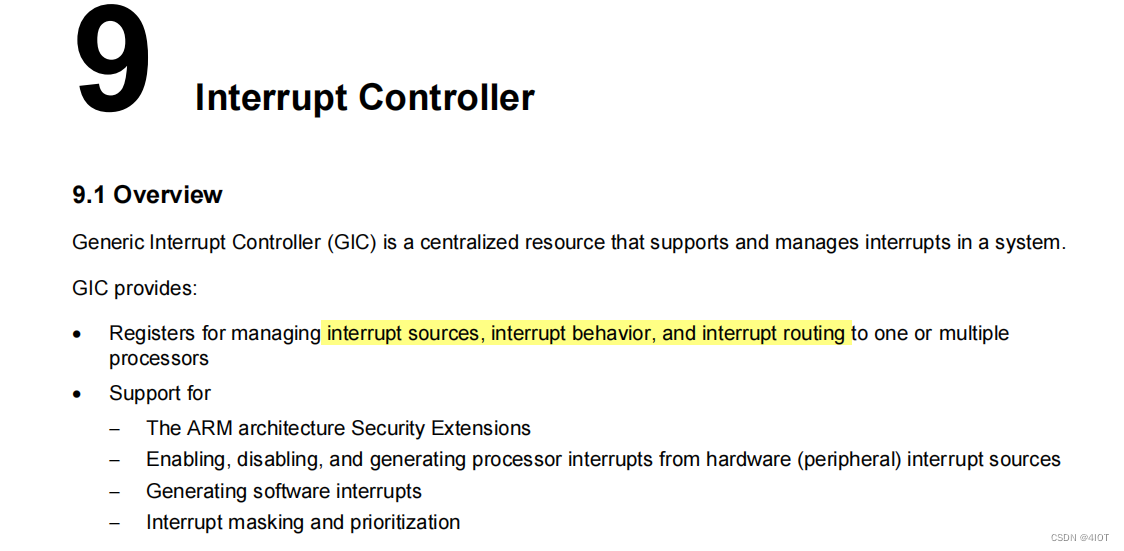

2.1 概述

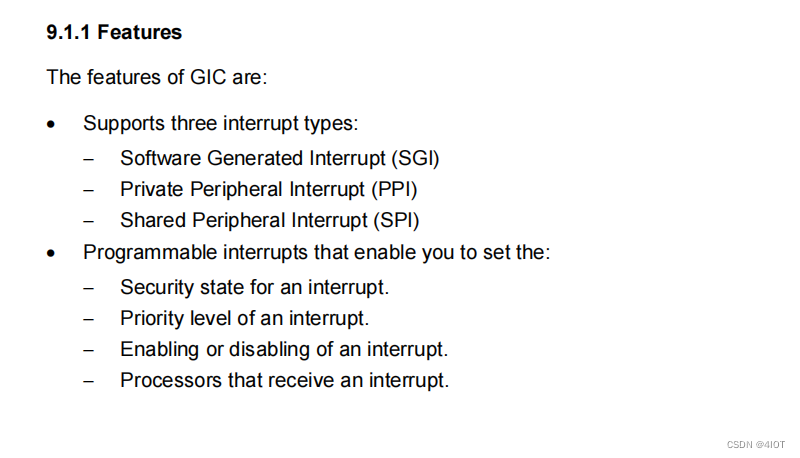

2.2 特征

- 支持三種中斷類型:

- 軟件生成中斷(SGI)(與之前SWI軟中斷指令不是一回事,注意區分)

- 私有外圍中斷(PPI)(只能發送給某一個特定的CPU)

- 共享外圍中斷(SPI)(這類中斷可以發送給任意一個CPU,使用最多)

- 可編程中斷,使您能夠設置:

- 中斷的安全狀態。(安全狀態可以觸發FIQ和IRQ,非安全中斷只能觸發IRQ)

- 中斷的優先級級別。

- 中斷的啟用或禁用。

-

接收中斷的處理器。

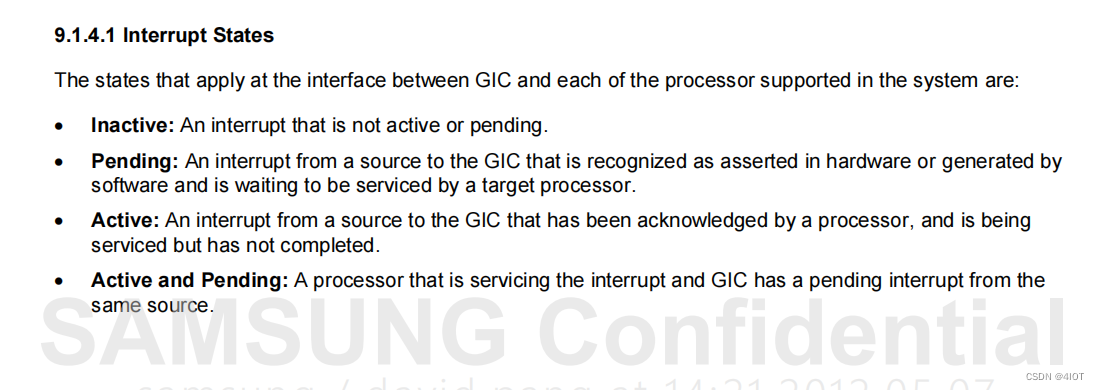

2.3 中斷狀態

2.4 中斷類型

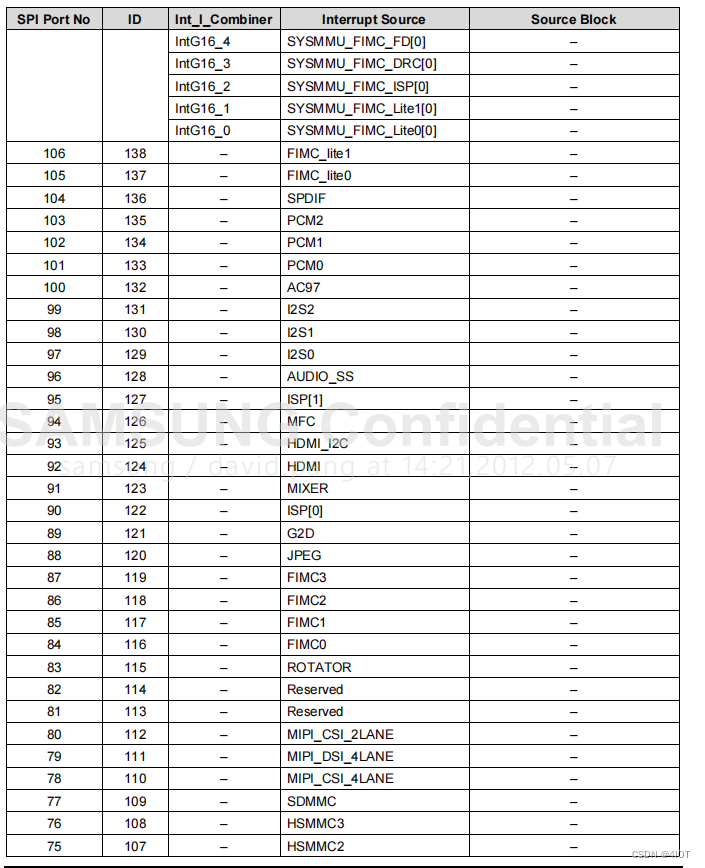

2.5 中斷控制器GIC中斷表

劃分了0~159個中斷號,其中

0~15 SGI 代表了軟中斷,

16~31 PPI只能發送給一個特定的CPU

32~159 SPI 共享中斷

串口 ID 84~87

WDT ID 75

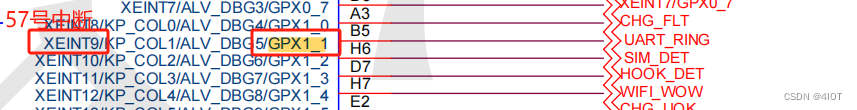

外部中斷,如ID57 代表EINT[9],實驗中使用較多

3 中斷控制器寄存器詳解

寄存器內容從9.5開始介紹

3.1 ICDDCR(Interrupt Controller Distributor Control Register)

中斷控制器分發器控制寄存器(總開關)

全局使能用于監視外設中斷信號并將掛起中斷轉發給CPU接口。

0 = GIC忽略所有外設中斷信號,不將掛起中斷轉發給CPU接口。

1 = GIC監視外設中斷信號,并將掛起中斷轉發給CPU接口。

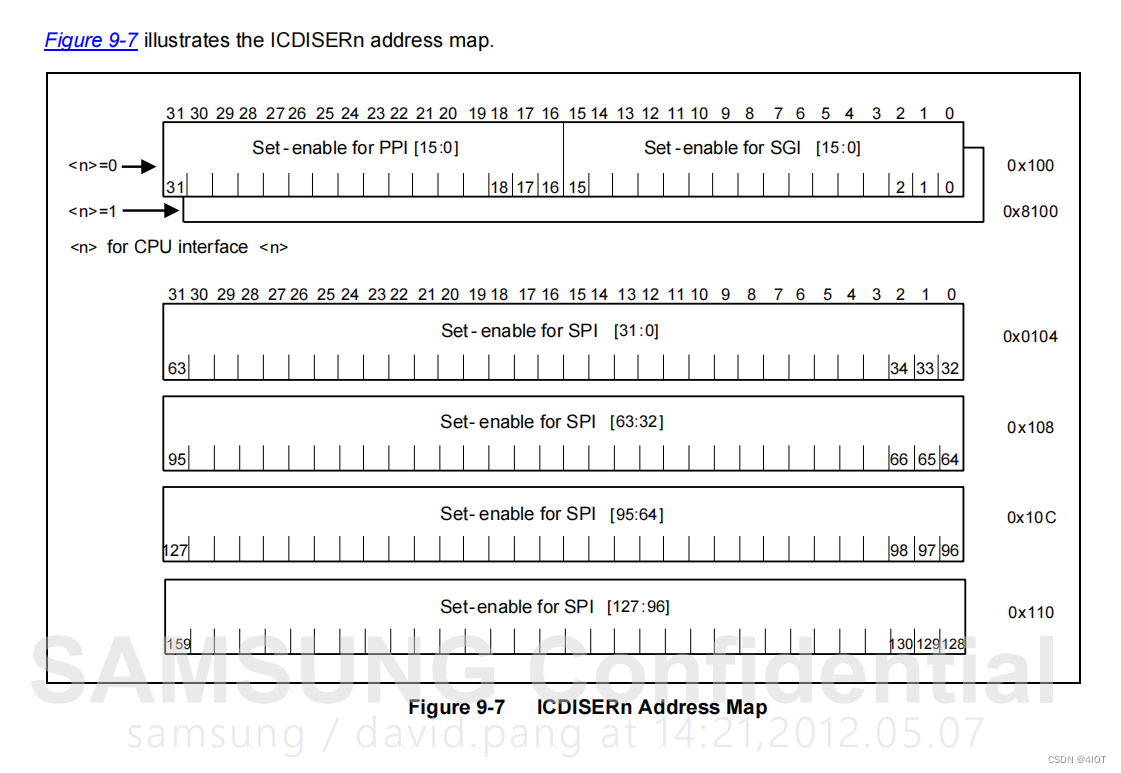

3.2?ICDISER_CPU(Interrupt Controller Distributor Set-Enable Register for CPU)

CPU的中斷控制器分發器設置使能寄存器(小開關)

這個寄存器用于設置每個CPU對應的中斷使能位。通過設置該寄存器的特定位,可以啟用或禁用特定中斷信號的傳遞給相應的CPU核心。具體的寄存器位定義和功能取決于使用的中斷控制器的架構和規范。

?

[31:0] 只有32位,我們總共需要管理160位,所有使用了多個寄存器地址。每個中斷ID對應寄存器參考下表:

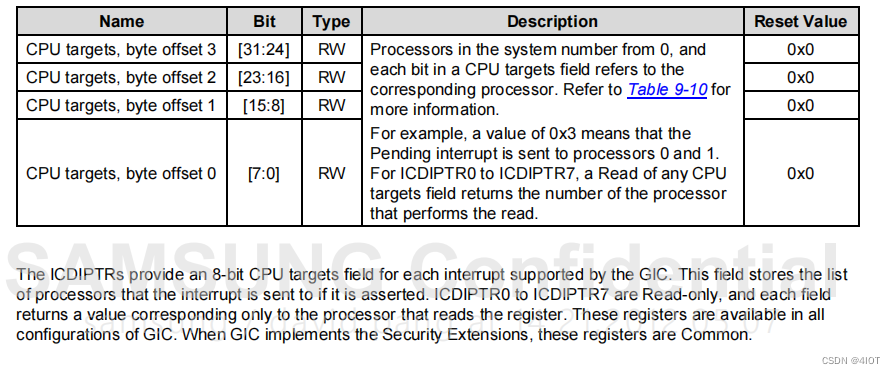

3.3 ICDIPTR_CPU(Interrupt Controller Distributor Interrupt Processor Targets Register for CPU)

即用于CPU的中斷控制器分發器中斷處理器目標寄存器。(選擇CPU)

例如,值為0x3(00000011)表示待處理的中斷將被發送到處理器0和1。對于三星CPU來說高4位無效。

中斷信號需要1280位去管理,160*8bit = 1280bit,一個寄存器只能管理32bit,需要40個寄存器。

對應關系:

例:管理6號中斷,由CPU2來出來

那么寄存器如下圖設置。

3.4 ICCICR_CPUn(Interrupt Controller CPU Interface Control Register for CPU n)

控制指定CPU核心的中斷控制器CPU接口的行為,包括使能和禁用中斷處理、配置FIQ和IRQ中斷的優先級等功能。(中斷控制器到CPU之間的開關)

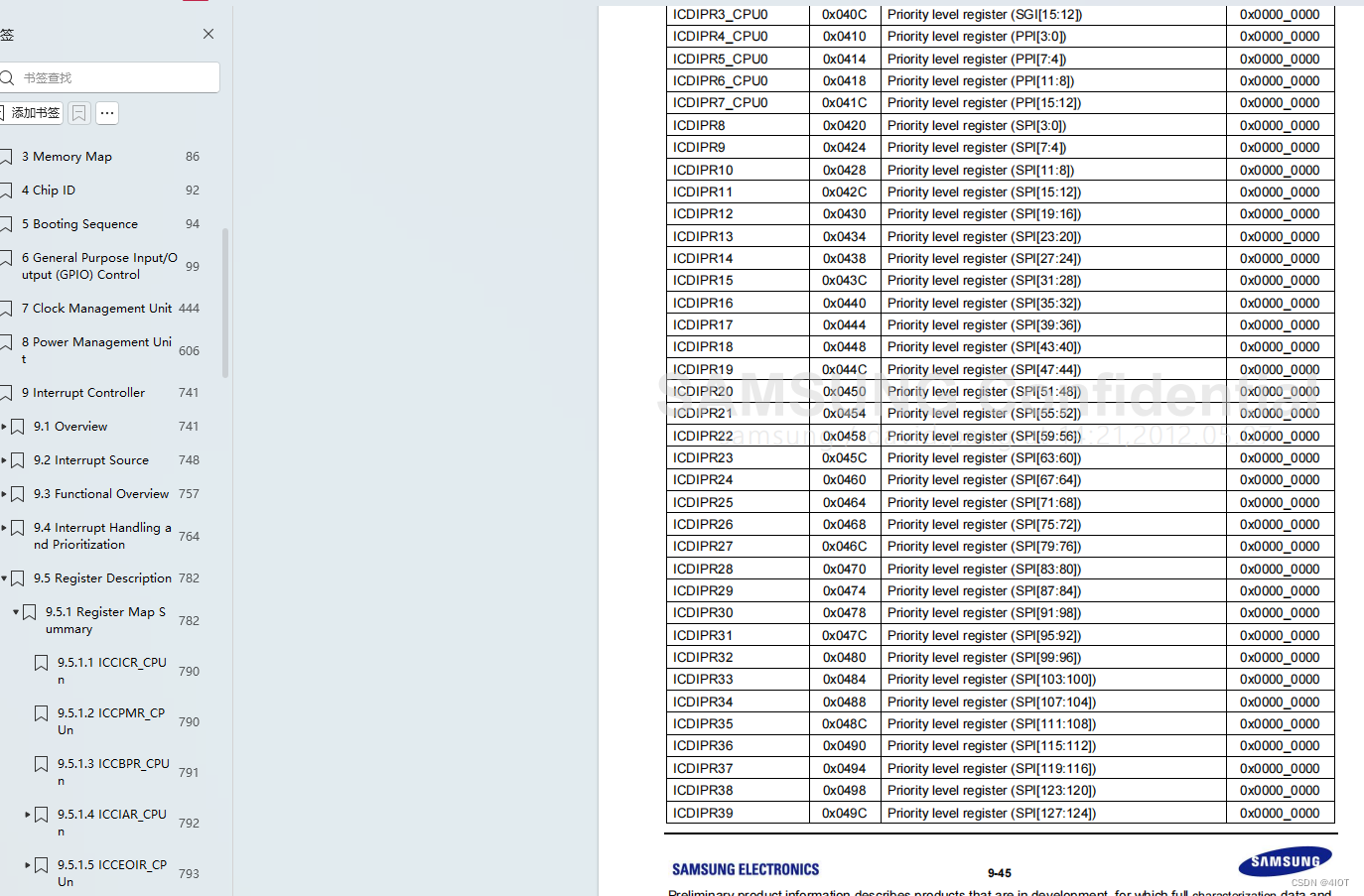

3.5 補充:中斷控制器優先級設置寄存器

4?GPIO中斷編程?

要求:KEY3按下時產生中斷,來點亮LED

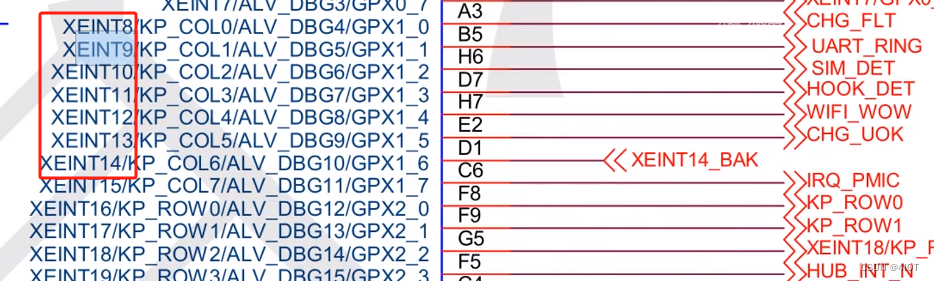

4.1 外設層次設置

讓外部的硬件控制器產生一個中斷信號發送給中斷控制器

GPIO下降沿產生中斷,對應核心板GPX1_1

GPIO下降沿產生中斷,對應核心板GPX1_1

?GPX與中斷寄存器對應關系

?GPX與中斷寄存器對應關系

?

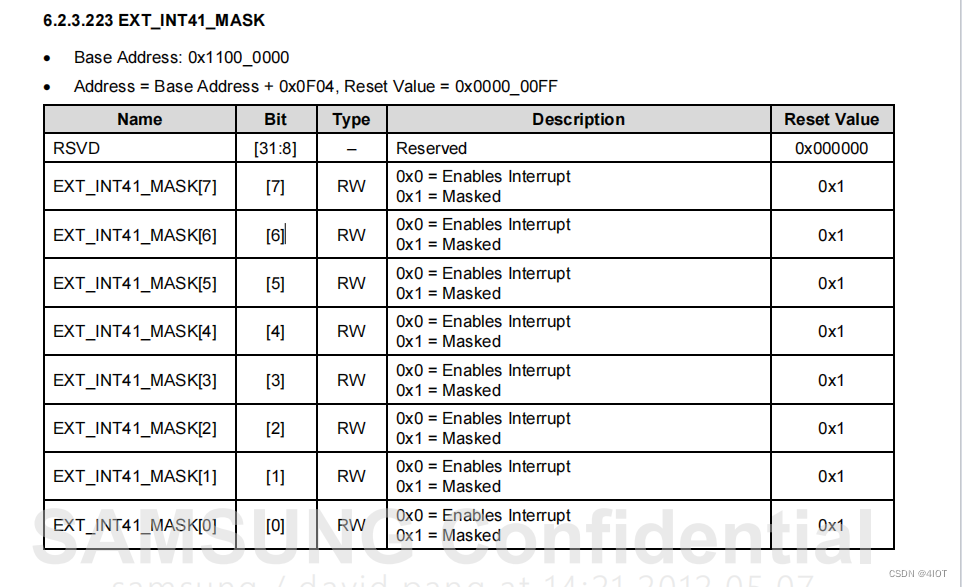

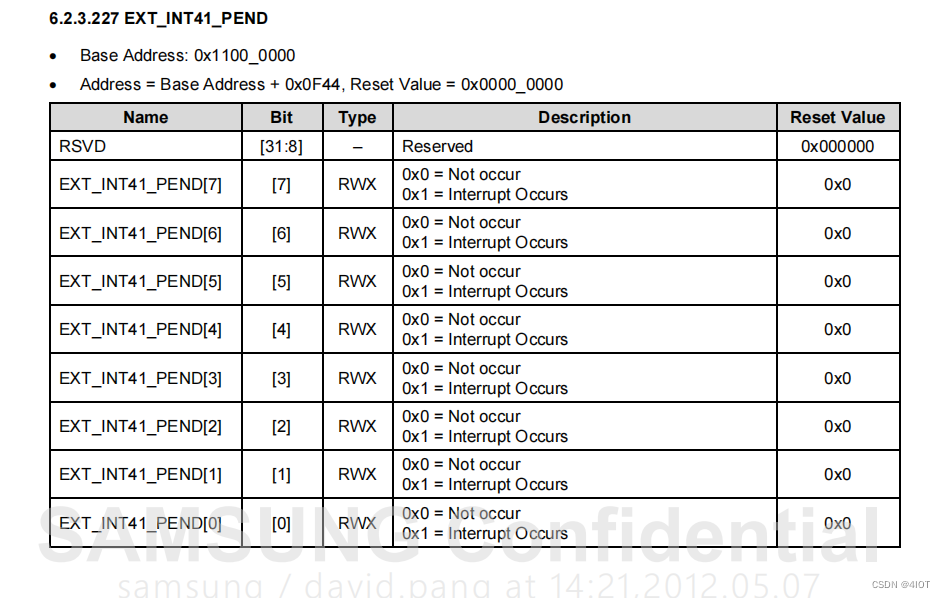

?中斷控制寄存器

使能中斷?

?這個寄存器一般不需要我們寫,中斷發送即會置1 ,用于判斷中斷發生

4.2 中斷控制器層次設置

讓中斷控制器接收外設產生的中斷信號并對其進行管理然后再轉發給CPU處理

ICDDCR置1,打開全局中斷,使其能接收外設產生的中斷信號并轉發到CPU接口

ICDISER_CPU,25位置1,使能57號中斷,使中斷控制器接收到57號中斷后能將其轉發到CPU接口

ICDIPTR14,000000001,選擇CPU0來處理57號中斷

ICCICR,使能中斷控制器和CPU0之間的接口,使中斷控制器轉發的中斷信號能夠到達CPU0

?

4.3 程序代碼

#include "exynos_4412.h"int main()

{/*外設層次 - 讓外部的硬件控制器產生一個中斷信號發送給中斷控制器*//*將GPX1_1設置成中斷功能*/GPX1.CON = GPX1.CON | (0xF << 4);/*設置GPX1_1的中斷觸發方式為下降沿觸發*/EXT_INT41_CON = EXT_INT41_CON & (~(0x7 << 4)) | (0x2 << 4);/*使能GPX1_1的中斷功能*/EXT_INT41_MASK = EXT_INT41_MASK & (~(1 << 1));/*中斷控制器層次 - 讓中斷控制器接收外設產生的中斷信號并對其進行管理然后再轉發給CPU處理*//*全局使能中斷控制器使其能接收外設產生的中斷信號并轉發到CPU接口*/ICDDCR = ICDDCR | 1;/*在中斷控制器中使能57號中斷,使中斷控制器接收到57號中斷后能將其轉發到CPU接口*/ICDISER.ICDISER1 = ICDISER.ICDISER1 | (1 << 25);/*選擇由CPU0來處理57號中斷*/ICDIPTR.ICDIPTR14 = ICDIPTR.ICDIPTR14 & (~(0xFF << 8)) | (0X01 << 8);/*使能中斷控制器和CPU0之間的接口,使中斷控制器轉發的中斷信號能夠到達CPU0*/CPU0.ICCICR = CPU0.ICCICR | 1;GPX2.CON = GPX2.CON & (~(0xF << 28)) | (0x1 << 28);while(1){ /*點亮LED2*/GPX2.DAT = GPX2.DAT | (1 << 7); /*延時*/Delay(1000000);/*熄滅LED2*/GPX2.DAT = GPX2.DAT & (~(1 << 7));/*延時*/Delay(1000000);} return 0;

}

中斷處理下一篇

十九 漫水填充)

)