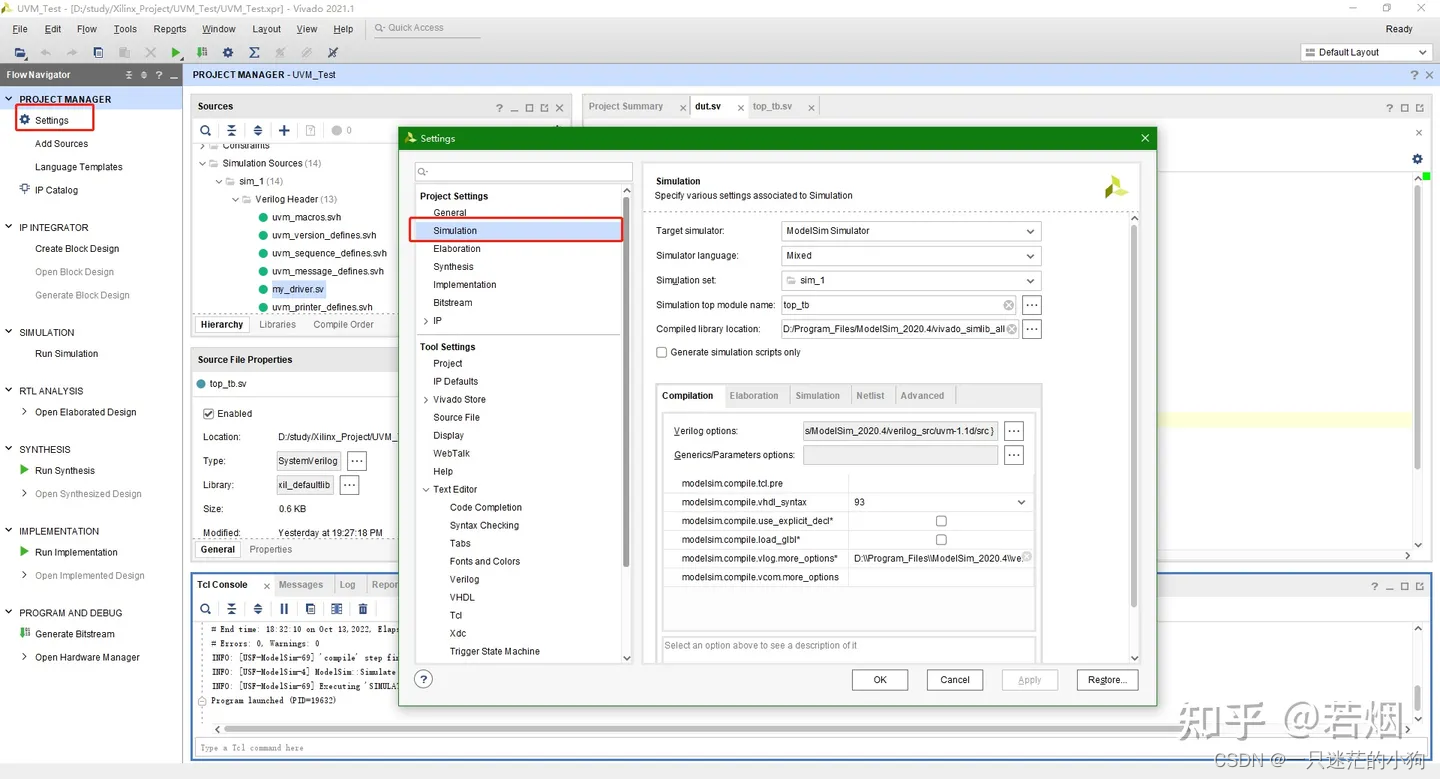

- 打開Vivado,打開對應工程,點擊左側Flow Navigator-->PROJECT MANAGER-->Settings,打開設置面板。

- 點擊Project Settings-->Simulation選項卡,如下圖所示。

-

將Target simulator設為Modelsim Simulator。

-

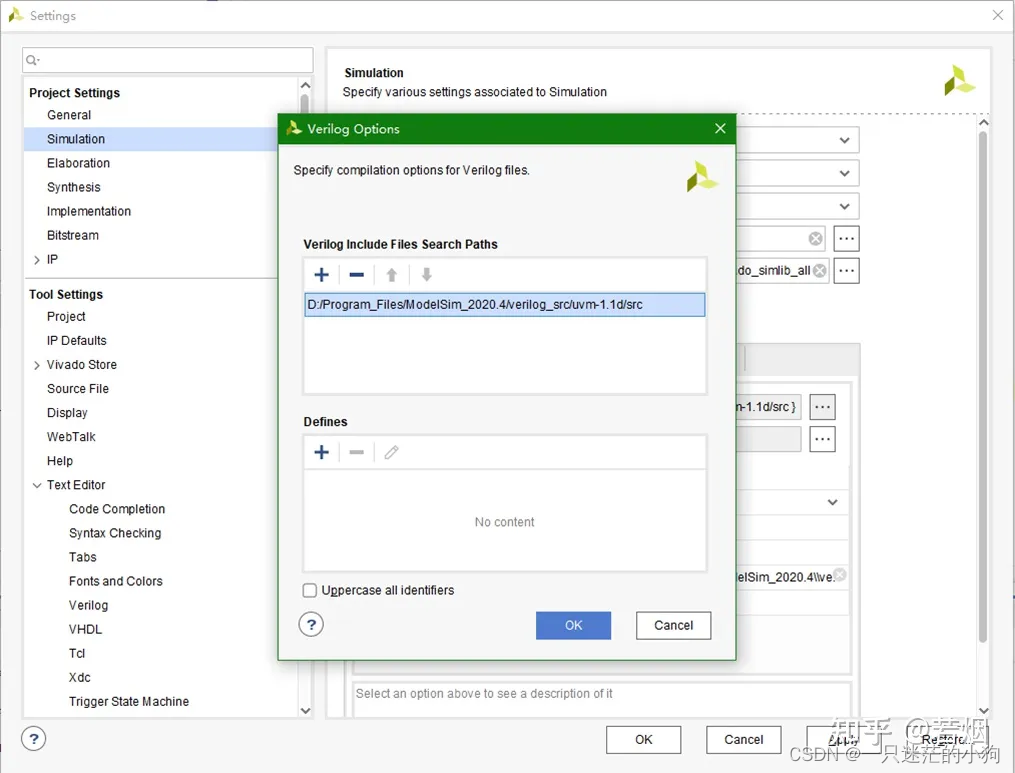

?在下方的Compilation欄中,點擊Verilog options右側的…按鈕,添加D:/Program_Files/ModelSim_2020.4/verilog_src/uvm-1.1d/src作為Verilog Include Files Search Paths,如下圖所示。注意,D:/Program_Files/ModelSim_2020.4是我的Modelsim安裝地址,Modelsim安裝目錄下就有對應的UVM庫,這里選擇verilog_src/uvm-1.1d/src。

-

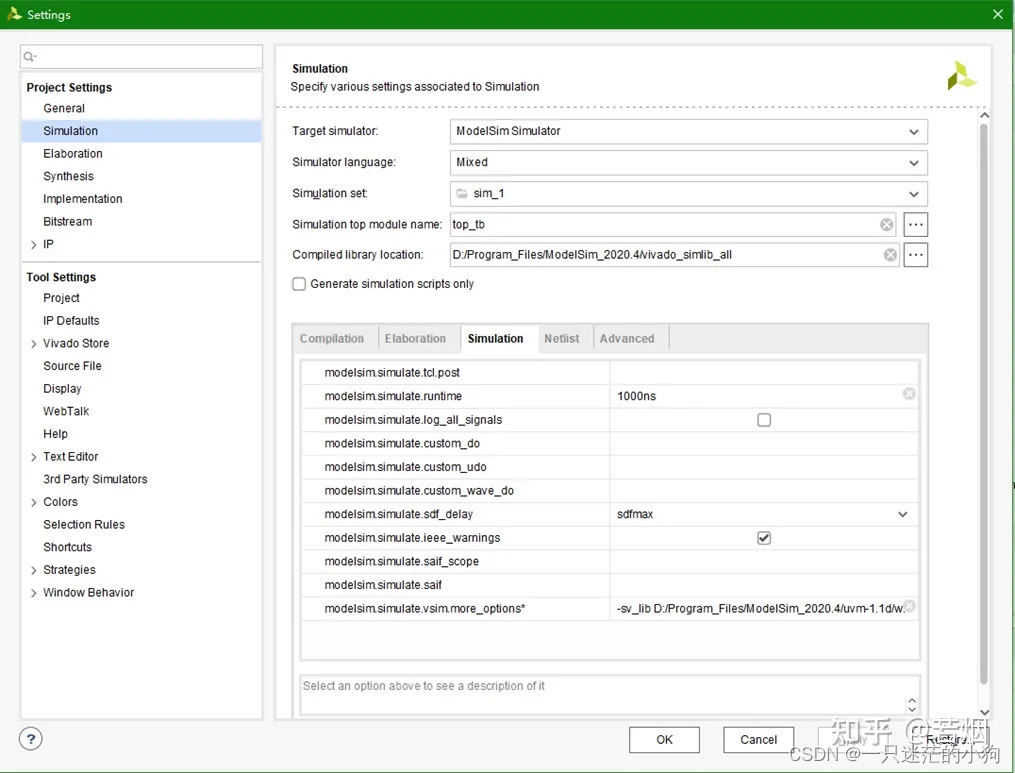

?在modelsim.compile.vlog.more_options中,輸入D:/Program_Files/ModelSim_2020.4/verilog_src/uvm-1.1d/src/uvm_pkg.sv。同樣,D:/Program_Files/ModelSim_2020.4是我的Modelsim安裝地址,Modelsim安裝目錄下就有verilog_src/uvm-1.1d/src/uvm_pkg.sv。

-

將Compilation欄切換為Simulation,在下方的modelsim.simulate.vsim.more_options中,輸入-sv_lib D:/Program_Files/ModelSim_2020.4/uvm-1.1d/win64/uvm_dpi。,如下圖所示。

-

在左上角Sources窗口中添加對應的設計文件和仿真文件,這里設計文件是dut.sv,仿真文件是top_tb.sv。

-

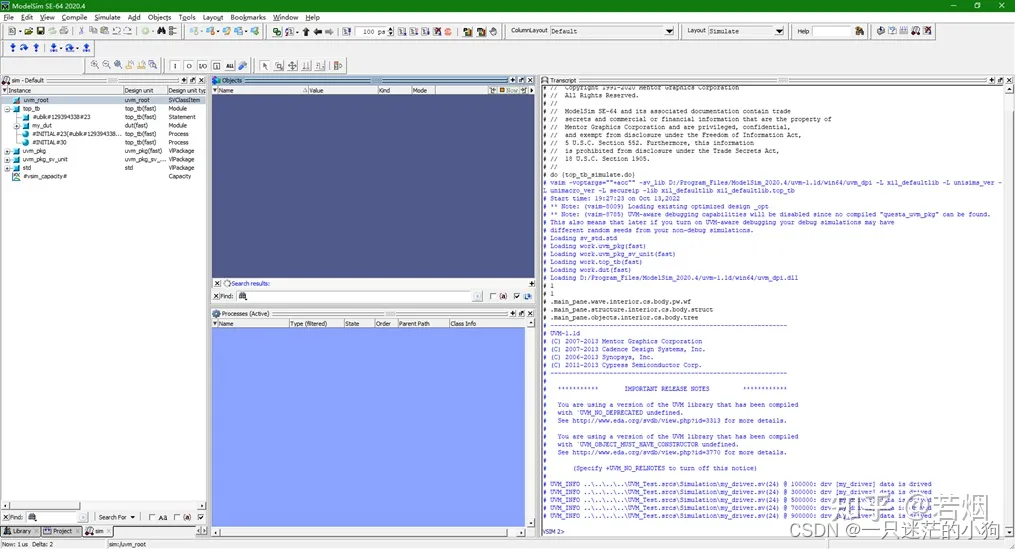

點擊左側Flow Navigator-->SIMULATION-->Run Simulation-->Run Behavior Simulation,運行行為級仿真。

-

在Modelsim的Transcript窗口中,可以看到相應輸出,當然也可以查看信號波形,如下圖所示。

轉自:Vivado & Modelsim聯合進行UVM仿真指南 - 知乎

轉自:Vivado & Modelsim聯合進行UVM仿真指南 - 知乎

Vivado Modelsim聯合進行UVM仿真指南

本文來自互聯網用戶投稿,該文觀點僅代表作者本人,不代表本站立場。本站僅提供信息存儲空間服務,不擁有所有權,不承擔相關法律責任。 如若轉載,請注明出處:http://www.pswp.cn/news/164530.shtml 繁體地址,請注明出處:http://hk.pswp.cn/news/164530.shtml 英文地址,請注明出處:http://en.pswp.cn/news/164530.shtml

如若內容造成侵權/違法違規/事實不符,請聯系多彩編程網進行投訴反饋email:809451989@qq.com,一經查實,立即刪除!相關文章

OpenGL 繪制圓形平面(Qt)

文章目錄 一、簡介二、代碼實現三、實現效果一、簡介 這里使用一種簡單的思路來生成一個圓形平面: 首先,我們需要生成一個單位圓,半徑為1,法向量為(0, 0, 1),這一步我們可以使用一些函數生成圓形點集。之后,指定面片的索引生成一個圓形平面。當然這里為了后續管理起來方便…

Py之PyMuPDF:PyMuPDF的簡介、安裝、使用方法之詳細攻略

Py之PyMuPDF:PyMuPDF的簡介、安裝、使用方法之詳細攻略 目錄

PyMuPDF的簡介

PyMuPDF的安裝

PyMuPDF的使用方法

1、基礎用法 PyMuPDF的簡介

PyMuPDF是一個高性能的Python庫,用于PDF(和其他)文檔的數據提取,分析,轉換和操作。 …

基于JavaWeb+SSM+Vue校園水電費管理小程序系統的設計和實現

基于JavaWebSSMVue校園水電費管理小程序系統的設計和實現 源碼獲取入口Lun文目錄前言主要技術系統設計功能截圖訂閱經典源碼專欄Java項目精品實戰案例《500套》 源碼獲取 源碼獲取入口

Lun文目錄

摘 要 III Abstract 1 1 系統概述 2 1.1 概述 2 1.2課題意義 3 1.3 主要內容 3…

使用【畫圖】軟件修改圖片像素、比例和大小

打開電腦畫圖軟件,點擊開始 windows附件 畫圖 在畫圖軟件里選擇需要調整的照片,點擊文件 打開 在彈出窗口中選擇照片后點擊打開 照片在畫圖軟件中打開后,對照片進行調整。按圖中順序進行 確定后照片會根據設定的值自動調整 保存…

Codeforces Round 745 (Div. 2)(C:前綴和+滑動窗口,E:位運算加分塊)

Dashboard - Codeforces Round 745 (Div. 2) - Codeforces

A:

答案就是2n!/2,

對于當前滿足有k個合法下標的排列,就是一個n-k個不合法的下標的排列,

所以每一個合法排列都相反的存在一個

對稱性

#include<bits/stdc.h>

using nam…

【Redisson】基于自定義注解的Redisson分布式鎖實現

前言

在項目中,經常需要使用Redisson分布式鎖來保證并發操作的安全性。在未引入基于注解的分布式鎖之前,我們需要手動編寫獲取鎖、判斷鎖、釋放鎖的邏輯,導致代碼重復且冗長。為了簡化這一過程,我們引入了基于注解的分布式鎖&…

JS獲取時間戳的五種方法

一、JavasCRIPT時間轉時間戳

JavaScript獲得時間戳的方法有五種,后四種都是通過實例化時間對象new Date() 來進一步獲取當前的時間戳,JavaScript處理時間主要使用時間對象Date。

方法一:Date.now()

Date.now()可以獲得當前的時間戳&#x…

快速學會使用Python3.12的新特性

一、 PEP 695: 類型形參語法的革新

PEP 695 在 Python 3.12 中引入了一種新穎且更為清晰的方式來定義泛型類和函數,旨在提升類型參數的明確性和簡潔性。這個提案不僅改善了類型系統的可讀性,還增強了其功能性。以下是這些變化的詳細概述:

1…

(四)C語言之符號常量概述

(四)C語言之符號常量概述 一、符號常量概述 一、符號常量概述

在程序中使用像300,20等這樣的等類似的“幻數”不是一個好的習慣,它們無法向閱讀該程序的人提供更多有用的信息,從而使得修改程序變得困難。處理這種幻數的一種方法是…

unreal 指定windows SDK

路徑 : “C:\Users\Administrator\AppData\Roaming\Unreal Engine\UnrealBuildTool\BuildConfiguration.xml”

在Configuration中添加 <WindowsPlatform><WindowsSdkVersion>10.0.20348.0</WindowsSdkVersion></WindowsPlatform>示例&…

R數據分析:集成學習方法之隨機生存森林的原理和做法,實例解析

很久很久以前給大家寫過決策樹,非常簡單明了的算法。今天給大家寫隨機(生存)森林,隨機森林是集成了很多個決策數的集成模型。像隨機森林這樣將很多個基本學習器集合起來形成一個更加強大的學習器的這么一種集成思想還是非常好的。…

算法面試題:反轉一個整數

題目:反轉一個整數。例如,輸入123,輸出321;輸入-456,輸出-654。注意:反轉后的整數在32位帶符號整數范圍內。

編寫一個函數 reverseInteger(x: int) -> int 來實現這個功能。

答案:

def re…

【前端】必學知識ES6 1小時學會

1.ES6概述

2.let和const的認識

3.let、const、var的區別

4.模板字符串

5.函數默認參數

6.箭頭函數【重點】

?編輯7.對象初始化簡寫以及案例分析 【重點】

8.對象解構

8.對象傳播操作符

9.對象傳播操作符案例分析

?編輯 10.數組Map

11.數組Reduce

12.NodeJS小結 …

代碼隨想錄算法訓練營第四十四天【動態規劃part06】 | 完全背包、518. 零錢兌換 II、377. 組合總和 Ⅳ

完全背包

有N件物品和一個最多能背重量為W的背包。第i件物品的重量是weight[i],得到的價值是value[i] 。每件物品都有無限個(也就是可以放入背包多次),求解將哪些物品裝入背包里物品價值總和最大。

題目鏈接:

題目頁…

計算機畢業設計 基于Hadoop的物品租賃系統的設計與實現 Java實戰項目 附源碼+文檔+視頻講解

博主介紹:?從事軟件開發10年之余,專注于Java技術領域、Python人工智能及數據挖掘、小程序項目開發和Android項目開發等。CSDN、掘金、華為云、InfoQ、阿里云等平臺優質作者? 🍅文末獲取源碼聯系🍅 👇🏻 精…

YOLO目標檢測——泄露檢測數據集下載分享【含對應voc、coco和yolo三種格式標簽】

實際項目應用:泄露檢測數據集說明:泄露檢測數據集,真實場景的高質量圖片數據,數據場景豐富,含多個類別標簽說明:使用lableimg標注軟件標注,標注框質量高,含voc(xml)、coco(json)和yo…

【JavaSE】不允許你不會使用String類

🎥 個人主頁:深魚~🔥收錄專欄:JavaSE🌄歡迎 👍點贊?評論?收藏

目錄

前言:

一、常用方法

1.1 字符串構造

1.2 String對象的比較

(1)比較是否引用同一個對象

注意…

)

(C:前綴和+滑動窗口,E:位運算加分塊))

C語言之符號常量概述)