基于FPGA的超聲波顯示水位距離

- 前言

- 一、整體框架

- 二、代碼架構

- 1.超聲波測距模塊

- 2.藍牙數據發送模塊

- 3.數碼管數據切換模塊

- 4.數碼管驅動模塊

- 6.串口驅動

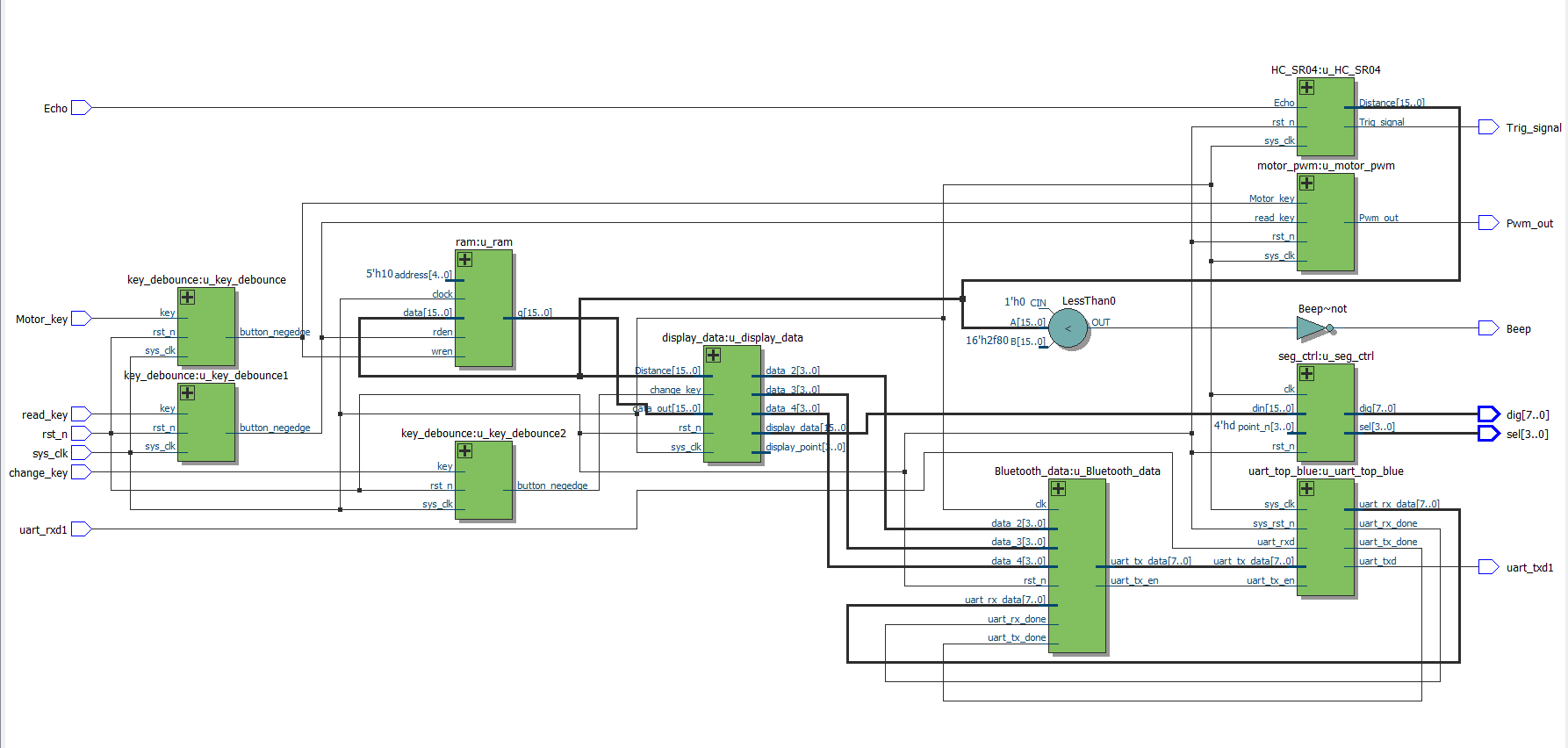

- 7.頂層模塊

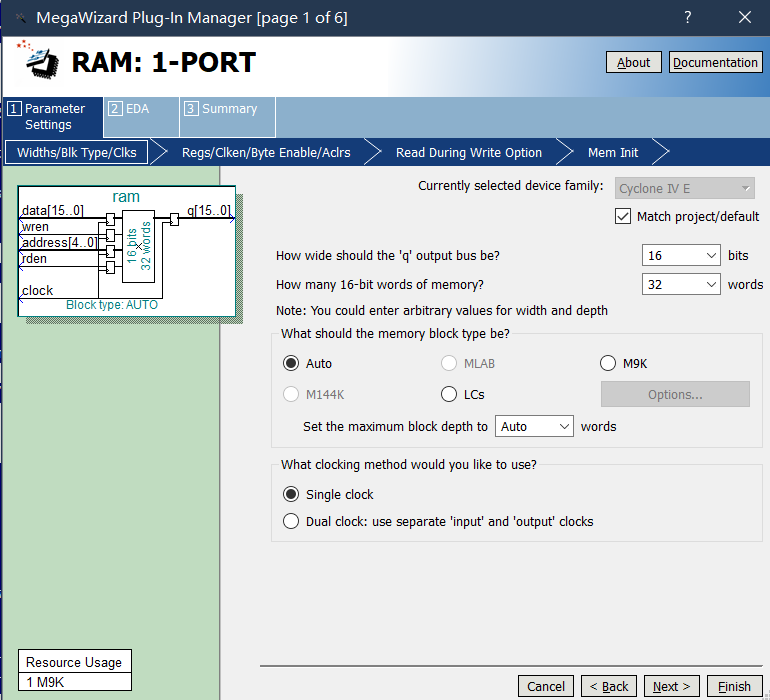

- 8.RAM ip核

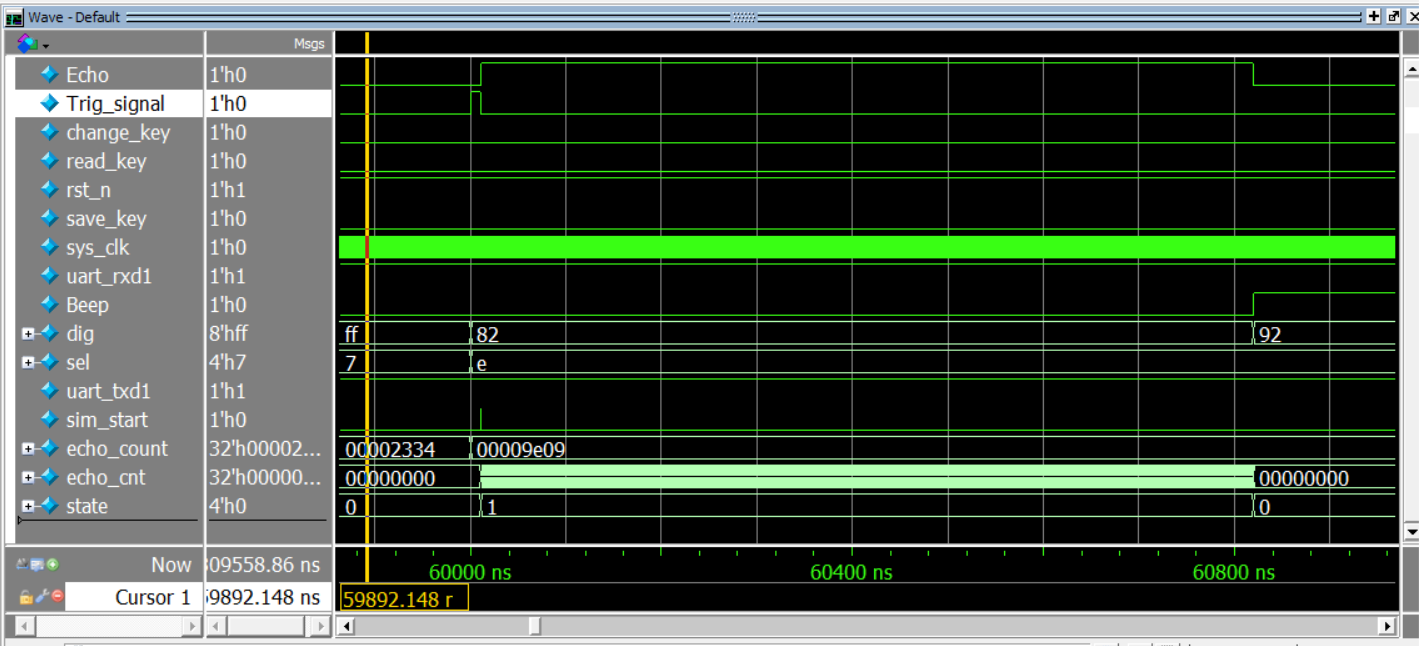

- 仿真相關截圖

前言

隨著工業化進程的加速和環境保護意識的提升,對水資源管理和水位監測的需求日益迫切。傳統的水位監測系統多采用單片機或PLC作為控制核心存在處理速度慢、實時性差、擴展性有限等問題。基于FPGA的水位監測系統以其強大的并行處理能力、高度的靈活性和可重配置性,為水位監測提供了新的解決方案。本課題旨在設計并實現一個基于FPGA的水位監測系統,通過實時采集水位數據,結合先進的數據處理算法,實現高效、準確的水位監測。

本課題聚焦于設計一個基于FPGA的水位監測系統,它通過部署在水源處的傳感器精確獲取水位信息,利用FPGA強大的并行處理能力實時分析數據一旦水位超限立即觸發報警,并上傳數據至監測中心進行記錄和存儲。

1)查找資料對水位監測技術進行了解,提出系統整體設計方案。

2)選擇適合的傳感器模塊、FPGA模塊、通信模塊、顯示塊等進行系統硬件設計。

3)利用自頂向下的設計方法進行系統頂層設計,并分模塊進行FPGA程序設進行軟硬件系統調試。

一、整體框架

硬件需求:FPGA開發板、數碼管模塊、3個按鍵、1個復位按鍵、藍牙模塊、超聲波測距模塊、蜂鳴器模塊

軟件模塊框架:

二、代碼架構

(仿真不需要按鍵消抖,同時時間間隔縮小)

1.超聲波測距模塊

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/04/12 16:01:55

// Design Name:

// Module Name: HC_SR04

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module HC_SR04(input sys_clk , input rst_n, //signal input Echo,output wire [15:0] Distance,output reg Trig_signal);parameter IDLE=4'd0;

parameter SEND=4'd1;

parameter RECIEVE=4'd2;

parameter OVER=4'd3;parameter MAX_CNT=24'd500;

parameter time_1s=32'd50000000;

reg [3:0] state;

reg [3:0] state_1;

reg [23:0] cnt;

reg [31:0] time_cnt;

reg [23:0] distance_temp;

reg key_start;assign Distance=distance_temp/1000;

always @(posedge sys_clk or negedge rst_n)beginif(!rst_n)begintime_cnt<=32'd0;key_start<=1'b0;endelse if(time_cnt<time_1s)begintime_cnt<=time_cnt+1;key_start<=1'b0;endelse if(time_cnt==time_1s)begintime_cnt<=32'd0;key_start<=1'b1;end

endalways @(posedge sys_clk or negedge rst_n)beginif(!rst_n)beginstate<=IDLE;Trig_signal<=1'b0;state_1<=IDLE;distance_temp<=24'd10000000;cnt<=24'd0;endelse begincase(state)IDLE:begincnt<=24'd0;if(key_start==1'b1)beginstate<=SEND;endelse beginstate<=IDLE;endendSEND:beginif(cnt<MAX_CNT)begincnt<=cnt+1;Trig_signal<=1'b1;state<=SEND;endelse begincnt<=16'd0;Trig_signal<=1'b0;state<=RECIEVE;endendRECIEVE:begincase(state_1)IDLE:beginif(Echo==1'b1)beginstate_1<=RECIEVE; endelse beginstate_1<=IDLE;endendRECIEVE:beginif(Echo==1'b1)begincnt<=cnt+1; endelse begincnt<=cnt+1;state_1<=OVER;endendOVER:beginstate_1<=IDLE;state<=OVER;enddefault:state_1<=IDLE;endcaseendOVER:begindistance_temp<=cnt*34;state<=IDLE;enddefault:state<=IDLE;endcaseend

endendmodule2.藍牙數據發送模塊

module Bluetooth_data(input clk,input rst_n,input [3:0] data_3,input [3:0] data_2,input [3:0] data_4,input uart_tx_done,input [7 :0] uart_rx_data,input uart_rx_done,output reg uart_tx_en,output reg [7:0] uart_tx_data);parameter IDLE = 4'd0;parameter WAIT_1s = 4'd1;parameter SEND = 4'd2;parameter OVER = 4'd3;parameter count_max = 32'd50000000; ////spo2:23.6 ----> 74 65 6D 70 3A 32 33 2E 36 0d 0a//hert:23.6 ----> 68 75 6D 69 3A 32 33 2E 36 0d 0areg [87:0] cmd_temp ={8'h68,8'h20,8'h3a,8'h32,8'h32,8'h2e,8'h33,8'h63,8'h6d,8'h0d,8'h0a};reg [87:0] cmd_humi ={8'h68,8'h20,8'h3a,8'h32,8'h32,8'h2e,8'h33,8'h63,8'h6d,8'h0d,8'h0a};reg [3: 0] state;reg [31:0] count;reg [5 :0] tx_count;reg [1: 0] tx_en_count;reg uart_tx_en_temp;reg [1 :0] change_count;wire [7:0] bluedata_1;wire [7:0] bluedata_2;wire [7:0] bluedata_3;assign bluedata_1=(data_4==4'd0)?8'h20:8'h30+data_4;assign bluedata_2=8'h30+data_3;assign bluedata_3=8'h30+data_2;//����??tx_dataalways @(posedge clk or negedge rst_n) beginif(!rst_n) beginuart_tx_data <= 8'd0;endelse if(change_count==2'd0)beginif((state==SEND) && tx_count<8'd3 ) beginuart_tx_data <= cmd_temp[87 - tx_count *8 -:8];endelse if((state==SEND) && tx_count==8'd3 ) beginuart_tx_data <= bluedata_1;endelse if((state==SEND) && tx_count==8'd4 ) beginuart_tx_data <= bluedata_2;endelse if((state==SEND) && tx_count==8'd5 ) beginuart_tx_data <= 8'h3a;endelse if((state==SEND) && tx_count==8'd6 ) beginuart_tx_data <= bluedata_3;endelse if((state==SEND) && tx_count<8'd11 ) beginuart_tx_data <= cmd_temp[87 - tx_count *8 -:8];end endelse if(change_count==2'd1)beginif((state==SEND) && tx_count<8'd3 ) beginuart_tx_data <= cmd_humi[87 - tx_count *8 -:8];endelse if((state==SEND) && tx_count==8'd3 ) beginuart_tx_data <= bluedata_1;endelse if((state==SEND) && tx_count==8'd4 ) beginuart_tx_data <= bluedata_2;endelse if((state==SEND) && tx_count==8'd5 ) beginuart_tx_data <= 8'h3a;endelse if((state==SEND) && tx_count==8'd6 ) beginuart_tx_data <= bluedata_3;endelse if((state==SEND) && tx_count<8'd11 ) beginuart_tx_data <= cmd_humi[87 - tx_count *8 -:8];end endend//tx_en timealways @(posedge clk or negedge rst_n) beginif(!rst_n) begintx_en_count <= 2'b0;endelse if((state==SEND) && tx_en_count<2'd1 && tx_count==8'd0) begintx_en_count <=tx_en_count+ 1'd1;endelse if((state==SEND) && tx_en_count==2'd1 && tx_count==8'd0) begintx_en_count <= 2'd3;endelse if(state==OVER)begintx_en_count <= 2'd0;endelse begintx_en_count <= tx_en_count;end

end//����??tx_countalways @(posedge clk or negedge rst_n) beginif(!rst_n) begintx_count <= 8'd0;endelse if(state==SEND) beginif(uart_tx_done==1'd1)tx_count <= tx_count+1'b1;endelse begintx_count <= 8'd0;end

end//����??data_tx_enalways @(posedge clk or negedge rst_n) beginif(!rst_n) beginuart_tx_en_temp <= 1'b0;uart_tx_en <= uart_tx_en_temp;endelse if((state==SEND ) && tx_en_count==1) beginuart_tx_en_temp <= 1'b1;uart_tx_en <= uart_tx_en_temp;endelse if((state==SEND ) && tx_count<8'd10 && uart_tx_done==1)beginuart_tx_en_temp <= 1'b1;uart_tx_en <= uart_tx_en_temp;endelse beginuart_tx_en_temp <= 1'b0;uart_tx_en <= uart_tx_en_temp;endend//state go always @(posedge clk or negedge rst_n) beginif(!rst_n) begincount <= 32'd0;endelse if(state == WAIT_1s && count < count_max)begincount <= count + 32'd1;endelse if(state == WAIT_1s && count == count_max)begincount <= 32'd0;endelse begincount <= count;endend//state go always @(posedge clk or negedge rst_n) beginif(!rst_n) beginstate <= IDLE;change_count<=2'd0;endelse begincase(state)IDLE:beginstate<=WAIT_1s;endWAIT_1s:beginif(count==count_max)beginstate<=SEND;endelse beginstate<=WAIT_1s;endendSEND:beginif(tx_count==6'd11)beginstate <= OVER;endelse beginstate <= SEND;endendOVER:beginstate <= IDLE;if(change_count<2'd1)beginchange_count<=change_count+2'd1;endelse if(change_count==2'd1)beginchange_count<=2'd0;endenddefault:state <= IDLE;endcaseendendendmodule3.數碼管數據切換模塊

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/05/26 14:56:37

// Design Name:

// Module Name: display_data

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module display_data(input sys_clk , input rst_n, input change_key, input [15:0] Distance,input [15:0] data_out,output wire [3:0] data_3,output wire [3:0] data_2,output wire [3:0] data_4,output reg [3 :0] display_point,output reg [15:0] display_data);wire [15:0] Distance_temp;wire [15:0] data;wire [3:0] data_1;

// wire [3:0] data_3;

// wire [3:0] data_2;

// wire [3:0] data_4;reg [1:0] cnt;function [15:0]Hex_to_Doc;

input [15:0] num_h;

beginHex_to_Doc = num_h[3:0] + num_h[7:4]*16 +num_h[11:8]*256 +num_h[15:12]*4096;

end

endfunctionassign data=(cnt==2'd0)?Distance:data_out;assign Distance_temp=Hex_to_Doc(data);assign data_1=Distance_temp%10;assign data_2=(Distance_temp%100)/10;assign data_3=(Distance_temp%1000)/100;assign data_4=(Distance_temp/1000);always @(posedge sys_clk or negedge rst_n)beginif(!rst_n)begincnt<=2'd0;endelse if(change_key && cnt<2'd1)begincnt<=cnt+1;endelse if(change_key && cnt==2'd1)begincnt<=2'd0;endendalways @(*)beginif(data_4==4'd0)begindisplay_data<={4'he,data_3,data_2,data_1};display_point<=4'b1111;endelse begindisplay_data<={data_4,data_3,data_2,data_1};display_point<=4'b1111;endendendmodule4.數碼管驅動模塊

module seg_ctrl( input clk ,input rst_n ,input [15:0] din ,//????6��???????????????��???????4��input [3:0] point_n ,//????��????????��output reg [3:0] sel ,//????��?output reg [7:0] dig //???????

);

//---------<????????>--------------------------------------------------------- parameter TIME_1MS = 50_000;//1ms//????????????????localparam NUM_0 = 7'b100_0000,//0NUM_1 = 7'b111_1001,//1NUM_2 = 7'b010_0100,//NUM_3 = 7'b011_0000,//NUM_4 = 7'b001_1001,//NUM_5 = 7'b001_0010,//NUM_6 = 7'b000_0010,//NUM_7 = 7'b111_1000,//NUM_8 = 7'b000_0000,//NUM_9 = 7'b001_0000,//A = 7'b000_1000,//B = 7'b000_0011,//bC = 7'b100_0110,//OFF = 7'b111_1111,//???CROSS = 7'b011_1111,//????//D = 7'b010_0001,//d//E = 7'b000_0110,//F = 7'b000_1110;////---------<?????????>-----------------------------------------------------reg [15:0] cnt_1ms ;//1ms???????????????????????wire add_cnt_1ms ;wire end_cnt_1ms ;reg [3:0] disp_data ;//??��??????????????reg point_n_r ;//??��???????????��????//****************************************************************

//--cnt_1ms

//****************************************************************always @(posedge clk or negedge rst_n)begin if(!rst_n)begincnt_1ms <= 'd0;end else if(add_cnt_1ms)begin if(end_cnt_1ms)begin cnt_1ms <= 'd0;endelse begin cnt_1ms <= cnt_1ms + 1'b1;end endend assign add_cnt_1ms = 1'b1;//??????????assign end_cnt_1ms = add_cnt_1ms && cnt_1ms == TIME_1MS - 1;//****************************************************************

//--seg_sel

//****************************************************************always @(posedge clk or negedge rst_n)begin if(!rst_n)beginsel <= 4'b1_110;//?????��???????????��??????end else if(end_cnt_1ms)begin sel <= {sel[2:0],sel[3]};//???????end end//****************************************************************

//--disp_data

//****************************************************************always @(posedge clk or negedge rst_n)begin if(!rst_n)begindisp_data <= 'd0;point_n_r <= 1'b1;end else begin case (sel)4'b1_110 : begin disp_data <= din[3:0] ; point_n_r <= point_n[0]; end//???��??????????????4'b1_101 : begin disp_data <= din[7:4] ; point_n_r <= point_n[1]; end4'b1_011 : begin disp_data <= din[11:8] ; point_n_r <= point_n[2]; end4'b0_111 : begin disp_data <= din[15:12]; point_n_r <= point_n[3]; enddefault: disp_data <= 'd0;endcaseend end//****************************************************************

//--seg_dig

//****************************************************************always @(*)begin case (disp_data)0 : dig = {point_n_r,NUM_0};1 : dig = {point_n_r,NUM_1};2 : dig = {point_n_r,NUM_2};3 : dig = {point_n_r,NUM_3};4 : dig = {point_n_r,NUM_4};5 : dig = {point_n_r,NUM_5};6 : dig = {point_n_r,NUM_6};7 : dig = {point_n_r,NUM_7};8 : dig = {point_n_r,NUM_8};9 : dig = {point_n_r,NUM_9};10 : dig = {point_n_r,A };11 : dig = {point_n_r,B };12 : dig = {point_n_r,C };13 : dig = {point_n_r,CROSS};14 : dig = {point_n_r,OFF };15 : dig = {point_n_r,F };default: dig = 8'hff;endcaseendendmodule6.串口驅動

module uart_top_blue( input sys_clk , //�?50MHz?��input sys_rst_n, //?�?��λ�??�����Ч//UART�?� input uart_rxd , //UART���??�output uart_txd , //UART���??�input uart_tx_en, //UART���������?�output wire uart_rx_done, //UART���������?� output wire uart_tx_done, //UART���������?� input [7:0] uart_tx_data, //UART�������� output wire [7:0] uart_rx_data //UART�������� );//parameter define

parameter CLK_FREQ = 50000000; //����???��?��

parameter UART_BPS = 9600 ; //���崮�?�����//wire define

//wire uart_rx_done; //UART���������?�

//wire [7:0] uart_rx_data; //UART��������//*****************************************************

//** main code

//*****************************************************//���?���?��

uart_rx_blue #(.CLK_FREQ (CLK_FREQ),.UART_BPS (UART_BPS)) u_uart_rx_blue(.clk (sys_clk ),.rst_n (sys_rst_n ),.uart_rxd (uart_rxd ),.uart_rx_done (uart_rx_done),.uart_rx_data (uart_rx_data));uart_tx_blue #(.CLK_FREQ (CLK_FREQ),.UART_BPS (UART_BPS)) u_uart_tx_blue(.clk (sys_clk ),.rst_n (sys_rst_n ),.uart_tx_en (uart_tx_en),.uart_tx_data (uart_tx_data),.uart_tx_done (uart_tx_done),.uart_txd (uart_txd ),.uart_tx_busy ( ));endmodulemodule uart_rx_blue(input clk , //???��input rst_n , //??��λ������Чinput uart_rxd , //UART���??�output reg uart_rx_done, //UART���������?�output reg [7:0] uart_rx_data //UART���?�������);//parameter define

parameter CLK_FREQ = 100000000; //???��?��

parameter UART_BPS = 115200 ; //���?�����

localparam BAUD_CNT_MAX = CLK_FREQ/UART_BPS; //?�?�?�������?���???�?���BPS_CNT��//reg define

reg uart_rxd_d0;

reg uart_rxd_d1;

reg uart_rxd_d2;

reg rx_flag ; //���?��?�?�?�

reg [3:0 ] rx_cnt ; //�������?�����

reg [15:0] baud_cnt ; //�����?�����

reg [7:0 ] rx_data_t ; //�������??���//wire define

wire start_en;//*****************************************************

//** main code

//*****************************************************

//�������??��?���(��?λ)���?�?��?�����?������?�

assign start_en = uart_rxd_d2 & (~uart_rxd_d1) & (~rx_flag);//�����?�??�?������

always @(posedge clk or negedge rst_n) beginif(!rst_n) beginuart_rxd_d0 <= 1'b0;uart_rxd_d1 <= 1'b0;uart_rxd_d2 <= 1'b0;endelse beginuart_rxd_d0 <= uart_rxd;uart_rxd_d1 <= uart_rxd_d0;uart_rxd_d2 <= uart_rxd_d1;end

end//�����?�?��?

always @(posedge clk or negedge rst_n) beginif(!rst_n) rx_flag <= 1'b0;else if(start_en) //���?��?λrx_flag <= 1'b1; //���?����У���?�?�rx_flag���//��??λ?����?�����?��?�������?�?�rx_flag���else if((rx_cnt == 4'd9) && (baud_cnt == BAUD_CNT_MAX/2 - 1'b1))rx_flag <= 1'b0;elserx_flag <= rx_flag;

end //�����??�������?

always @(posedge clk or negedge rst_n) beginif(!rst_n) baud_cnt <= 16'd0;else if(rx_flag) begin //���?��?���?�������?�������baud_cnt������?������if(baud_cnt < BAUD_CNT_MAX - 1'b1)baud_cnt <= baud_cnt + 16'b1;else baud_cnt <= 16'd0; //�����??�����������?�����end elsebaud_cnt <= 16'd0; //���?��?���?����������

end//�?������?�������rx_cnt������

always @(posedge clk or negedge rst_n) beginif(!rst_n) rx_cnt <= 4'd0;else if(rx_flag) begin //���?��?���?rx_cnt�?����if(baud_cnt == BAUD_CNT_MAX - 1'b1) //�������?�����������?������������?rx_cnt <= rx_cnt + 1'b1; //�������?�������1elserx_cnt <= rx_cnt;endelserx_cnt <= 4'd0; //���?��?���?����������

end //����rx_cnt��?�rxd�??�����

always @(posedge clk or negedge rst_n) beginif(!rst_n) rx_data_t <= 8'b0;else if(rx_flag) begin //??���?��?���?if(baud_cnt == BAUD_CNT_MAX/2 - 1'b1) begin //�ж�baud_cnt�?�����������λ���м�case(rx_cnt)4'd1 : rx_data_t[0] <= uart_rxd_d2; //�?����?�����λ4'd2 : rx_data_t[1] <= uart_rxd_d2;4'd3 : rx_data_t[2] <= uart_rxd_d2;4'd4 : rx_data_t[3] <= uart_rxd_d2;4'd5 : rx_data_t[4] <= uart_rxd_d2;4'd6 : rx_data_t[5] <= uart_rxd_d2;4'd7 : rx_data_t[6] <= uart_rxd_d2;4'd8 : rx_data_t[7] <= uart_rxd_d2; //�?����???�λdefault : ;endcase endelserx_data_t <= rx_data_t;endelserx_data_t <= 8'b0;

end //�����������???��?������?�?

always @(posedge clk or negedge rst_n) beginif(!rst_n) beginuart_rx_done <= 1'b0;uart_rx_data <= 8'b0;end//���������?�����������??λ����baud_cnt������??λ���м�?else if(rx_cnt == 4'd9 && baud_cnt == BAUD_CNT_MAX/2 - 1'b1) beginuart_rx_done <= 1'b1 ; //��?��������?�uart_rx_data <= rx_data_t; //����UART���?������?��и�?end else beginuart_rx_done <= 1'b0;uart_rx_data <= uart_rx_data;end

endendmodule

module uart_tx_blue(input clk , //???��input rst_n , //??��λ������Чinput uart_tx_en , //UART�?���?��input [7:0] uart_tx_data, //UART?���?�����output reg uart_txd , //UART���??�output reg [3:0] tx_cnt , //�������?�����output reg [15:0] baud_cnt , //�����?�����output reg uart_tx_done,output reg uart_tx_busy //����???�?�);//parameter define

parameter CLK_FREQ = 100000000; //???��?��

parameter UART_BPS = 115200 ; //���?�����

localparam BAUD_CNT_MAX = CLK_FREQ/UART_BPS; //?�?�?�������?���???�?���BPS_CNT��//reg define

reg [7:0] tx_data_t; //�������??���

//�����??�������?

always @(posedge clk or negedge rst_n) beginif(!rst_n) uart_tx_done<=1'b0;else if(tx_cnt == 4'd9 && baud_cnt == BAUD_CNT_MAX - 1) beginuart_tx_done<=1'b1;end elseuart_tx_done<=1'b0; //���?��?���?����������

end//*****************************************************

//** main code

//*****************************************************//��uart_tx_en?��?���?������?������?������BUSY�?�

always @(posedge clk or negedge rst_n) beginif(!rst_n) begintx_data_t <= 8'b0;uart_tx_busy <= 1'b0;end//����?��?���?�?���?����?������BUSY�?�else if(uart_tx_en) begintx_data_t <= uart_tx_data;uart_tx_busy <= 1'b1;end//��������??���?��??���?���else if(tx_cnt == 4'd9 && baud_cnt == BAUD_CNT_MAX - 1) begintx_data_t <= 8'b0; //���?������??���uart_tx_busy <= 1'b0; //�����BUSY�?�endelse begintx_data_t <= tx_data_t;uart_tx_busy <= uart_tx_busy;end

end//�����??�������?

always @(posedge clk or negedge rst_n) beginif(!rst_n) baud_cnt <= 16'd0;else if(uart_tx_en) baud_cnt <= 16'd0; //�����?��?���?�������?�������baud_cnt������?������else if(uart_tx_busy) beginif(baud_cnt < BAUD_CNT_MAX - 1'b1)baud_cnt <= baud_cnt + 16'b1;else baud_cnt <= 16'd0; //�����??�����������?�����end elsebaud_cnt <= 16'd0; //���?��?���?����������

end//tx_cnt����

always @(posedge clk or negedge rst_n) beginif(!rst_n) tx_cnt <= 4'd0;else if(uart_tx_en) tx_cnt <= 16'd0; else if(uart_tx_busy) begin //���?��?���?tx_cnt�?����if(baud_cnt == BAUD_CNT_MAX - 1'b1) //�������?�����������?������������?tx_cnt <= tx_cnt + 1'b1; //�������?�������1elsetx_cnt <= tx_cnt;endelsetx_cnt <= 4'd0; //���?��?���?����������

end//����tx_cnt���uart���???�?

always @(posedge clk or negedge rst_n) beginif(!rst_n) uart_txd <= 1'b1;else if(uart_tx_busy) begincase(tx_cnt) 4'd0 : uart_txd <= 1'b0 ; //��?λ4'd1 : uart_txd <= tx_data_t[0]; //����λ����λ4'd2 : uart_txd <= tx_data_t[1];4'd3 : uart_txd <= tx_data_t[2];4'd4 : uart_txd <= tx_data_t[3];4'd5 : uart_txd <= tx_data_t[4];4'd6 : uart_txd <= tx_data_t[5];4'd7 : uart_txd <= tx_data_t[6];4'd8 : uart_txd <= tx_data_t[7]; //����λ����λ4'd9 : uart_txd <= 1'b1 ; //??λdefault : uart_txd <= 1'b1;endcaseendelseuart_txd <= 1'b1; //����?���??�?�?�?

endendmodule

7.頂層模塊

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/04/20 09:30:52

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module top(input sys_clk , input rst_n, input save_key,input read_key,input change_key,input Echo, output wire Trig_signal,input uart_rxd1 , output uart_txd1 ,output wire [3:0] sel,output wire [7:0] dig,output wire sim_start,output wire Beep);//seg signalwire [15:0] display_data;wire [15:0] Distance;wire [3:0] data_3;wire [3:0] data_2;wire [3:0] data_4;wire uart_tx_en1; wire uart_rx_done1; wire uart_tx_done1; wire [7:0] uart_tx_data1; wire [7:0] uart_rx_data1; wire [15:0] data_out;assign Beep=(Distance<16'd500)?1'b0:1'b1;HC_SR04 u_HC_SR04(.sys_clk(sys_clk) ,.rst_n(rst_n) ,.Echo(Echo) ,.Distance(Distance) ,.sim_start(sim_start),.Trig_signal(Trig_signal) );display_data u_display_data(.sys_clk(sys_clk) ,.rst_n(rst_n) ,.Distance(Distance) ,.data_out(data_out) ,.change_key(change_key) ,.data_3(data_3) ,.data_2(data_2) ,.data_4(data_4) ,.display_data(display_data) );ram u_ram (.address ( 5'd1 ),.clock ( sys_clk ),.data ( Distance ),.rden ( read_key ),.wren ( save_key ),.q ( data_out ));Bluetooth_data u_Bluetooth_data(.clk(sys_clk), .rst_n(rst_n), .data_3(data_3) ,.data_2(data_2) ,.data_4(data_4) ,.uart_rx_done (uart_rx_done1),.uart_rx_data (uart_rx_data1),.uart_tx_en (uart_tx_en1),.uart_tx_data (uart_tx_data1),.uart_tx_done (uart_tx_done1) );uart_top_blue u_uart_top_blue(.sys_clk(sys_clk) , .sys_rst_n(rst_n), .uart_rx_done (uart_rx_done1),.uart_rx_data (uart_rx_data1),.uart_tx_en (uart_tx_en1),.uart_tx_data (uart_tx_data1),.uart_tx_done (uart_tx_done1),.uart_rxd(uart_rxd1) , .uart_txd(uart_txd1) );seg_ctrl u_seg_ctrl( .clk(sys_clk) ,.rst_n(rst_n) ,.din(display_data),.point_n(4'b1011) ,.sel(sel) ,.dig(dig)

); endmodule8.RAM ip核

仿真相關截圖

仿真沒有按鍵消抖,測距時間間隔縮短一點,其他正常。

MySQL學習筆記(6):分組查詢,正則表達式)

)

)

對象函數createTemplateMatching())

)