PCI、PCIe中斷概述

PCIe 中斷機制在繼承 PCI 傳統中斷(INTx)的基礎上,引入了更高效的 MSI/MSI-X 方案,以提升設備性能并減少 CPU 輪詢開銷。以下是核心要點及技術演進:

?? ??一、PCIe 中斷類型與演進??

-

??INTx(傳統中斷)??

- ??原理??:通過物理引腳(INTA#~INTD#)發送電平信號,經中斷控制器(如PIC/IO APIC)轉換為中斷請求(IRQ),CPU 通過中斷向量表調用 ISR。

- ??PCIe 兼容性??:PCIe 設備雖無物理引腳,但通過 ??Assert_INTx/Deassert_INTx 消息報文??模擬電平變化,實現軟件兼容。

- ??局限??:共享中斷線易沖突,且需等待所有設備中斷響應完成才能清除信號,效率低。

-

??MSI/MSI-X(消息信號中斷)??

- ??原理??:設備直接向 Host 預設的內存地址寫入特定數據(Message Data),觸發內存寫 TLP 報文提交中斷,無需物理線路。

- ??優勢??:

- ??無共享沖突??:每個中斷向量獨立,避免 INTx 的共享瓶頸。

- ??數據一致性??:中斷寫入操作嚴格按事務順序執行,確保數據先于中斷到達內存。

- ??擴展性??:MSI 支持 32 個連續中斷向量;MSI-X 支持 ??2048 個非連續向量??,適用多隊列設備(如網卡/NVMe)。

- ??配置??:通過 PCIe Capability 結構(Message Address/Data 寄存器)動態設置。

?? ??二、中斷處理流程優化??

-

??INTx 流程??

graph LR A[設備觸發INTx] --> B[中斷控制器轉換IRQ] B --> C[CPU 中斷應答] C --> D[獲取中斷向量] D --> E[執行ISR]- ??問題??:中斷狀態寄存器需手動讀取確認,易因異步信號導致數據競爭。

-

??MSI/MSI-X 流程??

graph LR A[設備寫Message Address] --> B[生成Memory Write TLP] B --> C[Host 解析為中斷請求] C --> D[直接觸發對應ISR]- ??優化點??:

- 消除物理信號延遲,中斷響應更快。

- 支持 ??中斷聚合(Interrupt Coalescing)??,合并多個請求減少 CPU 負載。

- ??優化點??:

🐧 ??三、Linux 中的實現關鍵??

-

??中斷號分配??

- PCIe 設備掃描時,內核通過

of_irq_parse_and_map_pci()解析設備樹中斷路由,分配虛擬中斷號(virq)并寫入配置空間Interrupt Line寄存器。 - 驅動通過

request_irq(pci_dev->irq, ISR)注冊中斷處理函數。

- PCIe 設備掃描時,內核通過

-

??配置空間關鍵寄存器??

寄存器 作用 Interrupt Pin標識設備使用的中斷引腳(1=INTA#, 2=INTB#, 等) Interrupt Line存儲軟件分配的中斷號(Linux 寫入 virq) MSI Capability控制 MSI 使能、消息地址/數據配置 -

??性能問題解決??

- ??中斷風暴??:優化 ISR 邏輯,將耗時操作移至下半部(如 tasklet)。

- ??虛擬化支持??:MSI-X 的向量隔離特性更適配虛擬化環境,避免 VM 中斷干擾。

?? ??四、設計?

- ??優先選用 MSI-X??:尤其多隊列設備(如 25G 網卡),避免向量數量瓶頸。

- ??中斷均衡??:多核系統中,利用

irqbalance將中斷分發不同 CPU 核心。 - ??錯誤處理??:

- 使能 PCIe AER(高級錯誤報告),結合

PERR#/SERR#捕獲物理層錯誤。 - MSI 中斷丟失時,檢查 Capability 結構中的 ??Pending Bits?? 狀態。

- 使能 PCIe AER(高級錯誤報告),結合

?

PCIe二種中斷機制

?? ??一、傳統INTx中斷傳遞(Legacy Interrupt Delivery)??

-

??物理實現原理??

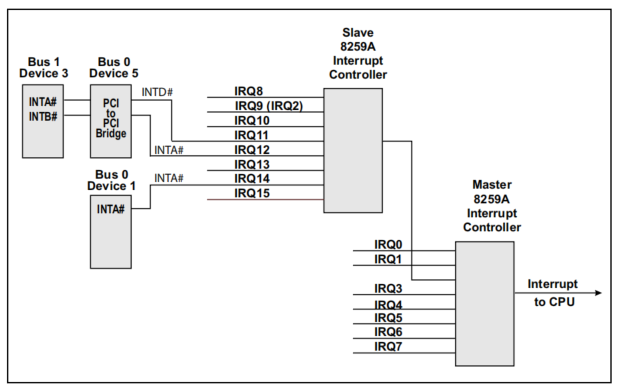

- PCI設備通過??邊帶信號引腳??(INTA#~INTD#)發送電平觸發的中斷請求,經中斷控制器(如8259 PIC)轉換為CPU可識別的INTR信號。

- ??共享沖突問題??:多個設備共用同一中斷線(Wire-OR連接),需等待所有設備中斷響應完成才能釋放信號,導致延遲增加。

-

??PCIe的兼容性改造??

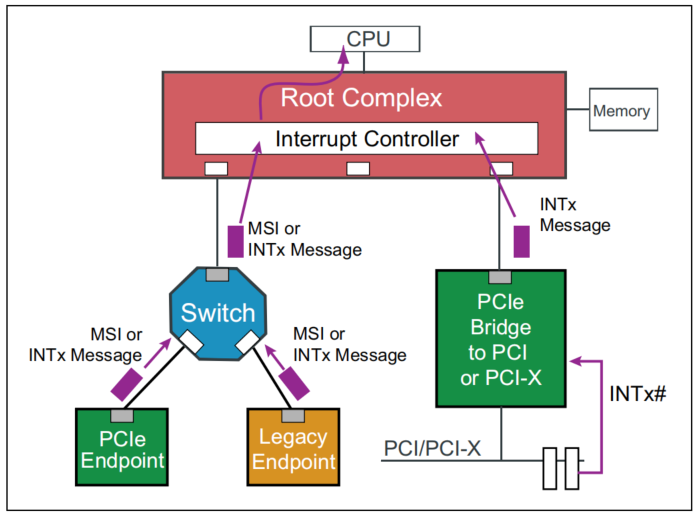

- ??虛擬化實現??:PCIe取消物理引腳,改用 ??Assert_INTx/Deassert_INTx消息報文?? 模擬電平變化(如Assert_INTA消息對應下降沿)。

- ??橋接轉換??:PCIe-to-PCI橋將下游PCI設備的物理INTx#信號轉換為上游的INTx消息(見圖表映射關系)。

graph LR A[PCI設備物理INTx#] --> B[PCIe-PCI橋] B --> C[轉換為INTx消息TLP] C --> D[Root Complex] D --> E[中斷控制器] -

??配置空間關鍵控制??

- ??Interrupt Pin寄存器??:標識設備使用的中斷引腳(0=無,1=INTA#,2=INTB#等)。

- ??Command寄存器bit3??:置1禁用INTx(僅影響傳統中斷,不影響MSI)。

? ??二、MSI/MSI-X中斷傳遞(Message Signaled Interrupts)??

-

??核心機制??

- ??內存寫入替代物理信號??:設備向Host預設的??Message Address??寫入??Message Data??,觸發Memory Write TLP提交中斷。

- ??本質辨析??:雖名為“Message”,實為??Posted Memory Write事務??,非PCIe Message TLP類型。

-

??技術優勢??

- ??無共享沖突??:每個中斷向量獨立,避免INTx的線競爭。

- ??數據一致性??:MSI寫操作與數據TLP遵從PCIe事務順序規則(同TC/VC路徑下保證先后順序)。

- ??擴展能力??:

- ??MSI??:支持32個連續中斷向量

- ??MSI-X??:支持??2048個非連續向量??,適用多隊列設備(如NVMe SSD、25G網卡)。

-

??配置與實現??

- ??Capability結構??:通過PCIe配置空間的MSI/MSI-X Capability寄存器配置地址與數據。

- ??TLP格式約束??:

- Length=1 DW,First BE=1111b,Last BE=0000b

- ??No Snoop?? 和 ??Relaxed Ordering?? 必須置0。

- ??驅動使能??:Linux中調用

pci_enable_msi()或pci_enable_msix()激活。

?? ??三、INTx與MSI/MSI-X關鍵對比??

| ??特性?? | ??INTx?? | ??MSI/MSI-X?? |

|---|---|---|

| ??觸發方式?? | 電平信號/消息模擬 | 內存寫入TLP |

| ??共享性?? | 是(易沖突) | 否(獨占向量) |

| ??最大中斷數?? | 4(INTA#~INTD#) | MSI: 32; MSI-X: 2048 |

| ??延遲敏感性?? | 高(需等待共享線釋放) | 低(直通內存寫入) |

| ??配置空間依賴?? | Interrupt Pin/Line寄存器 | MSI Capability結構 |

| ??適用場景?? | 兼容舊系統或驅動 | 高性能設備(GPU/高速網卡) |

?? ??四、設計注意事項與優化實踐??

-

??INTx的局限性??

- ??虛擬線映射復雜性??:PCIe交換機需按設備號轉換INTx消息類型(如Dev1的INTA#可能映射為上游INTB#)。

- ??電平保持問題??:中斷服務程序需手動讀取狀態寄存器確認中斷,易因異步信號導致競爭。

-

??MSI/MSI-X最佳實踐??

- ??中斷聚合??(Coalescing):合并多次事件觸發單次中斷,減少CPU負載(如網卡收包場景)。

- ??多核負載均衡??:MSI-X支持向量綁定不同CPU核心,結合

irqbalance優化響應延遲。 - ??錯誤恢復??:MSI丟失時檢查 ??Pending Bits?? 狀態,結合AER(Advanced Error Reporting)捕獲ECRC錯誤。

-

??系統兼容性??

- ??混合模式風險??:同時啟用INTx和MSI可能導致未定義行為,建議驅動中顯式禁用INTx。

- ??虛擬化支持??:MSI-X的向量隔離特性更適配虛擬化環境(如SR-IOV),避免VM間中斷干擾。

?

----- Python的數據類型及其集合操作)

)

)