一、協議概述

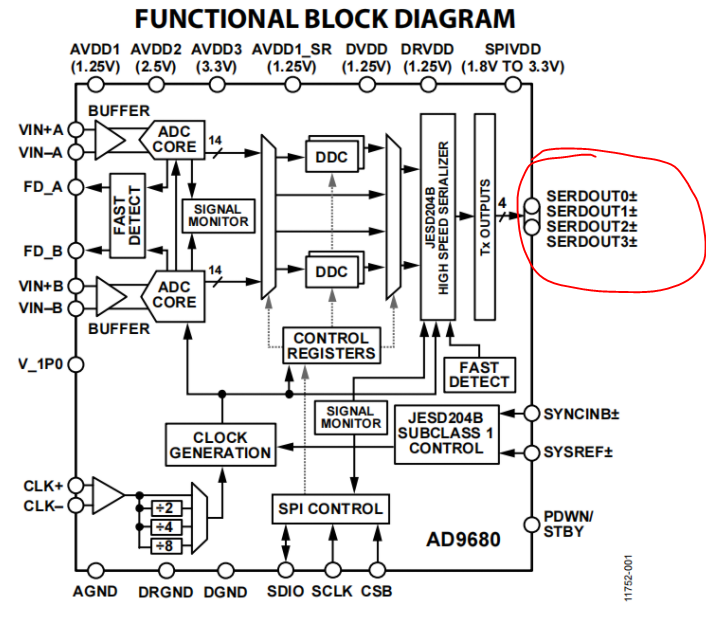

JESD204B是由JEDEC(固態技術協會)制定的高速串行接口標準,專為模數轉換器(ADC)、數模轉換器(DAC)與邏輯器件(如FPGA、ASIC)之間的數據傳輸設計。其核心目標是通過SERDES(串行器/解串器)技術實現高速、低延遲的數據傳輸,同時簡化硬件設計并降低系統成本。

二、協議架構

JESD204B采用四層架構設計,各層功能如下:

- 物理層(PHY)

- 采用CML(電流模式邏輯)電平標準,支持高速串行傳輸。

- 通過差分信號傳輸數據,抗干擾能力強,傳輸速率最高可達12.5Gbps/通道。

- 無需隨路時鐘,依賴CDR(時鐘數據恢復)技術從數據流中提取時鐘。

- 鏈路層(Link Layer)

- 數據組幀與編碼:將并行數據轉換為串行流,并添加控制位(如K碼)進行幀對齊。

- 8B/10B編碼:確保直流平衡,減少電磁干擾,同時簡化接收端時鐘恢復。

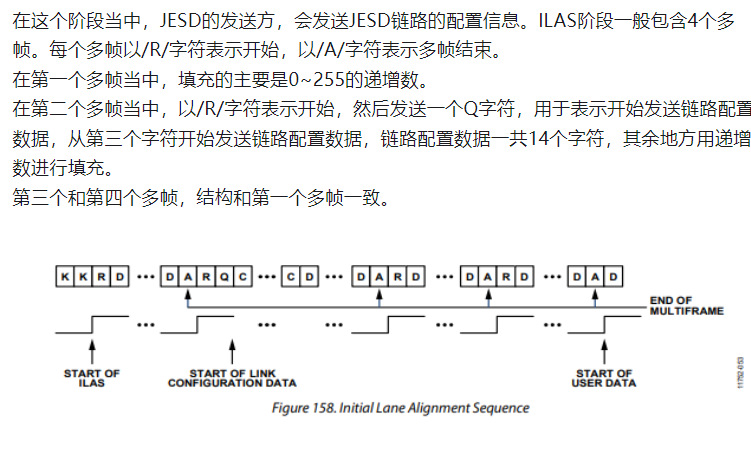

- 鏈路同步:通過CGS(代碼組同步)和ILAS(初始化通道對齊)階段建立可靠連接。

- 傳輸層(Transport Layer)

- 數據映射:將ADC/DAC的采樣數據映射為固定格式的幀結構,支持多通道對齊。

- 參數配置:通過L(通道數)、M(轉換器數)、F(每幀字節數)等參數靈活適配不同應用場景。

- 應用層(Application Layer)

- 鏈路配置:定義數據解析規則,確保發送端與接收端格式一致。

- 用戶接口:提供API或寄存器配置接口,支持動態參數調整。

三、核心特性

- 高速傳輸與低延遲

- 單通道速率最高12.5Gbps,支持多通道并行傳輸,總帶寬可達數十Gbps。

- 確定性延遲(Deterministic Latency):通過子類(Subclass)機制保證數據從發送到接收的延遲固定,適用于需要精確同步的系統(如雷達、通信基站)。

- 多通道同步與擴展性

- SYSREF信號:用于全局時鐘對齊,確保多ADC/DAC與FPGA之間的幀同步。

- 支持1-16通道并行傳輸,適應不同分辨率和采樣率需求。

- 靈活配置與兼容性

- 通過參數組合(L/M/F/S等)適配不同應用場景,例如:

- L=4, M=2, F=2:表示4通道、2個轉換器、每幀2字節。

- 兼容早期版本(如JESD204A),支持子類0/1/2三種工作模式。

- 通過參數組合(L/M/F/S等)適配不同應用場景,例如:

- 高效編碼與可靠性

- 8B/10B編碼:將8位數據映射為10位符號,確保直流平衡并簡化時鐘恢復。

- 錯誤檢測:通過奇偶校驗和幀計數驗證數據完整性。

四、技術優勢

| 特性 | JESD204B | 傳統接口(如LVDS/CMOS) |

|---|---|---|

| 傳輸速率 | 最高12.5Gbps/通道 | 通常<1Gbps |

| 引腳數量 | 顯著減少(如16位數據僅需4對差分線) | 需大量并行線(如16位需16對差分線) |

| 同步精度 | 支持確定性延遲 | 依賴硬件對齊,精度較低 |

| PCB布線復雜度 | 簡化(單層布線) | 需多層板嚴格等長 |

| 功耗 | 較高(因CDR和緩沖器) | 較低 |

五、應用場景

- 無線通信

- 5G基站、射頻前端:高速傳輸I/Q數據,支持大規模MIMO和波束成形。

- 高速數據采集

- 示波器、邏輯分析儀:實現高采樣率(GS/s級)和分辨率(14位以上)的數據捕獲。

- 醫療成像

- 超聲、MRI設備:確保實時圖像數據的無損傳輸。

- 工業自動化

- 高速控制信號傳輸,提升系統響應速度。

六、發展歷程

- JESD204(2006):初始版本,支持單通道傳輸,速率3.125Gbps。

- JESD204A(2008):引入多鏈路傳輸,提升采樣率和分辨率。

- JESD204B(2011):關鍵升級,支持確定性延遲和子類劃分,速率達12.5Gbps。

- JESD204C(2022):移除SYNC信號,僅支持Subclass 1,速率提升至32Gbps,效率進一步提升。

七、實現要點

- 硬件設計

- 選擇支持JESD204B的ADC/DAC(如TI的ADC12J4000)和FPGA(如Xilinx Kintex-7)。

- 配置高速差分對(SerDes),優化信號完整性(如阻抗匹配、等長布線)。

- 時鐘管理

- 提供低抖動參考時鐘(通常100-250MHz)和SYSREF信號,確保多設備同步。

- 鏈路初始化

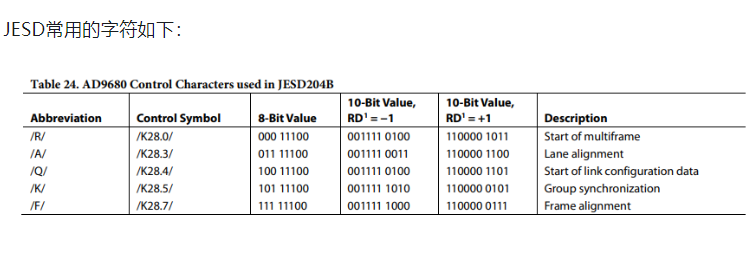

- CGS階段:通過K28.5字符對齊數據邊界。

- ILAS階段:傳輸配置信息(如L/M/F參數),驗證鏈路參數。

- 數據傳輸階段:進入正常工作模式,支持動態重配置。

- CGS階段:通過K28.5字符對齊數據邊界。

的路徑規劃(附ROS C++/Python仿真))

)

)