【學習筆記】Cadence電子設計全流程(三)Capture CIS 原理圖繪制(下)

- 3.16 原理圖中元件的編輯與更新

- 3.17 原理圖元件跳轉與查找

- 3.18 原理圖常見錯誤設置于編譯檢查

- 3.19 低版本原理圖文件輸出

- 3.20 原理圖文件的鎖定與解鎖

- 3.21 Orcad 與 Allegro 軟件交互式布局設置

- 3.22 Allegro Product Choices

- 3.23 兩份原理圖文件對比設置

- 3.24 物料 BOM 表的設置與導出

- 3.25 原理圖的 PDF 打印輸出

- 3.26 層次原理圖的概念與設計

全部內容見專欄:【Cadence從原理圖到PCB設計】

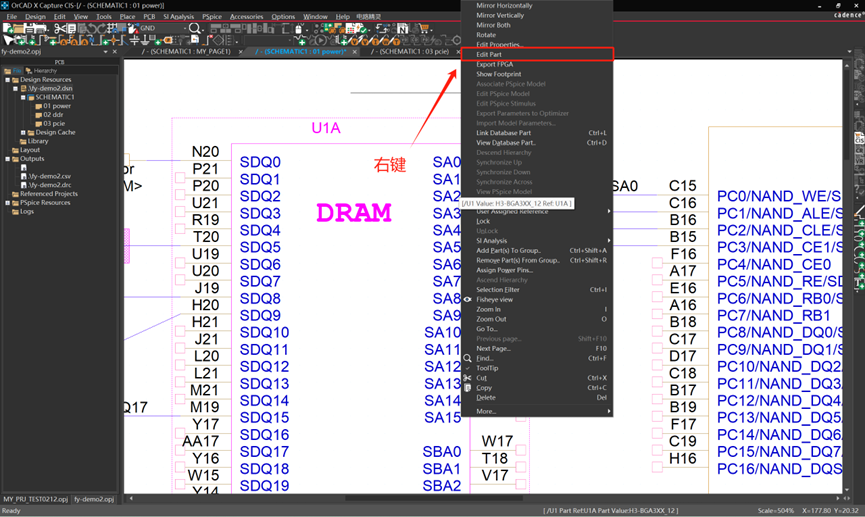

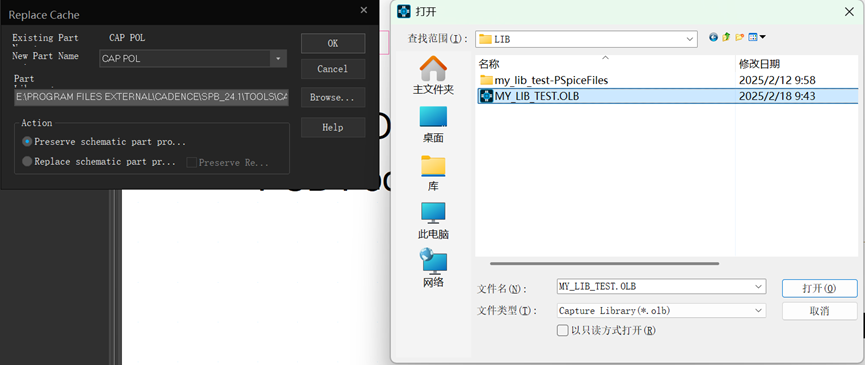

3.16 原理圖中元件的編輯與更新

方式1 在原理圖中直接更新

缺點:元器件和庫中內容是不一樣的,下一次調用庫時仍需要修改,修改只是應用于當下原理圖。

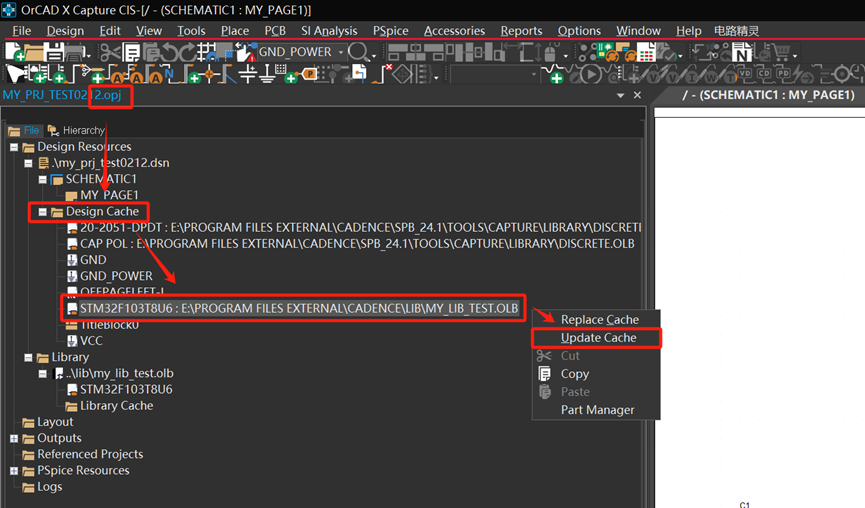

方式2 在庫中更新

找到本地庫直接打開修改后,進行更新

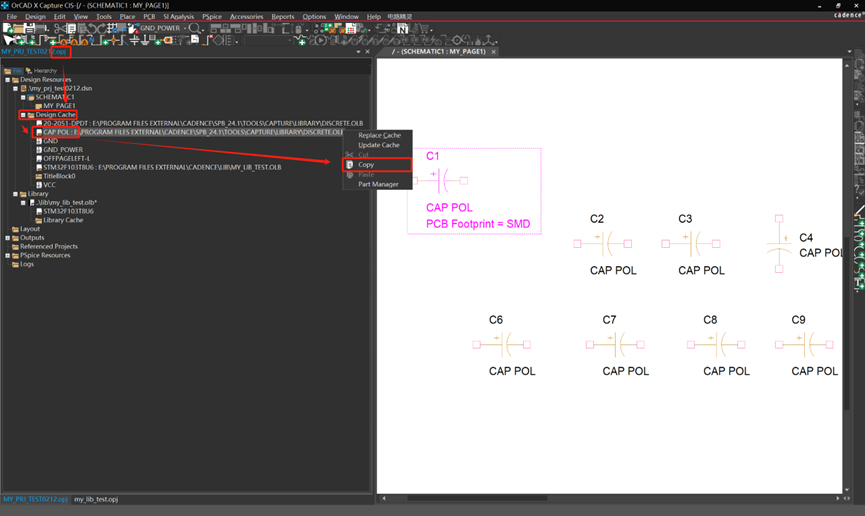

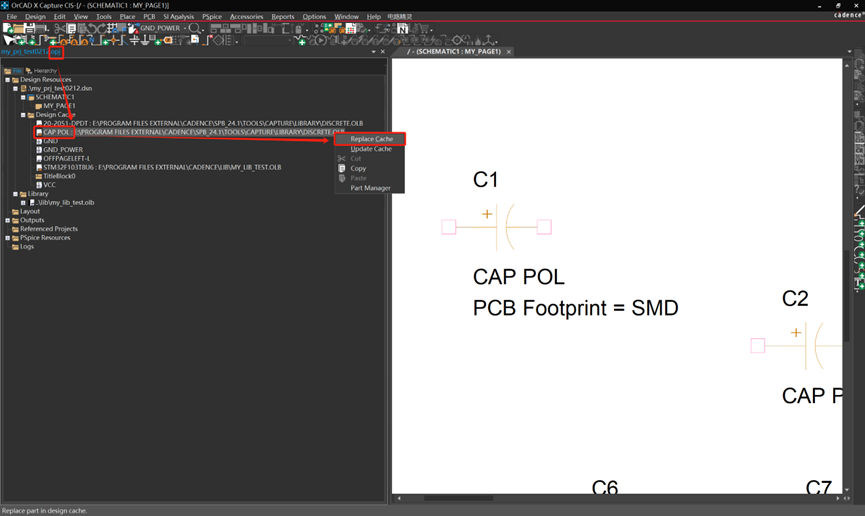

可以直接從緩存文件中復制/粘貼,找到想要提取的元器件,copy,于庫中粘貼

替換的時候,需要先替換掉庫的路徑

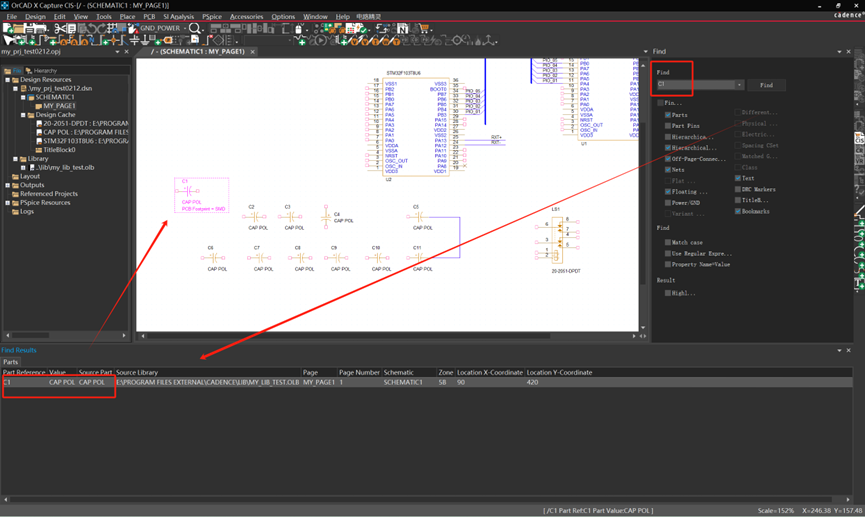

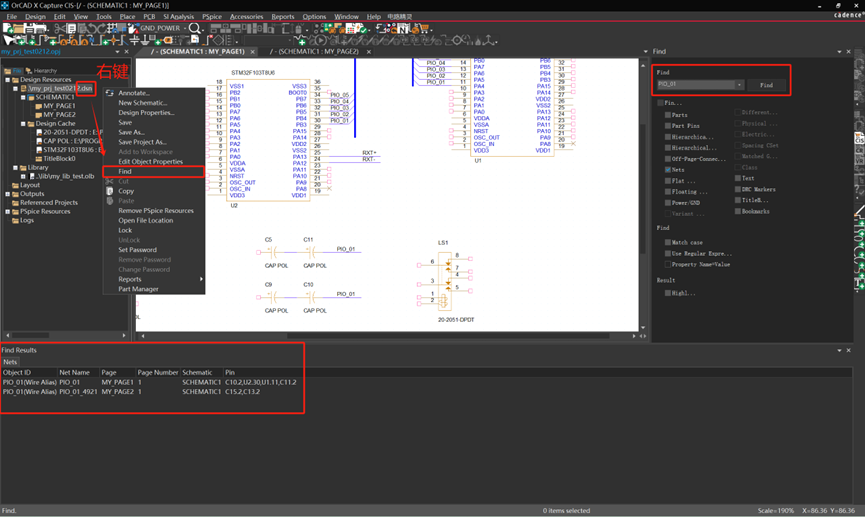

3.17 原理圖元件跳轉與查找

選擇原理圖跟目錄,進行全局查詢;或者選中某一頁原理圖,在當前頁面進行搜索,這一步操作很重要,不然沒法進行搜索

執行菜單【Edit】→【Find】命令,或者按快捷鍵【Ctrl+F】進行查找,彈出原理圖的搜索框進行搜索跳轉

在搜索框中輸入所要搜索的位號字符等,點擊Fimd按鈕在左下角的窗口中雙擊找到的結果即可高亮并定位到器件位置

搜索完成以后,軟件會自動彈出該元素所在的界面,若該元素有很多個,則下面會有一個列表,點擊即可跳轉,如圖所示,若沒有該元素,則不會有界面彈出

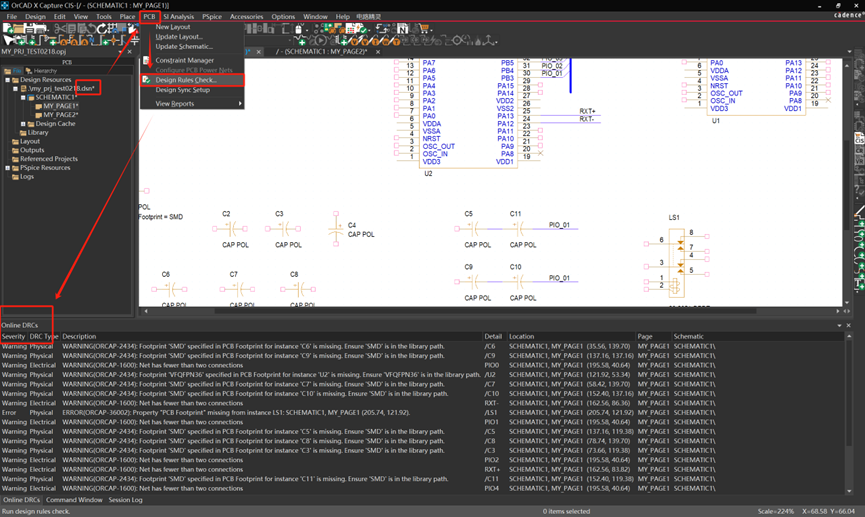

3.18 原理圖常見錯誤設置于編譯檢查

在輸出網表與PCB設計之前,進行DRC檢測

| Check 事項 | 含義 |

|---|---|

| Check single node nets | 檢查設計中的單端網絡 |

| Check no driving source and pin type… | 檢查器件屬性無源管腳與有源管腳的連接是否正確 |

| Check duplicate net name | 檢查重復的網絡名稱 |

| Check off-page connector connect | 檢測分頁圖紙間接口的連接性 |

| Check hierarchical port connection | 檢測階層端口的連接性 |

| Check unconnected bus net | 檢測沒有連接的總線網絡 |

| Check unconnected pins | 檢查沒有連接的管腳 |

| Check power pin visible | 檢測電源屬性的管腳是否顯示了管腳名稱與編號 |

| Check missing/illegal PCB Footprint | 檢測封裝名稱是否填寫。是否含有非法字符 |

| Check Normal convert view system | 檢測一個部件的正常視圖上的pin號是否與轉換視圖上的pin號不同 |

| Check incorrect pin group assignment | 檢查同一個Pin Group的所有插腳是否有相同的類型 |

| Check high speed props syntax | 在設計中檢查網絡高速屬性的語法是否正確 |

| Check missing pin number | 檢測缺失管腳編號的管腳 |

| Check device with zero pins | 檢測設計中是否含有零寬度的管腳 |

| Check power ground short | 檢測一個Part內部的電源網絡名稱是否有兩個不同的網絡標號名稱 |

| Check Name Prop consistency | 檢測層次原理結構中是否含有相同的網絡名稱 |

| Report all net name | 報告所有網絡的名稱 |

| Report off-grid object: | 報告不在格點上是器件 |

| Report hierarchical ports and off-page connection | 報告階層端口和分頁圖紙間接口的連接 |

| Report Misleading Tap Connection | 報告易誤解的連接 |

| Report Visible unconnected power pins | 報告所有具有可見電源屬性的管腳是否有連接 |

| Report unused part packages | 報告原理圖中未使用的器件part |

| Report invalid Refdes | 報告原理圖中無效的器件位號 |

| Report identical part references | 報告原理圖相同的位號 |

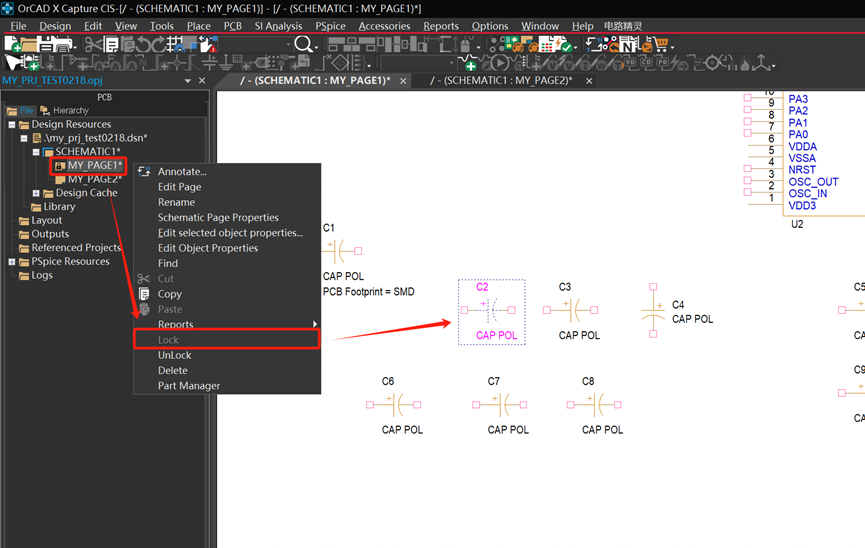

3.19 低版本原理圖文件輸出

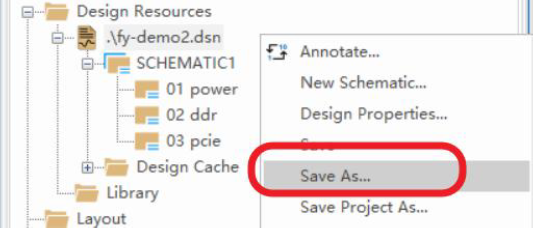

需要選中降低原理圖的根目錄就是DSN文件,如圖所示選中之后,點擊鼠標右鍵,SaveAs,就可以存為低的版本

在彈出的界面中,在保存類型那一欄可以選擇低的版本,般是存為16.2的版本,這樣就存為了低的版本了

這里可以看到有這樣的一個情況,就是Orcad存為低的版本的時候,只能存為一個版本,那就是16.2的版本。其實在Orcad設計的時候,16.2之前的版本,機制都是通用的,都可以打開,16.2以后版本的機制是一樣的,所以存為低版本的時候,是以16.2為分界點來處理就可以了

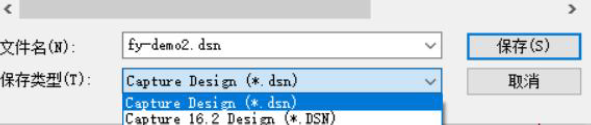

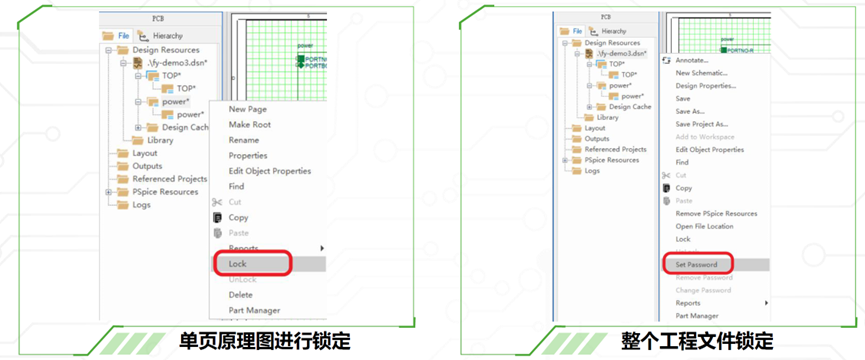

3.20 原理圖文件的鎖定與解鎖

選中圖紙點擊右鍵LOCK即可鎖定。工程可設置密碼。

防止PCB工程師誤操作。

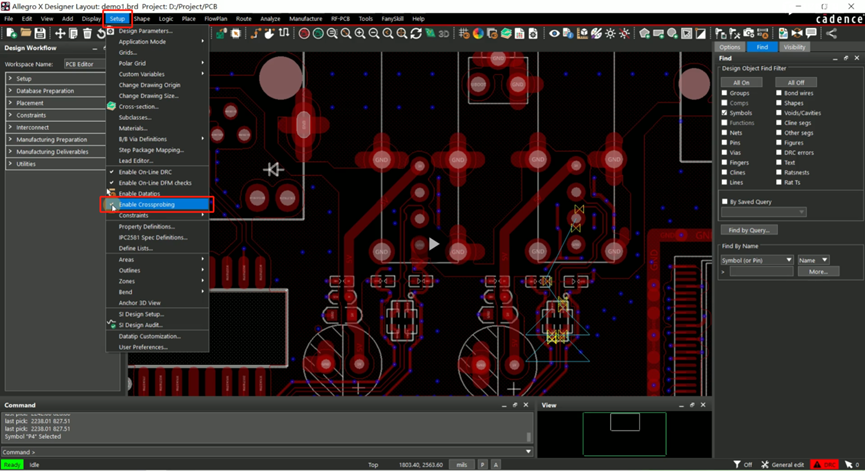

3.21 Orcad 與 Allegro 軟件交互式布局設置

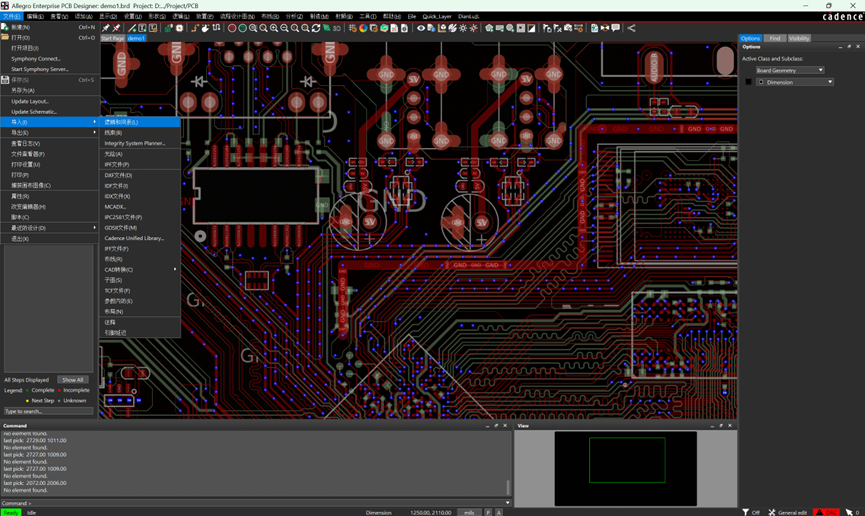

在做pcb設計的時候,原理圖選中一個元器件,PCB中可以直接選中。

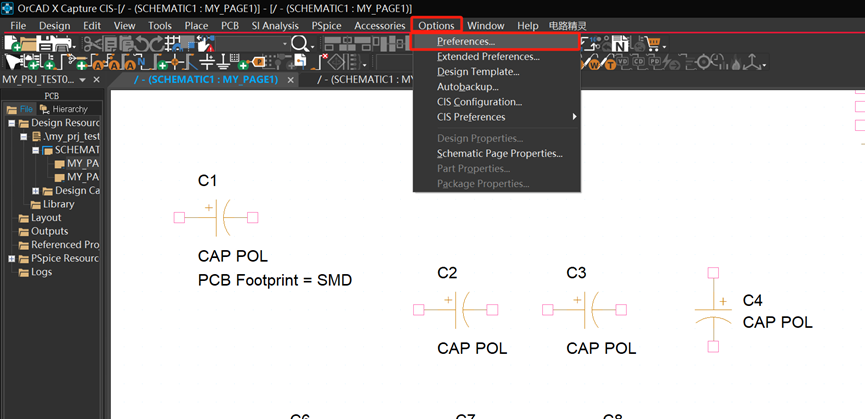

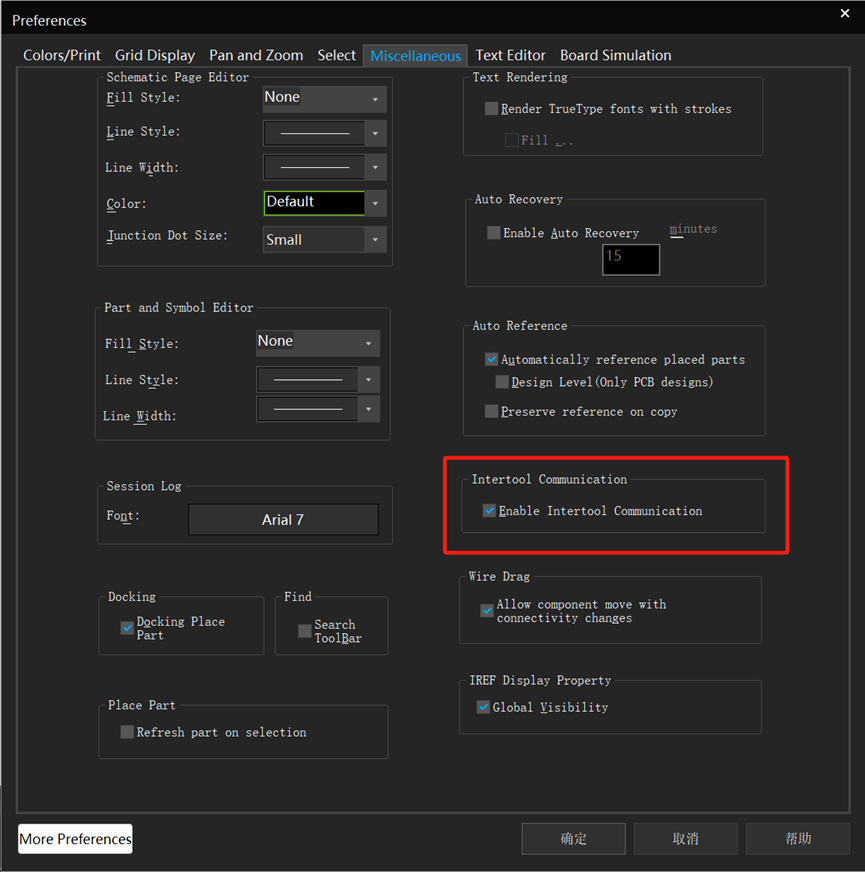

- 為了達到原理圖和PCB兩兩交互,需要在ORCAD中將允許交互進行勾選,執行菜單命令Options-Preference,打開參數界面,選擇Miscellaneous菜單,將交互模式進行勾選;

- 使能交互式布局

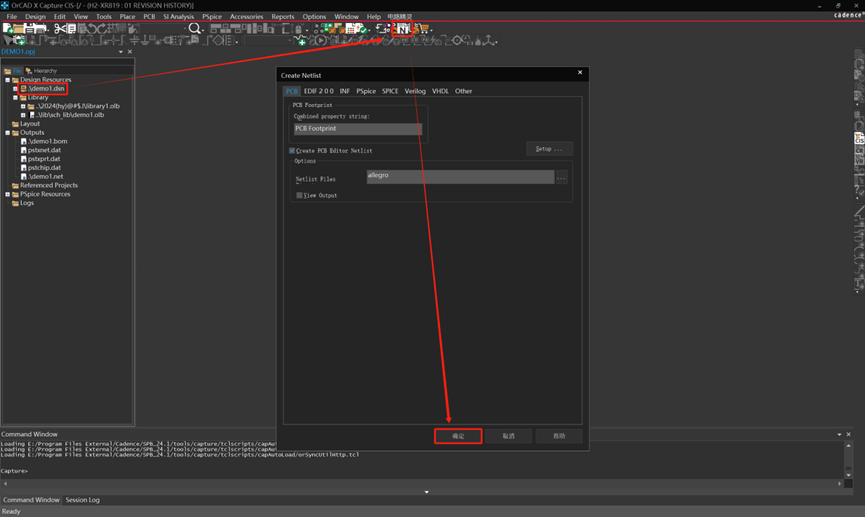

- 網表必須是導入第一方網表,第三方無效;

- 在allegro中使能/關閉交互式布局功能

- 當前兩個步驟完成后,原理圖與PCB的交互就已經完成,在原理圖選中器件在PCB中進行交互的時候,需要先在PCB中執行MOVE命令,PCB中相應器件才會被選中;

- 在PCB選中器件在原理圖中進行交互的時候,需要先在PCB中執行高亮命令,原理圖中相應器件才會被選中

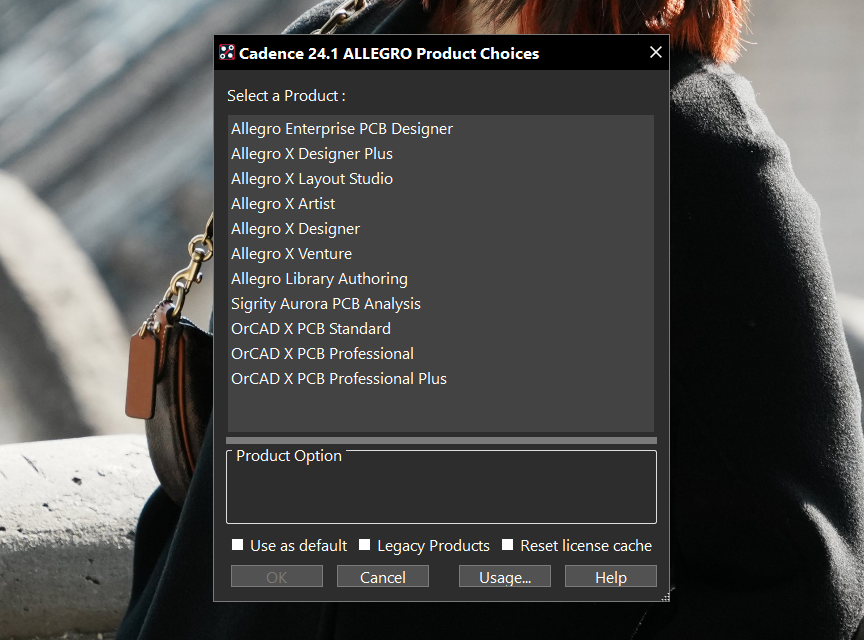

3.22 Allegro Product Choices

在 Cadence Allegro 中打開 PCB 文件時,如果出現“Allegro Product Choices”對話框,并且列出了多個選項(如你提到的這些),選擇哪個取決于你的具體需求和許可證權限。

以下是這些選項的詳細說明,幫助你做出選擇:

| Allegro Product Choices | 功能/適用場景 |

|---|---|

| Allegro Enterprise PCB Designer | 這是 Allegro 的最高版本,包含所有高級功能,如高速設計、約束管理、信號完整性分析、電源完整性分析等。適合復雜的高速 PCB 設計,尤其是需要高級仿真和分析的項目。 |

| Allegro X Designer Plus | 提供完整的設計功能,包括布局、布線、約束管理等,但可能缺少一些企業版的高級功能。適合中高復雜度的 PCB 設計。 |

| Allegro X Layout Studio | 專注于 PCB 布局和布線,適合中小型項目。適合不需要高級仿真和分析的常規 PCB 設計。如果你的設計復雜度較低,可以選擇這個。 |

| Allegro X Artist | 提供基本的 PCB 設計功能,適合初學者或小型項目。適合簡單的 PCB 設計任務。如果你的設計需求較簡單,可以選擇這個。 |

| Allegro X Designer | 提供標準的設計功能,包括布局、布線和約束管理。適合中等復雜度的 PCB 設計。如果你需要標準的設計功能,可以選擇這個。 |

| Allegro X Venture | 這是一個入門級工具,功能較為基礎。適合非常簡單的 PCB 設計或學習用途。如果你的設計需求非常基礎,可以選擇這個。 |

| Allegro Library Authoring | 專門用于創建和管理元件庫(封裝、符號等)。適合需要創建或編輯元件庫的場景。如果你只需要編輯元件庫,選擇這個。 |

| Sigrity Aurora PCB Analysis | 專注于 PCB 的信號完整性(SI)、電源完整性(PI)和熱分析。適合需要進行仿真和分析的項目。如果你需要仿真分析,選擇這個。 |

| OrCAD X PCB Standard | OrCAD 的標準版本,提供基本的 PCB 設計功能。適合中小型項目。如果你習慣使用 OrCAD,且設計復雜度較低,可以選擇這個。 |

| OrCAD X PCB Professional | OrCAD 的專業版本,提供更多高級功能,如約束管理和高速設計支持。適合中高復雜度的 PCB 設計。如果你需要更多功能,且習慣使用 OrCAD,可以選擇這個。 |

| OrCAD X PCB Professional Plus | OrCAD 的最高版本,包含所有高級功能,如信號完整性分析和高速設計支持。適合復雜的高速 PCB 設計。如果你需要全面的功能,且習慣使用 OrCAD,可以選擇這個。 |

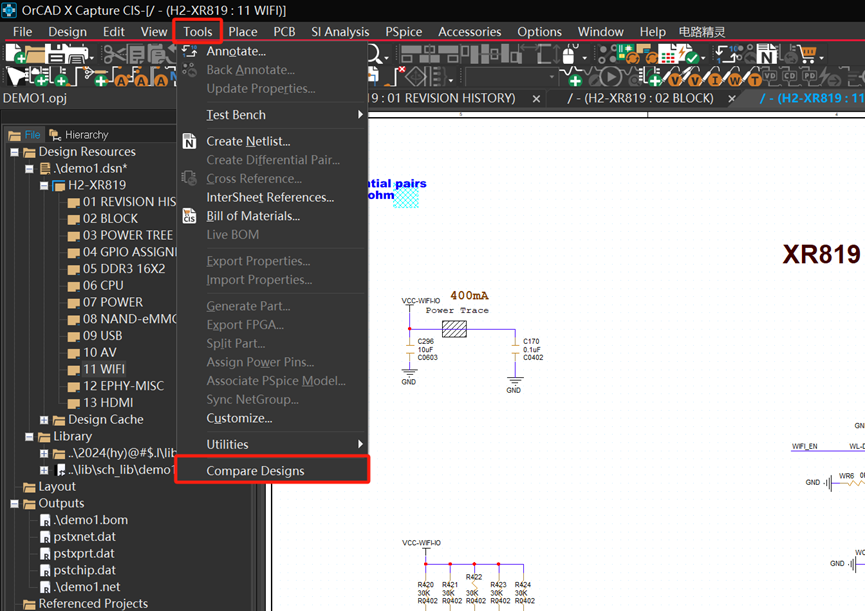

3.23 兩份原理圖文件對比設置

要對比兩份原理圖的差別,查看那里進行了改動。

選擇Tools-Compare Designs就可以開啟DSN設計差異對比的功能

Schematic,Page可以設置對比的范圍其目的就是能夠設置對部分原理圖文件或者所有的原理圖頁面進行對比,方便工程師進行差異化的選擇對比。

Output選擇欄目里面可以對輸出的參數進行配置,HTMLPath需要注意不要有中文路徑,非法的字符等。指定的目錄需要有讀寫權限。

Compare對比開啟后,就會彈出Design Difference Summary顯出差異的報告。

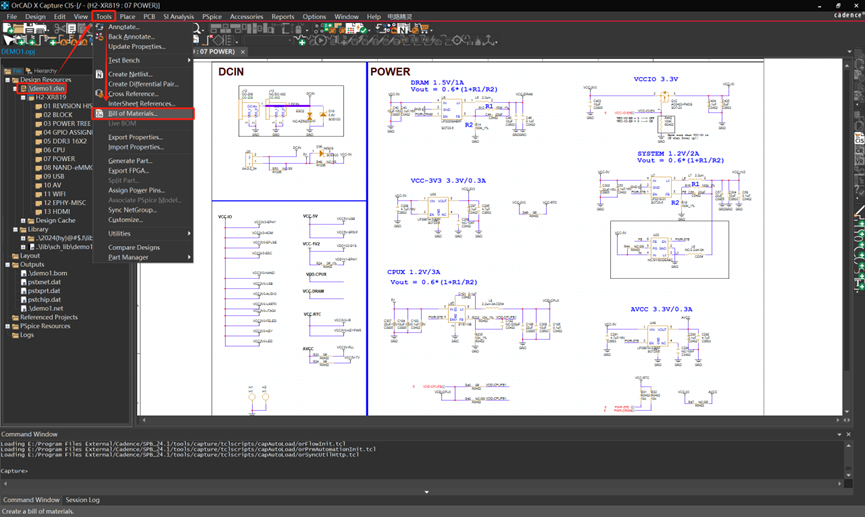

3.24 物料 BOM 表的設置與導出

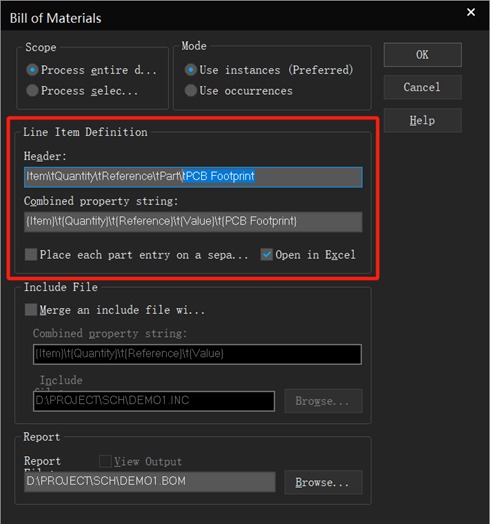

- 選中.DSN根目錄以后,執行菜單命令Tools-Bi1lof Materials…命令,來進行B0M清單的輸出

- 在Header以及Combined Property String欄中,分別列出了需要輸出的元素,依次是器件的數量、器件的位號、器件的屬性值;

- 缺失器件的封裝屬性值,需要單獨加上,格式就是跟Header以及Combined Property String致,勾選上Open in Excel,這樣輸出BOM清單就用EXCEL表格打開了,進行編輯整理,得到需要的BOM清單。

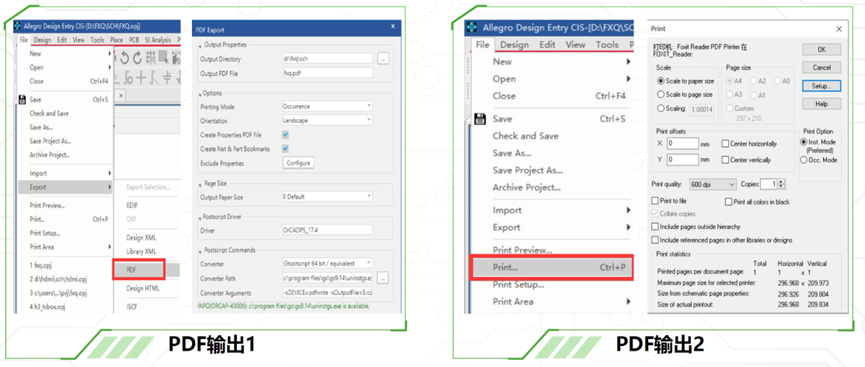

3.25 原理圖的 PDF 打印輸出

3.26 層次原理圖的概念與設計

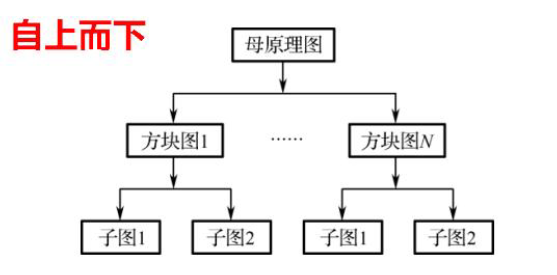

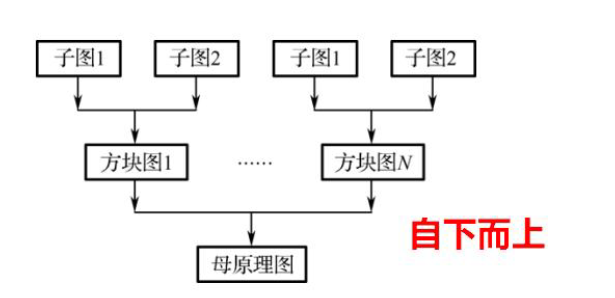

層次原理圖就是把完整的電路系統按照功能劃分為若干子系統,即子功能電路模塊。這樣,設計人員就可以把每一個子功能電路模塊的相應原理圖繪制出來,然后在這些子原理圖之間建立連接關系,從而完成整個電路系統的設計。

層次原理圖設計的概念很像文件管理樹狀結構,設計者可以從繪制電路母原理圖(簡稱母圖)開始,逐級向下繪制子原理圖(簡稱子圖);也可以從繪制基本的子原理圖開始,逐級向上繪制相應的母原理圖。因此,層次原理圖的設計方法可以分為兩種,即自上而下的層次原理圖設計方法和自下而上的層次原理圖設計方法。

-

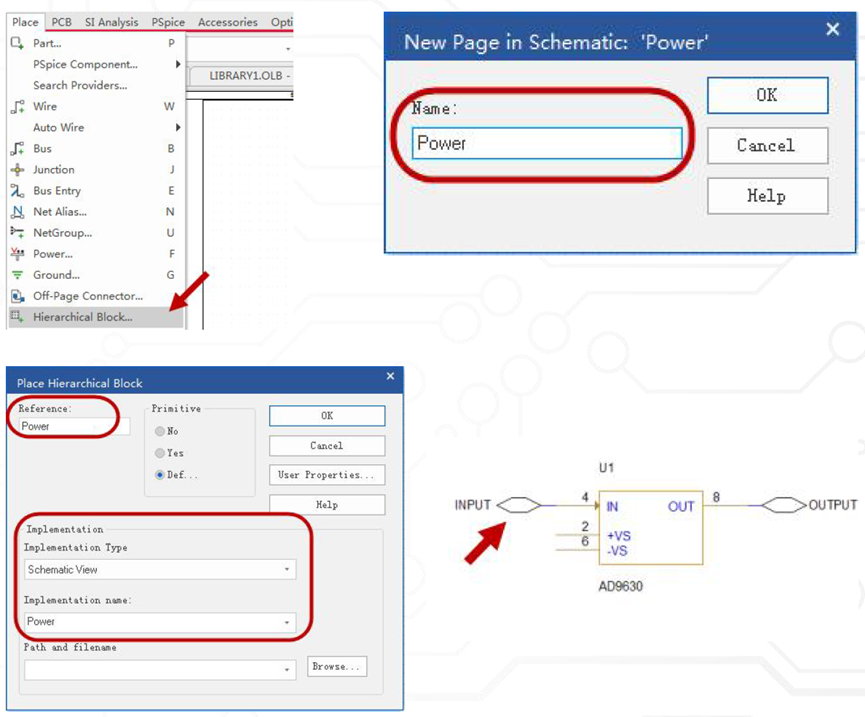

創建分級的模塊Hierarchical Block,在原理圖設計的頁面,執行命令Place>Hierarchical Block…

-

在彈出的對話框中,輸入分級模塊的名稱,如圖所示,選擇合適的參數,一般如圖所示設置即可,點擊OK,則層次式原理圖分級模塊創建完畢

-

在原理圖頁面畫出合適的分級模塊框框的大小這個也可以后面進行調整,用于分配子端口的以及總線的位置

-

雙擊新生成的圖框,或者選中圖框進行右擊選擇Descend Hierarchy,進行子圖的設置在彈出來的對話框中填寫原理圖頁面名,然后點擊“OK”按鈕,如圖所示,設置子圖的原理圖頁的名稱

-

在新生成的原理圖頁面中進行原理圖的子圖繪制設置,并放置好與總框圖的接口Hierarchical Port

-

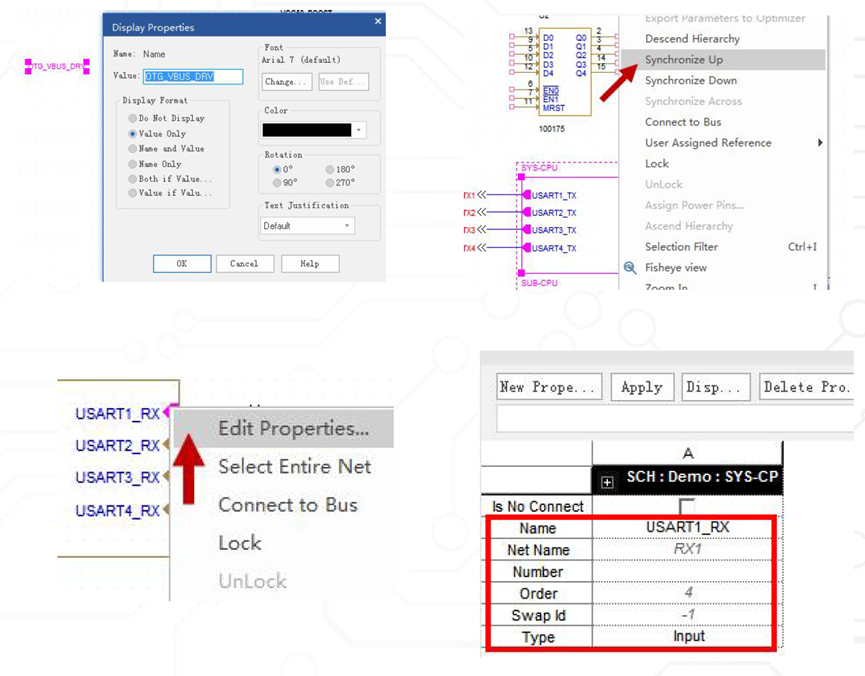

雙擊放置的Hierarchical Port名,修改其名稱,點擊“OK”退出

-

然后返回到放置Hierarchical Block的頁面,選中已放置好的框并右擊選取Synchronize Up,然后在此框邊緣會出面子原理圖頁面中的Hierarchical Port,如圖所示

-

選取需修改的Hierarchical Port右擊選取Edit Properties進行編輯,如圖所示

-

在彈出來的對話框對其屬性進行修改,然后保存退出即可,如圖所示,這樣我們的層次原理圖的模塊就繪制完畢了。

最后

更多內容見專欄:【硬件設計遇到了不少問題】

Cadence 筆記傳送門:【Cadence從原理圖到PCB設計】

商品詳情 API 接口概述及 JSON 數據返回參考)

(純命令))