13.8 RFSoC上PYNQ的SDR設計流程

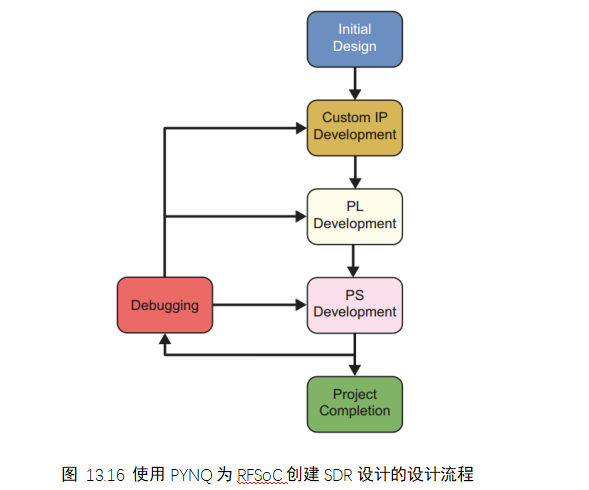

本節中詳細介紹的設計過程可以分為六個獨立的步驟,如圖13.16所示,并在接下來的幾頁中進行討論。

13.8.1 初始設計過程

。在這里,系統設計人員必須考慮許多因素,例如RFDC接收和/或發送的頻率范圍,以及這些信號的帶寬。這一步也應該使用頻率規劃,以確定所需的配置是否會導致任何帶內干擾。這些因素將決定在設計中使用所需的采樣率和時鐘率。例如,如果信號帶寬遠小于RFDC所需的采樣率,則可以使用插值或抽取級來降低PL上的時鐘速率。然而,如果需要大帶寬,則可能需要使用SSR來滿足PL時間限制。

另一個需要考慮的因素是FPGA上IP之間的通信,以及PL和PS之間的通信。Vivado中提供的許多IP都是兼容AXI的,因此對于任何自定義IP也采用兼容AXI的接口往往是有益的。如果要在PS和PL之間傳遞大量數據,則可能需要AXI流 DMA,而對于低帶寬信號,AXI - Lite接口通常就足夠了。

在這個階段考慮如何構建PS軟件以及如何與PL硬件交互是很重要的。AMD為其IP提供了許多可以從PS控制的驅動程序,例如AXI DMA。如果要開發自定義IP,那么可能還需要為它們開發自定義驅動程序。

此外,如果設計需要使用AXI - Lite控制信號,那么PL硬件必須符合AXI - Lite標準并適當地處理它們。

13.8.2 定制IP的開發

下一步是開發和測試在FPGA上運行的定制IP。作者在這個階段的首選工具是模型編寫器和HDL編碼器,兩者都在MATLAB/Simulink環境中運行。使用Simulink使系統設計人員能夠在將IP功能集成到Vivado設計之前快速模擬和測試IP功能,例如,可以利用Simulink源塊為仿真提供適當的刺激,并且可以使用Sink塊來可視化時間和頻域的結果。這兩個工具都能夠在它們生成的IP中合并符合AXI的端口。

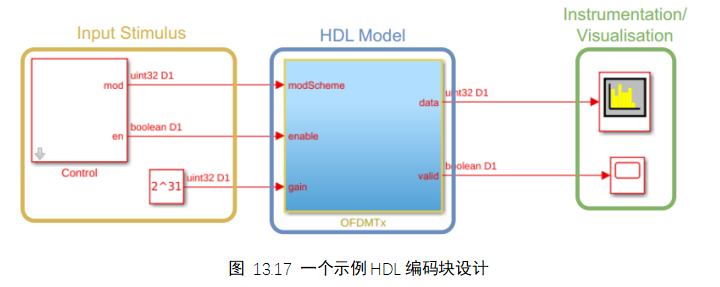

如圖13.17所示為HDL Coder設計示例,突出顯示了構成IP核的HDL模型,以及輸入刺激的生成和輸出信號的檢測。

Simulink中的時鐘使用采樣時間(換句話說,采樣周期)的概念,這是采樣率的倒數。因此,采樣時間參數是指IP所需的時鐘速率。

一般情況下,單個時鐘驅動IP的所有接口,設置為匹配所需的采樣率。如果在自定義IP中需要任何速率更改,那么必須注意IP必須由以最高采樣率運行的時鐘驅動,這一點很重要。然后,這些工具在IP內生成其他時鐘,以驅動以較低采樣率運行的塊;所需的采樣率(以及時鐘速率)通常與整數因子相關。

在設計定制IP時,重要的是要考慮輸入和輸出,以及它們如何與更廣泛的設計交互。如前所述,使用AXI標準是值得考慮的,它將允許這些IP與Vivado中其他兼容AXI的IP很好地協同工作。AXI流可用于通過處理鏈傳遞RF數據,而AXI- Lite可用于控制信號,例如啟用和復位。

Simulink提供信號范圍和頻譜分析儀工具,允許系統設計人員在將模型轉換為HDL IP之前測試和驗證模型的功能。頻譜分析儀對于確定信號數據是否被正確處理非常有用,而信號范圍可用于識別軸流接口信號的問題。

13.8.3 自定義IP集成到Vivado,硬件系統設計

一旦開發和測試了自定義IP,就可以將它們導入到Vivado并集成到完整的PL設計中。這一步可能是最關鍵的,因為它要求系統設計人員對底層硬件及其功能有很好的理解。在Vivado中,系統設計人員將MATLAB/Simulink中設計的自定義IP與RF數據轉換器等其他IP之間的接口連接起來;以及PL和PS之間的任何溝通。

此外,這是在設計中設置時鐘速率和采樣速率的地方。必須小心確保每個IP都由正確的時鐘驅動,否則可能會出現意外行為,并且難以調試。本書中的大多數設計都是從三個獨立的時鐘源運行的:(i) PL時鐘,用于驅動AXI- Lite接口;(ii) DAC時鐘,驅動與傳輸路徑相關的IP;(iii) ADC時鐘,它驅動接收路徑上的ip。在某些情況下,可能需要使用時鐘轉換器來生成ip所需的頻率。

創建PL設計的最直接方法,也是作者所采用的方法,是使用Vivado的內置IP Integrator工具。IP集成商允許系統設計人員使用可視化的、基于塊的方法將IP連接在一起。

硬件系統設計人員最終會遇到的一個問題是時序關閉,即確保設計能夠支持所需的時鐘速率。對于SDR設計,這可能涉及在接收器的信號處理鏈中較早地抽取信號,或者相反,在發射器的信號處理鏈中較晚地插值。另一個選擇是更改Vivado中的實現策略,它定義了放置和路由的方法。Vivado定義了許多不同的策略,包括一些主要關注定時關閉的策略(通常具有延長的運行時間,但有可能獲得更好的結果)。

13.8.4 PS軟件的開發

在PL設計完成后,就可以開發PS的軟件了。從本書中的各種設計中可以明顯看出,PYNQ是作者在PS上開發軟件的首選框架。使用PYNQ有許多好處,包括對標準IP的良好驅動程序支持,以及為自定義ip創建驅動程序的簡單方法。使用Python還可以快速有效地編寫代碼,從而相對快速地識別PL和PS上的任何問題。此外,Python生態系統包含無數已建立的庫,例如Plotly和SciPy,這使得直接在PS上開發用于可視化和分析信號的代碼變得簡單。

由于其易用性,PYNQ提供了一種快速的方法來確認PL設計是否按預期執行。AXI - Lite寄存器可以使用MMIO庫進行讀寫,RFDC驅動程序可用于配置RF數據轉換器,DMA驅動程序使通過共享內存在PS和PL之間傳遞數據變得簡單。如果數據僅在PL和RFDC之間傳遞,則可能需要在PL上運行集成邏輯分析儀(ILAs)或外部設備(如頻譜分析儀和/或信號發生器)來驗證發送和接收路徑的功能。

13.8.5 調試

正如調試過程中常見的那樣,解決方案通常很簡單,但是確定故障的位置可能非常耗時。幫助這個過程的一個有用工具是Python調試器PDB,它允許用戶設置斷點并有條不紊地逐步執行PS代碼。一旦發現并修復了錯誤,就可以從項目中刪除調試器代碼。

如果確認PS軟件按預期運行,則可能需要重新訪問PL設計階段以解決問題。根據PL設計的大小,生成一個新的比特流可能需要很長時間,因此,PL調試可能是一個耗時的過程,特別是如果需要多次重新生成比特流,以嘗試不同的解決方案。出于這個原因,在進入軟件開發階段之前,廣泛地模擬和測試PL硬件是有益的。

雖然在設計中可能存在許多不同的故障,但根據我們的經驗,在為RFSoC開發系統時可能會出現兩個常見問題。正如本節前面所討論的,不正確的時鐘頻率可能導致不可預測的行為。RFDC通常由外部時鐘基礎設施驅動,因此確保時鐘的正確編程以及它們提供預期的頻率非常重要。

另一個常見問題來自于如何在自定義IP中生成和處理AXI流信號。除了tdata信號外,AXI流IP還可以包含各種其他接口信號,包括tvalid、tready和包結束信號tlast。如果這些信號沒有與tdata信號正確同步,那么沿著信號路徑進一步的IP可能無法正確操作。例如,在設置數據傳輸時,PYNQ DMA驅動程序要求數據包大小具有特定的長度。如果最后一個信號脈沖太早或太晚,指示數據包的結束,這將導致DMA掛起。如果處理不當,trready信號也會出現類似的問題。

13.8.6 項目完成

一旦PS和PL被驗證工作如預期,軟件就可以形式化。這可能包括為自定義IP制作驅動程序,或者(如果適合預期用例)創建刺激或可視化工具,例如本書中的許多設計。在這些設計中廣泛使用的另一種可能性是,將大部分功能抽象為類和函數,然后將它們導入到Notebook中。這使得Jupyter Notebook中的代碼更加精簡,更容易理解。

G Notebook Set G——RFSoC無線電演示器

G.1 無線電系統

01_rfsoc_radio_system.ipynb探索了發射器和接收器的無線電通道,為用戶提供了底層無線電體系結構的概述。這包括研究xrfdc Python包,它負責配置RFSoC的數據轉換器。我們還將使用另一個重要的包xrfclk,它配置RFSoC的時鐘網絡。用戶還將被介紹到無線電儀表板,這是一個圖形用戶界面,控制系統。無線電系統架構示意圖如圖G.1所示。

本手冊介紹了發送端向接收端發送數據時使用的數據幀的結構,它作為一種簡單的通信協議。圖G.2顯示了RFSoC無線電演示器使用的數據幀結構。注意,數據幀有三個主要部分:序言、報頭和有效負載。通常發射機發送一個已知的比特序列(前導),接收器使用同步技術檢測到它。在此之后,諸如幀號、數據標志和幀長度等附加信息將包含在報頭中(稍后將提取這些信息并由接收方用于解釋幀)。有效載荷是指幀所攜帶的數據。

G.2 觀察無線電通道

在介紹RFSoC無線電設計之后,我們將開始觀察系統運行時的發送和接收無線電管道。這包括通過從發射器和接收器管道的各個階段進行“抽查”來對無線電系統進行實時內省,即在不影響其來源的處理管道的情況下提取內部信號的副本進行分析。然后使用這些信號生成波形以進行可視化(示例圖如圖G.3所示)。可以通過運行02_rfsoc_radio_observe.ipynb開始觀察無線電通道。

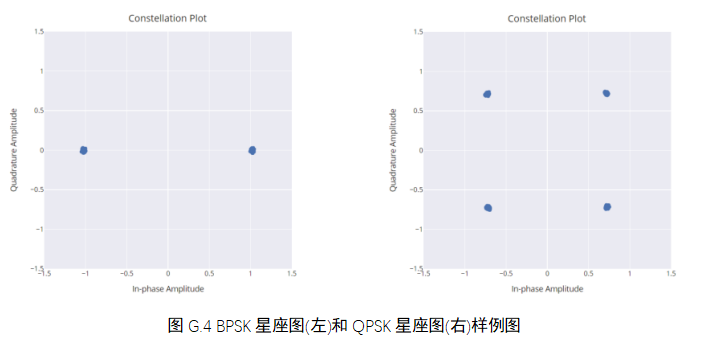

我們還將研究兩種數字調制方案的使用:二進制相移鍵控(BPSK)和正交相移鍵控(QPSK)。可以在系統運行期間在BPSK和QPSK之間切換,并繪制接收到的星座圖,理想情況下應該類似于圖G.4所示的星座圖。

G.3 發送和接收:“Hello World!”

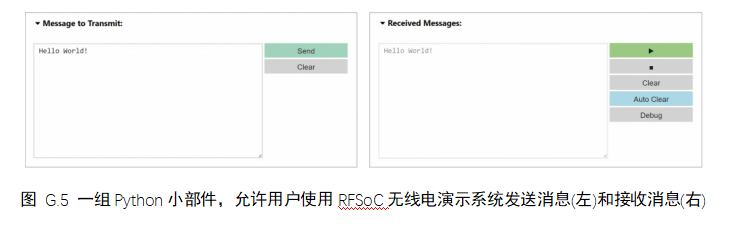

首先,打開并運行名為03_rfsoc_radio_helloworld.ipynb的Notebook。這個例子將使用RFSoC無線電系統發送一個“Hello World!”的信息在發射器和接收器之間傳遞。我們將使用三種不同的技術發送此消息。第一個方法使用一個簡單的函數調用來發送“Hello World!”第二種方法使用Python小部件,允許您使用按鈕和文本窗口輕松地輸入和傳輸消息(此應用程序的示例如圖G.5所示)。第三個方法允許您廣播“Hello World!”消息反復使用Python線程庫。

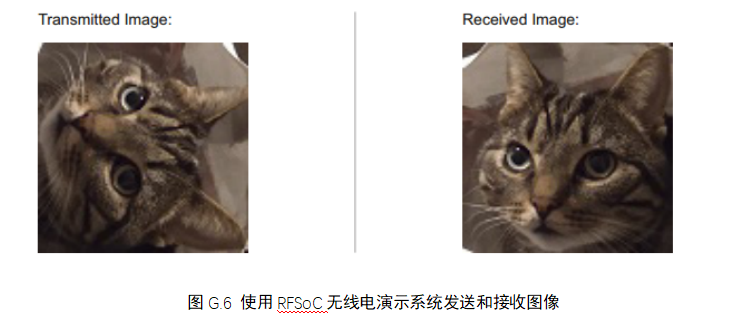

本Notebook Set的最后一部分允許您使用RFSoC無線電演示系統發送和接收圖像。無線電系統重復傳輸圖像,每次成功傳輸后將圖像旋轉90°。在本演示中,您可以選擇BPSK和QPSK調制方案進行傳輸。圖像發送和接收RFSoC演示系統的示例輸出如圖G.6所示。

精彩文章,請關注訂閱號:威視銳科技

)

![[Linux系統編程]進程間通信—system V](http://pic.xiahunao.cn/[Linux系統編程]進程間通信—system V)

用于將笛卡爾坐標(x, y)轉換為極坐標(magnitude, angle)函數cartToPolar())

)

| 零基礎入門STM32第九十二步)