計組TEC4實驗——運算器組成實驗

1. 實驗目的

(1)掌握算術邏輯運算加、減、乘、與的工作原理。

(2) 熟悉簡單運算器的數據傳送通路。

(3) 驗證實驗臺運算器的8位加、減、與、直通功能。

(4) 驗證實驗臺的4位乘4位功能。

(5) 按給定數據,完成幾種指定的算術和邏輯運算。

2. 實驗平臺

TEC-4計算機組成原理實驗系統

8 位計算機模型實驗系統,采用了數據總線和指令總線雙總線機制

3. 實驗準備——接線

4. 實驗內容 1

-

將 01010101B 置入 DR1

-

將 10101010B 置入 DR2

-

進行直通運算

-

進行加法運算DR1+DR2=11111111B

5. 實驗內容2

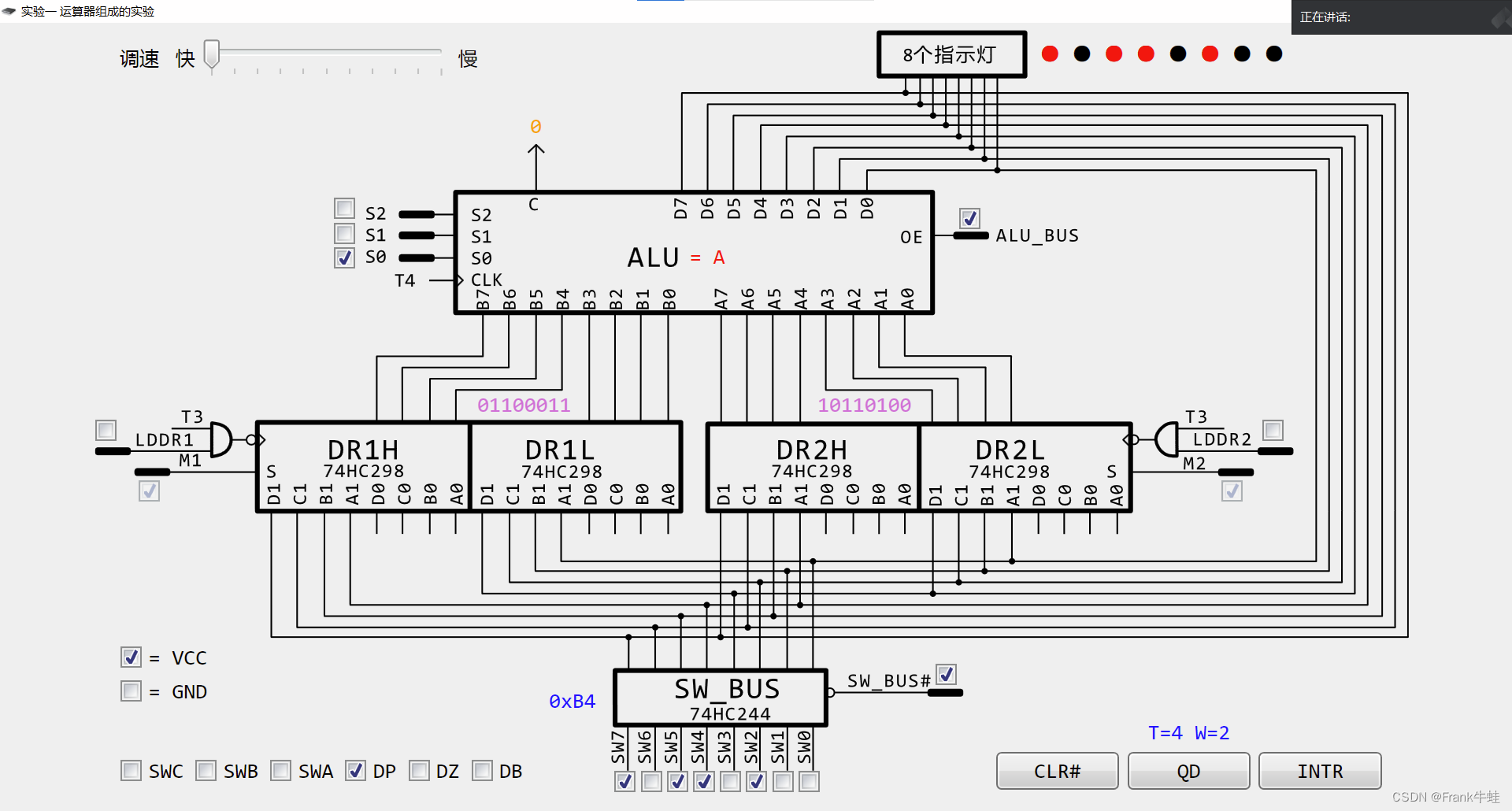

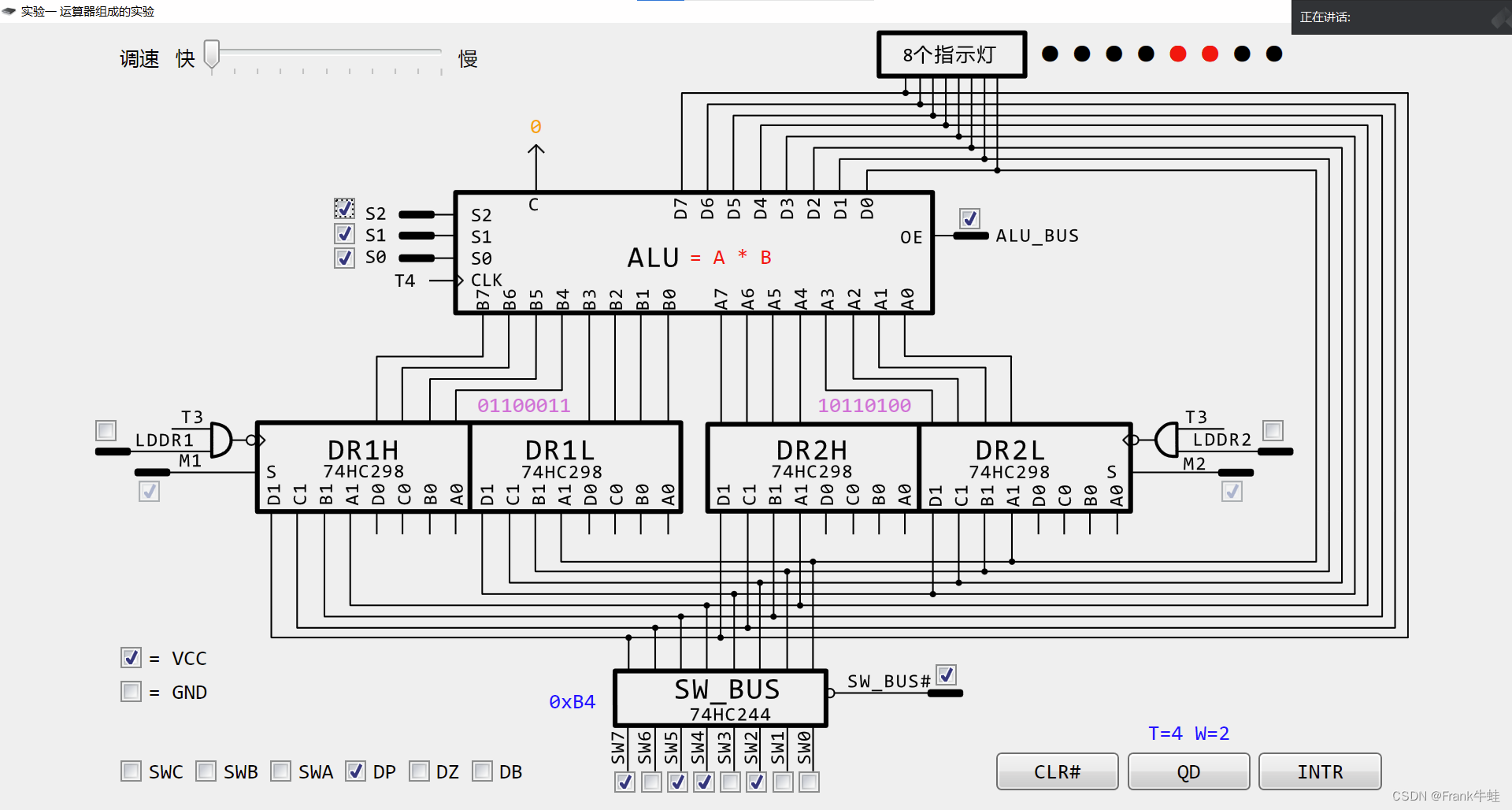

- DRl=01100011B,DR2=10110100B

直通

- 對結果(數據和進位)進行分析

6. 實驗內容3

-

將A、B中的內容互換。

-

DRl=01100011B,DR2=10110100B則交換后為DRl=10110100B;DR2=01100011B

實驗思路

首先由ALU求出A+B,放入DR2中,此時DR1和DR2分別存放B和A+B;接著用ALU求出(A+B)-B=A,放入DR1中,此時DR1和DR2分別存放A和A+B;最后用ALU求出(A+B)-A=B,放入DR2中,此時DR1和DR2分別存放A和B,交換完成。

實驗過程截圖

- 將A+B 放入 DR2 中

- 求出(A+B)-B=A,放入DR1中

- 求出(A+B)-A=B,放入DR2中

如圖所示,交換完成!

7. 回答問題

-

在實驗中, 在置數給DR1時,SW_BUS#若為高,會出現什麼現象?

- 答:數據可能不會被寫入到DR1中,因為寫使能信號未被激活。

-

在給DR2置數時,應注意什麼問題?

- 答:應確保DR2的寫使能信號有效(如SW_BUS#為低電平),并且輸入的數據正確無誤,同時注意時序,不要在時鐘邊沿到來之前改變數據或控制信號。

-

DR2\ DR1哪個是A,哪個是B?

- 答:A是DR2,B是DR1。

-

在給寄存器置數時,M1=0是否可以?

- 答:M1用于選擇DR1的數據輸入源。M1=1時,DR1選擇D1—A1作為數據輸入端;M1=0時,DR1選擇D0—A0作為數據輸入端。M2用于選擇DR2的數據輸入源。M2=1時,DR2選擇D1—A1作為數據輸入端;M2=0時,DR2選擇D0—A0作為數據輸入端。因此我認為應該是OK的。

-

請說明如何控制ALU完成不同地運算?

- 答:控制ALU完成不同運算,通過一組控制信號**(S2、S1、S0)**實現。這些信號決定了ALU內部邏輯電路的配置,以執行加法、減法、邏輯與、邏輯或、邏輯異或、直通或者乘法等運算。根據實驗文檔中的操作,選擇正確的控制信號組合,即可使ALU執行所需的運算。

-

在置數階段,若ALU_BUS=1,而SW_BUS#=0則會出現什麼問題?

- 答:在置數階段,ALU_BUS=1表示數據總線上有數據,而SW_BUS#=0意味著寫入寄存器的控制信號無效,這樣會導致雖然數據總線上有數據,但是數據無法被正確寫入到寄存器中,因為寫入操作沒有被激活

- 這些控制信號如何產生的?(人充當控制器)信號有時序嗎?

- 答:實驗中,控制信號是由人通過開關手動設置的。有時序,且這些信號的時序非常重要,必須按照特定的順序和時鐘周期給出,以確保數據處理的正確性和時序邏輯的正確執行。

-

什么是數據通路?

- 答:數據通路是指在計算機或數字系統中,數據從一個組件傳輸到另一個組件的路徑。它包括寄存器、算術邏輯單元(ALU)、多路復用器、解復用器、各種邏輯門等,這些組件協同工作,實現數據的流動和處理。

-

操作控制的順序影響結果嗎〉為什么?

- 答:當然會,因為不同的控制序列會激活不同的運算邏輯,導致不同的數據處理流程和結果。

-

如果要求設計出8位的算術邏輯運算單元,請說出最簡單的思路。

-

答:如圖:

-

可以使用兩個ALU,以便處理進位。

圖片來源:CSDN博客:運算器實驗——8位算術邏輯運算實驗

實驗結束,本文收錄于計算機組成原理專欄下

點贊關注收藏,獲取更多干貨~

ISERDESE2原語仿真)

- 圖像畸變校正)

)