一、說明

PCI-Express(peripheral component interconnect express)是一種高速串行計算機擴展總線標準,它原來的名稱為“3GIO”,是由英特爾在2001年提出的,旨在替代舊的PCI,PCI-X和AGP總線標準。

PCIe屬于高速串行點對點雙通道高帶寬傳輸,所連接的設備分配獨享通道帶寬,不共享總線帶寬,主要支持主動電源管理,錯誤報告,端對端的可靠性傳輸,熱插拔以及服務質量(QOS)等功能。

V3.0版本最大的變更是支持8Gbps的速率,以及為實現帶寬翻倍使用了128b/132b的高效編碼技術。同時,仍是支持2.5Gbps和5Gbps的傳輸速率(8b/10b編碼)。

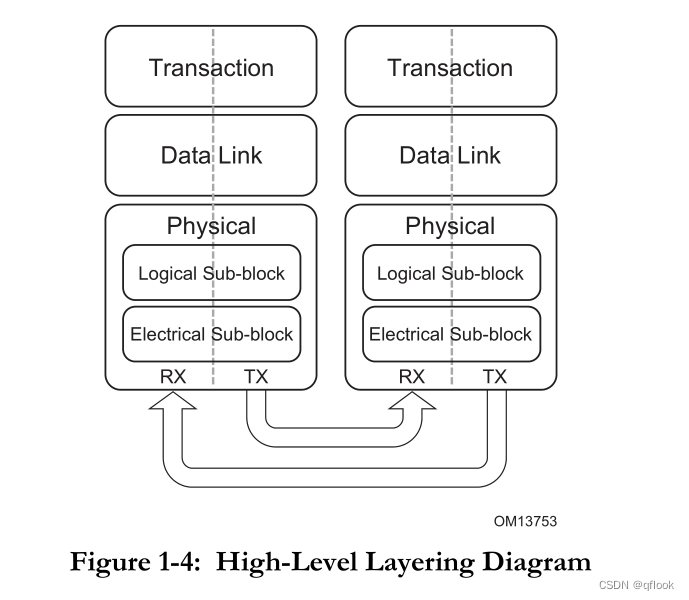

分層框圖如下,本文主要講的物理層Physical主要包括邏輯部分和電氣部分,主要包括PLL電路、Buffer、阻抗匹配電路、驅動電路、串并轉換或并串轉換電路及均衡電路等;邏輯子模塊的功能是負責數據鏈路層和電氣子模塊的交互,例如有多lane的情況下,將從數據鏈路層的數據拆分,并8b/10b編碼給到電氣子模塊等:

數據結構如下:

數據結構如下:

傳輸性能分析:https://zhuanlan.zhihu.com/p/645335755?utm_id=0

二、電氣要求

1.發送規范

1)測量環境

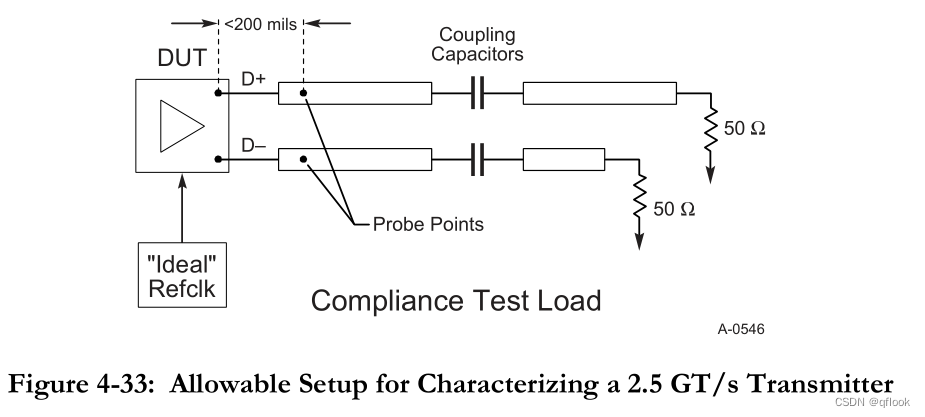

2.5Gbps速率可以直接用探頭測試,需注意探針要距離TX管腳不超過200mils,且在AC耦合電容之前。環境如下:

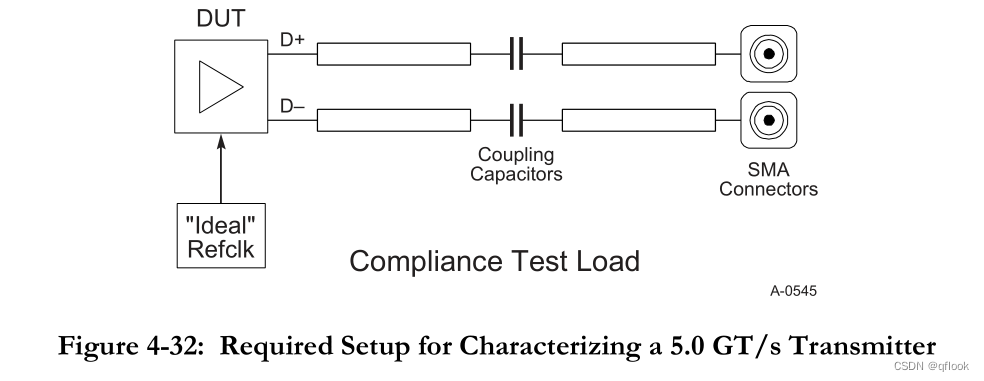

5Gbps速率不能直接用探頭點測(前端電容、引線長度導致的寄生參數等),需要用SMA直接接到示波器,環境如下:

另外,需要說明的是,以上兩種速率也可以用通用的測試夾具進行測試,不過需要通過去嵌等手段去除夾具的影響。

另外,需要說明的是,以上兩種速率也可以用通用的測試夾具進行測試,不過需要通過去嵌等手段去除夾具的影響。

對于8Gbps速率來說,則需要特制的測試板來實現測試目的,環境如下:

其中低抖動時鐘源是為了測量抖動時排除外部干擾;Breakout Channel疏導通道是由于芯片管腳(特別是BGA封裝)無法直接測試,也因此需要本通道盡量短(不超過6英寸),插損不能超過2dB,回損不能高于15dB(4G頻率范圍內);Replica Channel復制通道應盡量和疏導通道一樣(走線長度、過孔、所在層數等),方便去嵌操作。

2)TX均衡

2.5Gbps和5Gbps兩種速率僅支持去加重均衡技術,其中2.5Gbps只支持-3.5dB去加重,5Gbps支持-3.5dB和-6dB兩種去加重規格。

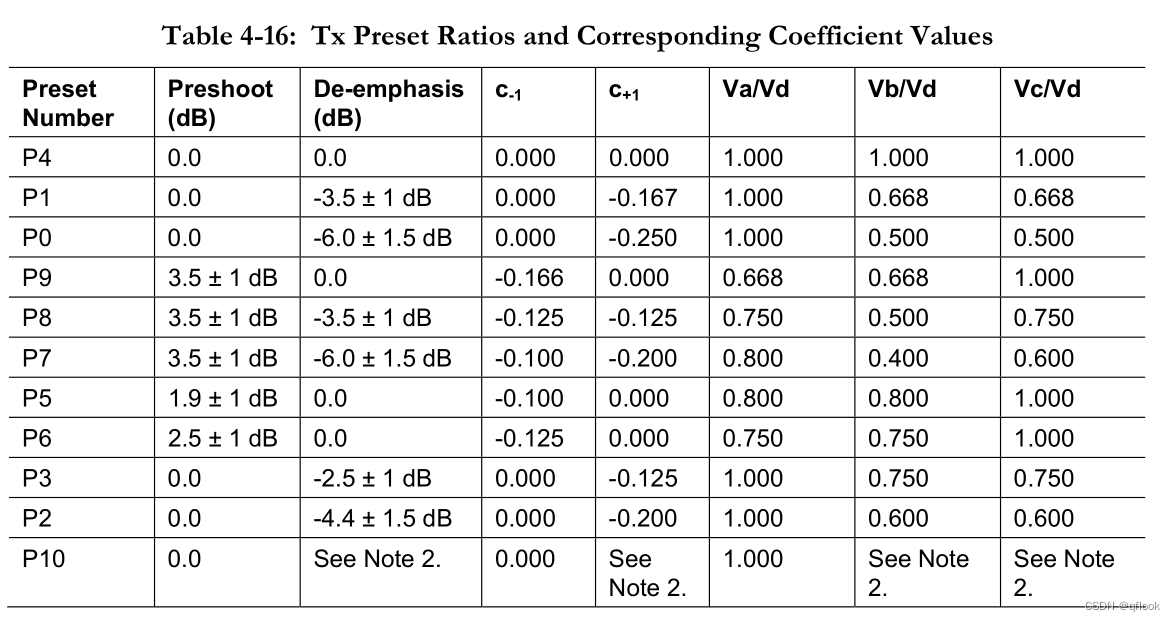

8Gbps的TX均衡比較復雜,通過3抽頭濾波器實現11中均衡組合(具體均衡實現方法參考:

mp.weixin.qq.com),具體如下:

其中全擺幅需要支持全部均衡,Reduced swing低擺幅僅需支持P1、P3、P4、P5、P6和P9即可。以上組合中的P0和P1也就是2.5G和5G的去加重,因此實現了兼容。

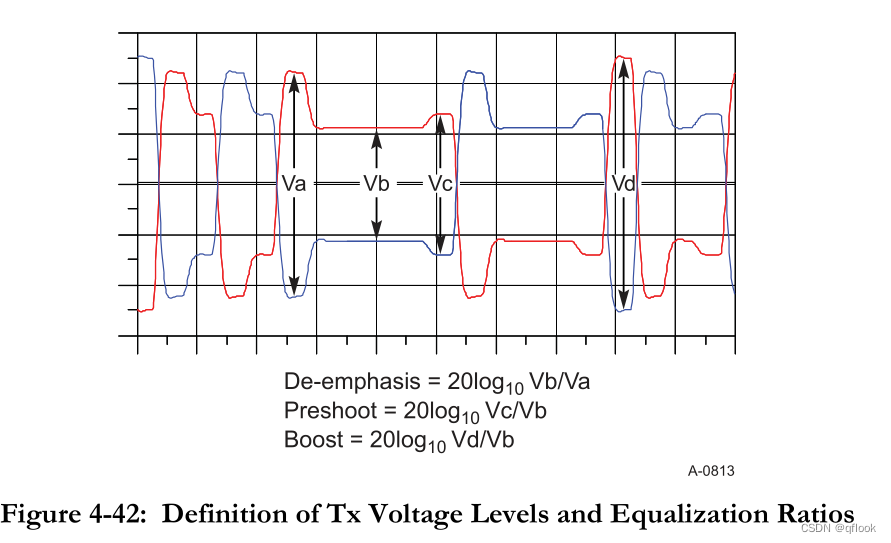

上表中的C就是指的抽頭系數,通過不同系數來實現的不同均衡組合,也導致了信號波形的區別:

Vb就是指去加重電壓,VC是指預充電壓,Vd是指最大幅度電壓,Va協議上也沒有具體說明,個人認為是normal電壓。

Vb就是指去加重電壓,VC是指預充電壓,Vd是指最大幅度電壓,Va協議上也沒有具體說明,個人認為是normal電壓。

3)TX電器規范

協議明確規定了3種速率的TX參數,具體如下:

| Symbol | 2.5G | 5G | 8G | 備注 |

| UI | 399.88~400.12ps | 199.94~200.06ps | 124.9625~125.0375ps | 不包含擴頻時鐘SCC引入的抖動 |

| VTX-DIFF-PP | 0.8~1.2V | 0.8~1.2V | 無 | 全擺幅電壓 |

| V TX-DIFF-PP-LOW | 0.4~1.2V | 0.4~1.2V | 無 | reduce擺幅電壓 |

| V TX-DE-RATIO-3.5dB | 3~4dB | 3~4dB | 參考Table 4-16 | |

| V TX-DE-RATIO-6dB | 不支持 | 5.5~6.5dB | 參考Table 4-16 | |

| V TX-CM-AC-PP | 未規定 | ≤150mV | ≤150mV | AC共模電壓峰峰值 |

| V TX-DC-CM | 0~3.6V | 0~3.6V | 0~3.6V | DC共模電壓峰峰值 |

| Z TX-DIFF-DC | 80~120Ω | ≤120Ω | ≤120Ω | |

| L TX-SKEW | 【500ps,2UI】 | 【500ps,4UI】 | 【500ps,6UI】 | 差分對間偏差 |

| C TX | 【75,265nF】 | 【75,265nF】 | 【176,265nF】 | AC耦合電容 |

| Symbol | 8G | 備注 |

| V TX-FS-NO-EQ | 0.8~1.3V | 無TX均衡的全擺幅峰峰值電壓 |

| V TX-RS-NO-EQ | ≤1.3V | 無TX均衡的低擺幅峰峰值電壓 |

| V TX-EIEOS-FS | ≥250mV | EIEOS期間全擺幅電壓最小值 |

| V TX-EIEOS-RS | ≥232mV | EIEOS期間低擺幅電壓最小值 |

2.RX規范

1)2.5G的電氣規范

具體要求如下:

| 參數 | 要求 | 備注 |

| UI | 399.88~400.12ps | 不包含SSC |

| 差分電壓峰峰值 | 0.175~1.2V | |

| 眼寬 | ≥0.4UI | |

| 單端匹配電阻 | 40~60Ω | |

| 差分匹配電阻 | 80~120Ω | |

| 差分對間偏差 | ≤20ns | 5G是8ns,8G是6ns |

2)5G的電氣規范

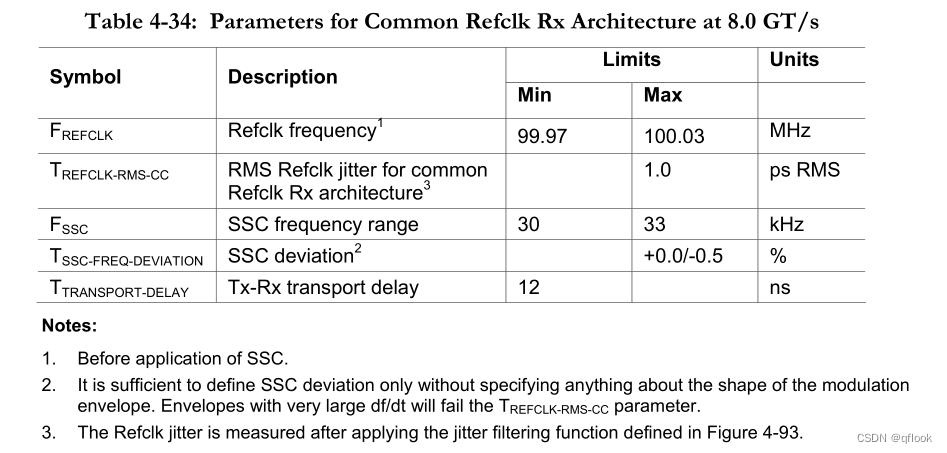

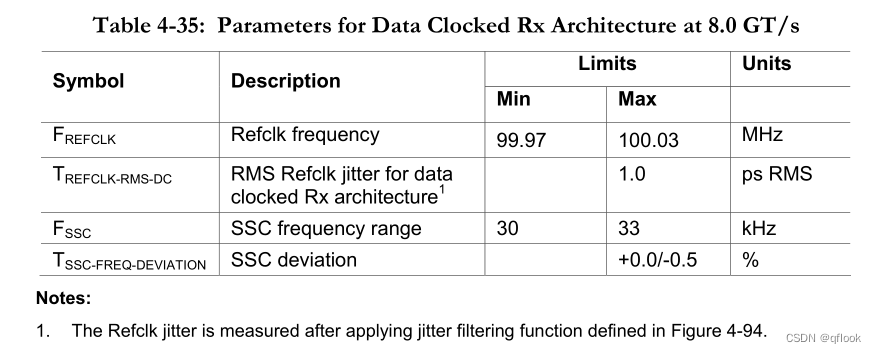

5G的RX要求分2種情況,一是TX和RX共用100MHz參考時鐘,另外一個是數據嵌入式時鐘。

眼圖模板如下:

共用參考時鐘的參數如下:

共用參考時鐘的參數如下:

數據嵌入式時鐘的參數如下:

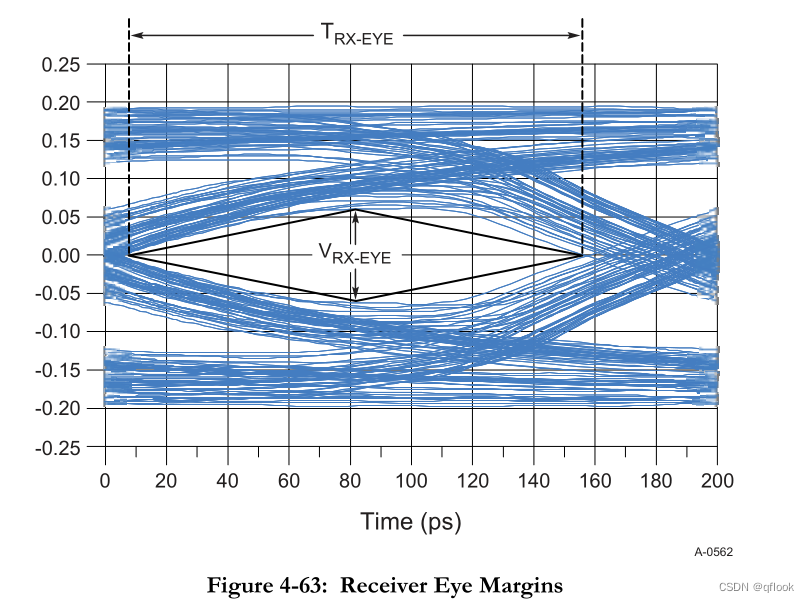

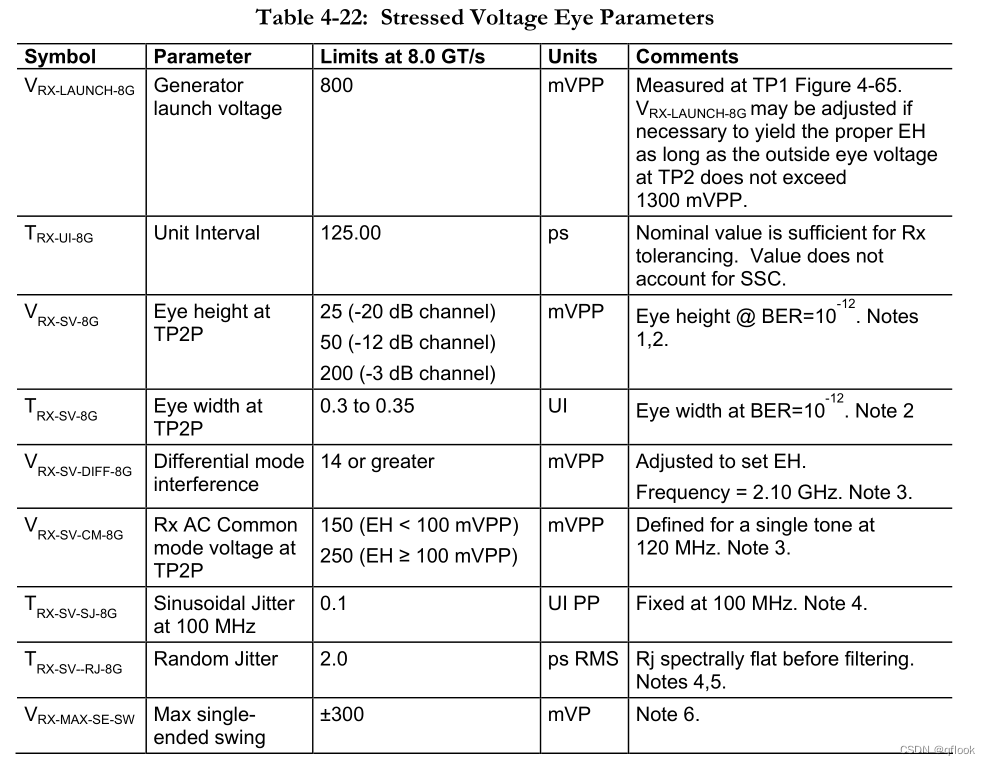

3)8G的RX測試

RX主要進行容限測試,測試環境如下:

主要原理是校準通道和疏導通道模擬實際走線,信號發生器模擬TX,首先調整在TP2P位置測得的壓力眼圖(有2種眼圖,分別測試電壓和抖動,具體如Table 4-22和4-23),然后切換到#2通道將信號發送給RX,然后測試BER誤碼率要求小于10的-12次方。

主要原理是校準通道和疏導通道模擬實際走線,信號發生器模擬TX,首先調整在TP2P位置測得的壓力眼圖(有2種眼圖,分別測試電壓和抖動,具體如Table 4-22和4-23),然后切換到#2通道將信號發送給RX,然后測試BER誤碼率要求小于10的-12次方。

校準通道提供了3種,代表了真實情況遇到的最小到最大插損信道的情況:

校準通道提供了3種,代表了真實情況遇到的最小到最大插損信道的情況:

針對最短校準通道和中間校準通道,RX只能使用一階CTLE均衡;針對最長的校準通道,RX可以使用一階CTLE均衡和1tap的DFE均衡。

其中CTLE均衡的傳遞函數:

Adc是指DC增益,協議規定可以在-6dB和-12dB之間以1dB的步長調節。曲線如下:

DFE均衡的框圖如下:

DFE均衡的框圖如下:

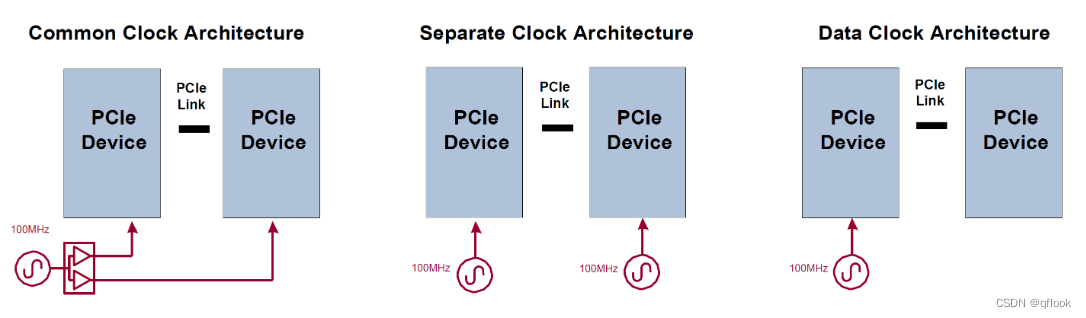

4)參考時鐘

參考時鐘Refclk的頻率是100MHz,其功能不是數據時鐘同步,而是給內部控制器的時鐘。主要有三種模式:

共享參考時鐘的具體參數要求如下:

共享參考時鐘的具體參數要求如下:

嵌入式參考時鐘參數要求:

獨立的參考時鐘要求就是兩個時鐘都是±300ppm。

三種參考時鐘對比:

| 類型 | 優點 | 缺點 | 備注 |

| 共享參考時鐘 | 1)收發側的時鐘抖動jitter都是相同的,因此便于跟蹤和計算 2)低功耗模式仍然可用,防止PLL偏移 | 時鐘偏差要控制在12ns以內,對比較大的板卡或跨板等情況的實現有很大挑戰 | 穩定性好,應用最廣泛 |

| 獨立參考時鐘 | 獨立提供時鐘,完全不受PCB布局、走線長度的影響 | 現在沒有方案可以確定對端參考時鐘是否開啟SSC,影響抖動計算 | |

| 嵌入式參考時鐘 | 實現簡單 | PCIE4.0取消了本方案 | 不推薦 |

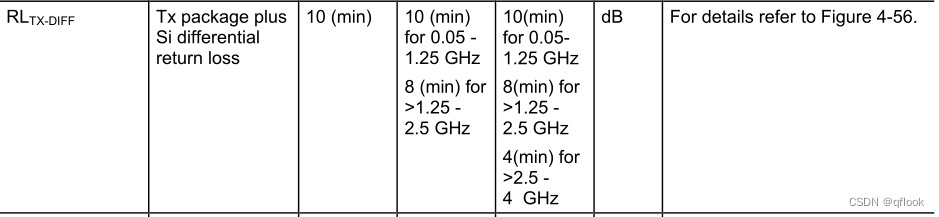

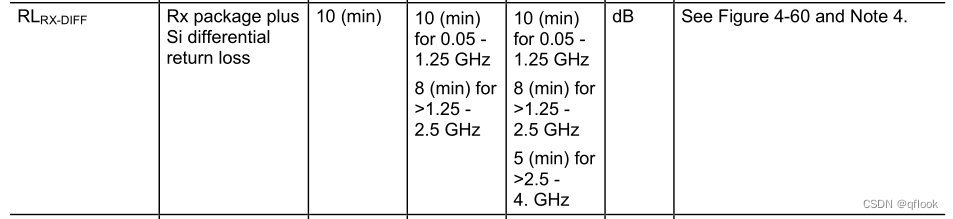

三、S參數要求

協議規定了芯片內的差分回損SDD11,具體如下:

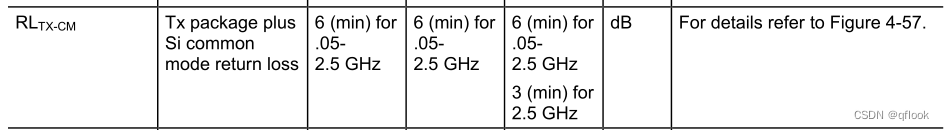

具體大小如下參數要求:

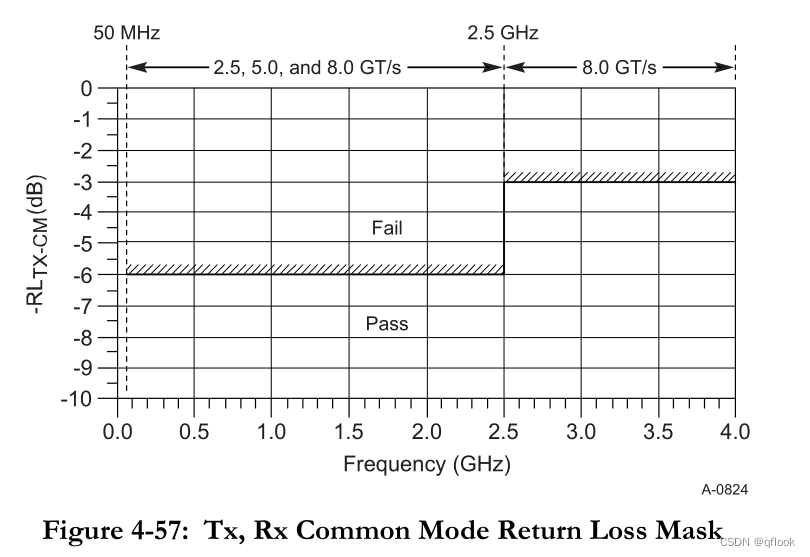

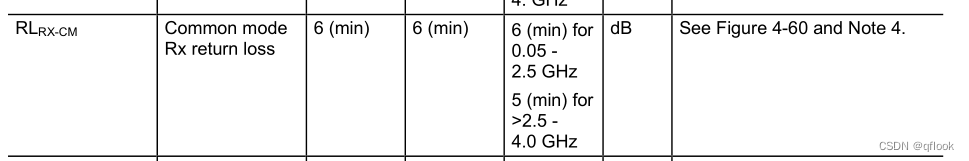

協議同樣要求共模回損SCC11,具體如下:

協議同樣要求共模回損SCC11,具體如下:

具體大小如下參數要求(注意RX的參數和圖對應不上,不確定是圖僅畫出了TX沒有包含RX,還是參數寫錯了):

測試方法也是通過疏導通道的SMA頭連接網分進行,不過測試結果通過去嵌來排除疏導通道的影響。

測試方法也是通過疏導通道的SMA頭連接網分進行,不過測試結果通過去嵌來排除疏導通道的影響。

)