前言:比較器的價值

1、為何稱比較器為“決策者”?

- 邏輯判斷的物理實現

比較器通過硬件電路直接完成“大于/小于”的二元判斷,無需軟件干預。例如:- 在過壓保護電路中,比較器實時監測輸入電壓?Vin??與參考電壓?Vref?,當?Vin?>Vref??時,輸出端立即“決策”拉低電平,觸發保護動作。

- 這種決策速度遠超微控制器(MCU)的ADC采樣+軟件比較流程(后者可能需微秒級延遲)。

- 多級決策的擴展性

通過級聯多個比較器,可實現復雜邏輯決策:- 窗口比較器:由兩個比較器構成,檢測輸入電壓是否在?Vref1??和?Vref2??之間(如電池電壓監測系統)。

- 優先級編碼器:結合比較器陣列與邏輯門,可對多路輸入信號進行優先級排序(如中斷控制器設計)。

2、模擬→數字轉化的關鍵特性

輸出電平的“硬切換”

比較器輸出端通常為推挽結構或開漏結構,可直接驅動數字電路(如MCU的GPIO、邏輯門芯片):- 推挽輸出:如LM393,輸出高電平接近?VCC?,低電平接近?GND,兼容CMOS/TTL邏輯。

- 開漏輸出:如TLV3501,需外接上拉電阻,適合多設備共享信號線(如I2C總線)。

與ADC的互補關系

特性 比較器 ADC 輸出 單比特(0/1) 多比特(N位數字編碼) 速度 納秒級(高速型號<1ns) 微秒至毫秒級(取決于分辨率) 資源占用 面積小、功耗低 面積大、功耗高(需采樣保持電路) 典型應用 閾值檢測、觸發器 精密測量、信號量化 案例:在超聲波測距系統中,比較器用于檢測回波信號的上升沿(觸發計時器),而ADC用于后續信號幅度的精確測量。

3、設計中的“轉化效率”優化

- 輸入級匹配:降低決策誤差

- 共模輸入范圍:確保輸入信號在比較器允許范圍內(如TLV3501的共模范圍為??0.2V?至?VCC?+0.2V)。

- 輸入阻抗:高阻抗設計(如MOSFET輸入級)減少對前級電路的負載效應。

- 輸出級驅動:增強數字兼容性

- 灌電流/拉電流能力:選擇輸出驅動強的比較器(如LM2903可提供40mA灌電流),直接驅動LED或繼電器。

- 電平轉換:若數字系統工作電壓與比較器不同(如比較器用5V,MCU用3.3V),需添加電平轉換電路(如SN74LVC1T45)。

- 動態響應優化:提升轉化速度

- 壓擺率(SR):高速比較器(如ADCMP572的SR達6000V/μs)可快速響應輸入信號跳變。

- 傳播延遲均衡:在高速數據采集系統中,選擇傳播延遲匹配的比較器陣列(如MAX9626的四通道比較器,延遲匹配<50ps)。

4、典型應用中的“轉化”案例

- 零交叉檢測(AC信號→數字脈沖)

- 電路:將交流信號接入比較器同相端,反相端接地。

- 效果:輸出為與AC信號同頻率的方波,供數字電路(如MCU定時器)測量頻率或相位。

- 熱敏電阻溫度監測(電阻變化→數字告警)

- 電路:熱敏電阻與固定電阻分壓,分壓點接比較器反相端,參考電壓由電位器設定。

- 效果:當溫度超過閾值時,比較器輸出翻轉,觸發風扇或報警器。

- Σ-Δ ADC中的1位量化(模擬信號→PWM流)

- 原理:比較器將積分器輸出與參考電壓比較,生成1位數字流(0/1),反饋環路調整積分器斜率,實現高精度量化。

- 優勢:通過過采樣和噪聲整形,用簡單比較器實現16位以上分辨率。

5、總結:比較器的“轉化哲學”

比較器的核心價值在于以極簡的硬件實現模擬→數字的“瞬間決策”,其設計需圍繞三大矛盾展開優化:

- 速度 vs 精度:高速比較器可能犧牲失調電壓精度(如ADCMP572的?VOS??為10mV),而精密比較器(如LTC6752的?VOS??<1μV)速度較慢。

- 功耗 vs 性能:微功率比較器(如LMP7300的IQ=20μA)傳播延遲可能達微秒級,而高速型號功耗可達數百毫瓦。

- 通用性 vs 專用性:通用比較器(如LM393)適用于多數場景,而專用型號(如LMH7322的10GHz帶寬)針對特定需求優化。

最終目標:在給定約束(成本、面積、功耗)下,選擇或設計最合適的比較器,實現模擬信號到數字邏輯的高效、可靠轉化。

一、核心定義與功能

比較器是模擬電路中的核心模塊,用于比較兩個模擬信號(電壓或電流)的大小,并輸出二進制邏輯電平(高電平或低電平)。其本質是1位模/數轉換器(ADC),將連續變化的模擬信號轉換為離散的數字信號,是連接模擬與數字世界的橋梁。

二、工作原理

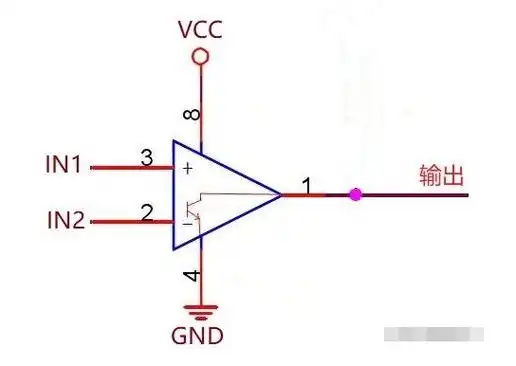

差分輸入與高增益放大

比較器通過差分輸入級接收兩個信號(同相輸入端?V+?、反相輸入端?V??),并利用極高的開環增益(通常?>105)放大微小電壓差?ΔV=V+??V??。飽和輸出特性

由于無負反饋,輸出端迅速達到電源電壓的極限值:- 若?ΔV>0,輸出飽和至正電源軌(如?VCC?);1電平

- 若?ΔV<0,輸出飽和至負電源軌(如?GND);0電平

閾值與遲滯效應

- 固定閾值:部分比較器僅有一個參考電壓?Vref?,當輸入信號跨越?Vref??時輸出翻轉。

- 遲滯比較器:通過正反饋引入兩個閾值(上升閾值?VTH+?、下降閾值?VTH??),形成“回差”特性,有效抑制輸入噪聲引起的輸出抖動。例如,LM393的遲滯電壓可通過外部電阻調節。

三、關鍵性能指標

- 精度

- 失調電壓(VOS?):輸入為零時輸出的偏移電壓,需通過激光調阻或數字校準技術降低。

- 增益帶寬積(GBW):決定比較器對快速變化信號的響應能力,高速比較器(如MAX961)的GBW可達GHz級。

- 速度

- 傳播延遲(tp?):輸入信號變化到輸出穩定所需時間,典型值為納秒級(如LMH7322的?tp?=700ps)。

- 壓擺率(SR):輸出電壓的最大變化速率,影響大信號響應速度。

- 穩定性

- 共模抑制比(CMRR):衡量對共模信號的抑制能力,高CMRR(如100dB)可減少電源噪聲干擾。

- 遲滯電壓(VHYST?):通過正反饋增強抗干擾性,典型值為幾mV至幾百mV。

四、典型應用場景

- 信號檢測與整形

- 過零檢測:檢測交流信號是否過零,用于電機控制或相位同步。

- 波形整形:將正弦波轉換為方波,為數字電路提供清晰時鐘信號。

- 電壓監測與保護

- 過壓/欠壓保護:監測電源電壓是否超出安全范圍,觸發保護電路(如電池管理系統中的過充保護)。

- 窗口比較器:由兩個比較器構成,檢測輸入電壓是否在預設范圍內(如溫度監控系統)。

- 模數轉換(ADC)

- 逐次逼近寄存器(SAR)ADC:比較器通過二分搜索法確定輸入電壓的數字編碼。

- Σ-Δ ADC:比較器輸出用于反饋環路,實現高精度轉換。

- 振蕩器與定時器

- 方波振蕩器:利用遲滯比較器和RC網絡構成弛張振蕩器,生成固定頻率信號。

五、比較器與運算放大器的區別

| 特性 | 比較器 | 運算放大器 |

|---|---|---|

| 反饋機制 | 開環或正反饋(遲滯) | 通常負反饋 |

| 輸出狀態 | 飽和至電源軌(二進制) | 線性放大(連續值) |

| 響應速度 | 極快(納秒級) | 較慢(微秒級) |

| 抗噪聲能力 | 遲滯設計增強穩定性 | 依賴負反饋抑制噪聲 |

| 典型應用 | 數字信號處理、閾值檢測 | 模擬信號放大、濾波 |

六、設計優化策略

- 降低延遲

- 選擇高速比較器(如LMH7220),其傳播延遲僅4.5ns。

- 減少輸入電容和寄生電感,優化PCB布局(如縮短走線、增加地平面)。

- 降低功耗

- 采用微功率比較器(如LMP7300),靜態電流低至20μA。

- 使用電源管理技術(如動態調整供電電壓)。

- 提高抗干擾性

- 增加遲滯電壓(如通過外部電阻分壓)。

- 采用屏蔽設計和低噪聲電源(如LDO穩壓器)。

七、典型電路案例

- 光控燈電路

- 原理:將光敏電阻(LDR)與比較器反相端連接,參考電壓由分壓電阻設定。白天光照強時,LDR阻值低,反相端電壓低于參考值,比較器輸出低電平,燈滅;夜晚反之。

- 芯片推薦:LM393(雙路比較器,成本低)。

- 欠壓指示器

- 原理:通過電位器調節參考電壓,當輸入電壓低于閾值時,比較器輸出低電平,驅動LED或蜂鳴器報警。

- 芯片推薦:LM358(單電源供電,兼容TTL邏輯)。

八、總結

比較器是模擬電路中的“決策者”,其核心價值在于將模擬信號轉化為數字電平邏輯,廣泛應用于信號檢測、保護電路、ADC等領域。設計時需權衡速度、精度、功耗和抗干擾性,通過合理選擇芯片類型(如高速LMH7322、低功耗LMP7300)和優化電路拓撲(如遲滯設計、屏蔽布局),可顯著提升系統性能。

(補題))

詳解:當Transformer“看見”世界,計算機視覺的范式革命)

:PHP 性能優化:打造高效應用)

)