概述

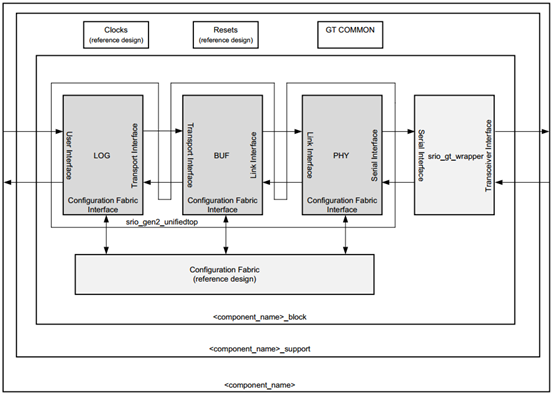

RapidIO標準定義為三層:邏輯層、傳輸層、物理層。

邏輯層:定義總體協議和包格式,包含設備發起/完成事務的必要信息。

傳輸層:提供包傳輸的路由信息(對頂層不可見)。

物理層:描述設備級接口細節(包傳輸機制、流控、電氣特性、低級錯誤管理)。

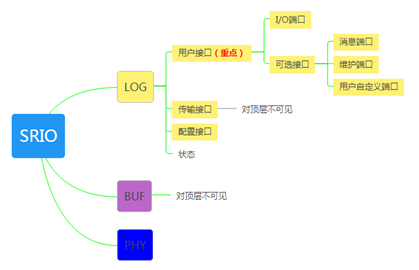

邏輯層(LOG)

邏輯層劃分為模塊控制并解析數據包,包含三種接口:

用戶接口(User Interface)

可配置端口數量和事務類型。

支持通過AXI4-Lite總線訪問本地/遠程寄存器。

傳輸接口(Transport Interface)

相當于緩存Buffer(對頂層不可見)。

配置接口(Configuration Fabric Interface)

讀寫本地配置空間及邏輯層/傳輸層寄存器。

用戶接口詳解

- I/O端口集:

支持I/O事務(NWRITEs、NWRITE_Rs、SWRITEs、NREADs、RESPONSEs)。

可選支持消息事務(取決于IP核配置)。

支持門鈴事務。

消息端口:專用于消息事務。

維護端口:專用于維護事務。

用戶自定義端口:支持自定義事務類型(未使能時丟棄包)。

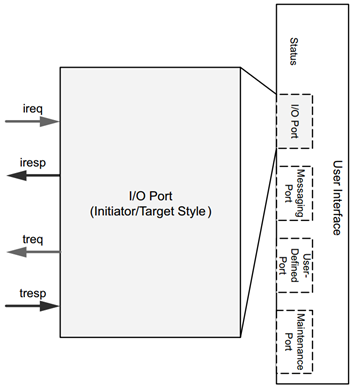

I/O端口類型

- Condensed I/O:

單AXI4-Stream通道發送/接收所有包類型。

- Initiator/Target:

分離請求與響應事務,共4個AXI4-Stream通道。

數據流協議

支持HELLO格式與SRIO Stream格式。

- 通道映射關系:

s_axis_ireq*→ ireq(本地請求)m_axis_iresp*→ iresp(遠程響應)m_axis_treq*→ treq(遠程請求)s_axis_tresp*→ tresp(本地響應)

物理層(PHY)

功能:處理鏈路訓練、初始化、協議、CRC校驗、應答標識符插入。

- 接口:

通過AXI4-Stream通道連接傳輸層。

AXI4-Lite接口連接配置層。

串行接口連接高速收發器(通常使用FPGA集成的GT接口)。

寄存器空間

能力寄存器空間(CAR)

命令和狀態寄存器空間(CSR)

均在邏輯層實現。

HELLO包格式

標準化包頭域,包頭與數據分離傳輸。

- Size域規則:

值 = 傳輸字節總數 - 1(有效范圍0~255,對應實際1~256字節)。

需與RapidIO包的size/address/wdptr域一致。

- 因AXI4-Stream的

tdata為8字節,需分情況處理:數據量 < 8字節

數據量 > 8字節

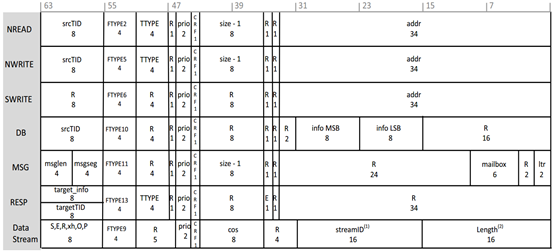

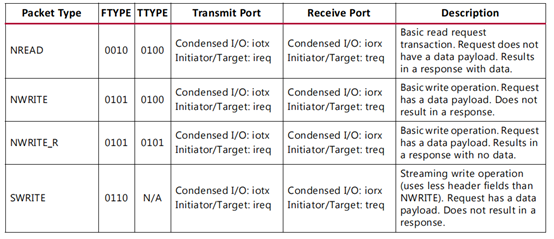

SRIO事務類型及關系梳理

1. 直接I/O(DMA)事務

| 事務類型 | 特性 | 應用場景 |

|---|---|---|

| NWRITE | 寫操作,無需響應 | 高效無確認數據傳輸 |

| NWRITE_R | 寫操作,需響應 | 需數據完整性的場景 |

| SWRITE | 流式寫(數據長度需為8B整數倍) | 連續數據流(如視頻) |

| NREAD | 讀操作,返回響應包+數據 | 讀取目標地址數據 |

2. 消息傳遞事務

| 事務類型 | 特性 | 應用場景 |

|---|---|---|

| DOORBELL | 短消息通知(如中斷觸發) | 輕量級事件通知 |

| MESSAGE | 長消息傳輸(郵箱路由) | 動態通信/軟件管理交互 |

3. 維護事務

MAINTENANCE READ/WRITE:讀寫配置寄存器(初始化/錯誤處理)。

事務對比

| 特性 | 直接I/O事務 | 消息傳遞事務 |

|---|---|---|

| 效率 | 高(硬件控制) | 低(軟件介入) |

| 可靠性 | NWRITE無確認 | 依賴軟件處理 |

| 延遲 | 低 | 較高 |

| 典型場景 | DSP與FPGA間實時通信 | 多處理器系統通知 |

事務類型對應表如下,更具體地可以見PG007開發手冊P73頁。

SRIO事務時序仿真

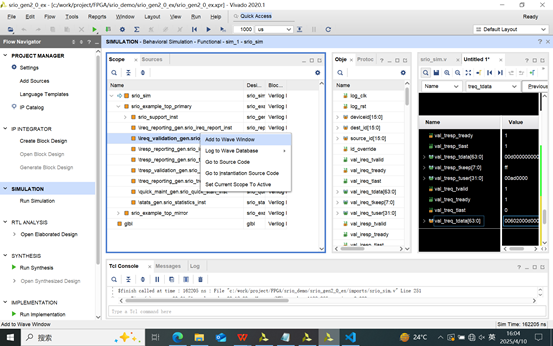

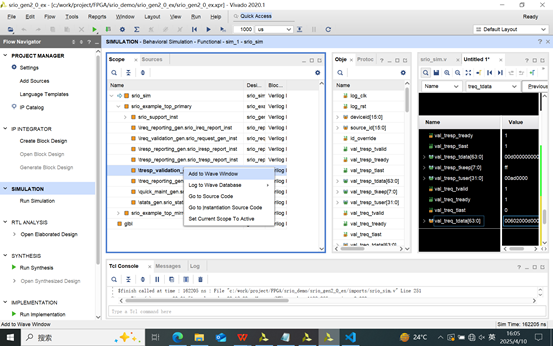

仿真步驟(Vivado 2020.1)

創建工程及SRIO IP核。

右鍵IP核 → "Open IP Example Design"。

運行仿真,添加

request/response模塊觀察信號。

運行約1000us捕獲事務動作。

關鍵事務時序

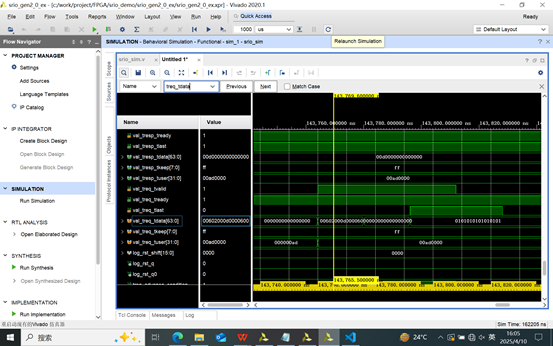

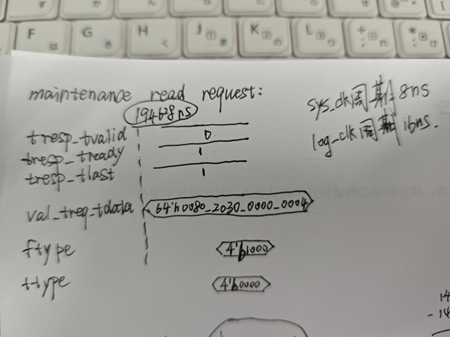

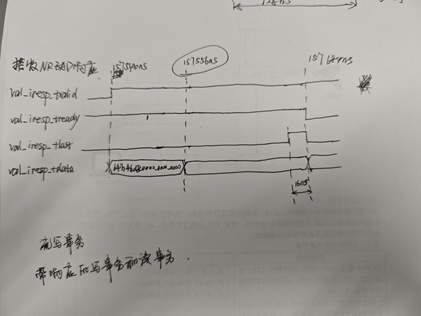

- MAINTENANCE READ REQUEST

接收請求,無響應(

val_tresp_tvalid=0)。

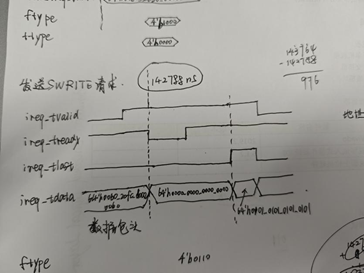

SWRITE請求(發送)

val_ireq_tvalid拉高,ftype=6,ttype=0。

SWRITE請求(接收)

response模塊驗證事務類型。

ftype(6)和ttype(0)

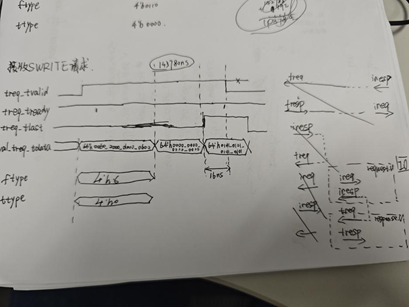

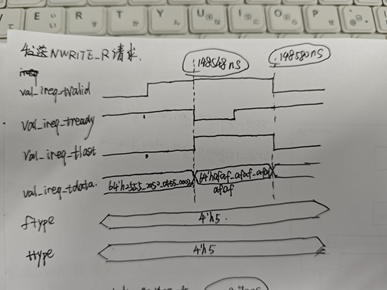

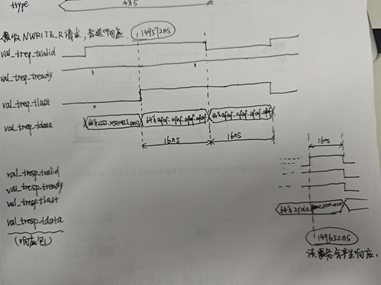

NWRITE_R請求(發送)

請求包發送。

NWRITE_R請求(接收+響應)

接收請求后發送響應包,和發送的請求包一致,該事務會產生響應,在一段時間后可以看到val_tresp_tvalid拉高一個周期,發送響應包val_tresp_tdata = 64’h25d0_4000_0000_0000。

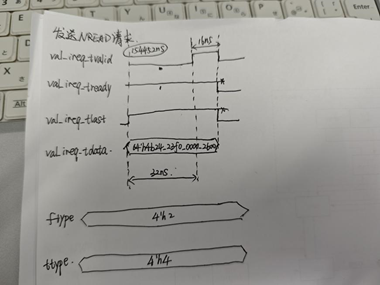

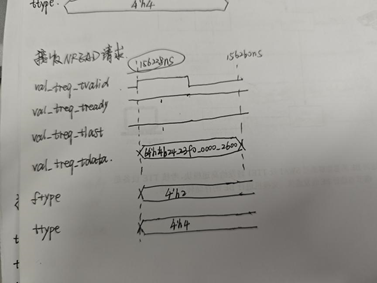

NREAD請求(發送)

僅包頭無數據。

NREAD請求(接收)

接收模塊返回響應包+數據。

- NREAD響應(發送)

size=8'h3f→ 發送64字節數據(8個周期)。

- NREAD響應(接收)

接收包頭(

val_iresp_tdata=64'h4bd8400000000000)及數據。 跟在包頭后面的是數據0。

自定義事務傳輸仿真

計劃仿真NWRITE和SWRITE兩種事務類型,通過FIFO實現用戶層時鐘到IP核跨時鐘傳輸以及數據緩存的功能,方便用戶直接使用。

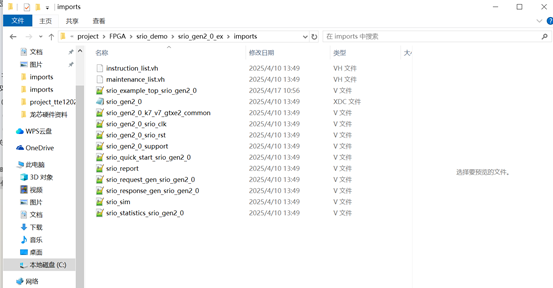

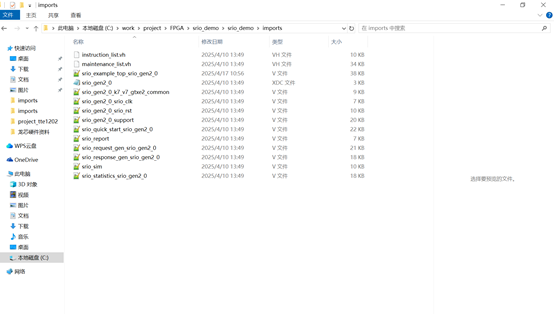

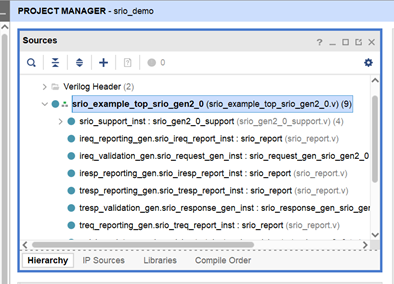

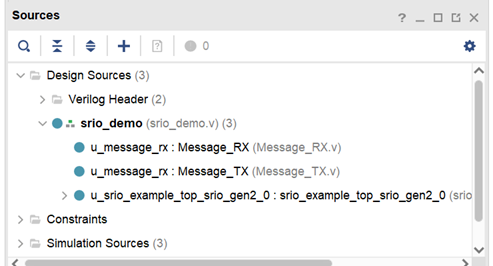

移植srio_example工程

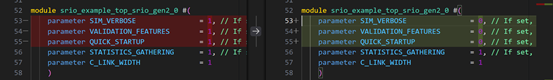

配置參數:

parameter?SIM_VERBOSE????????????=?1,??//?仿真詳細日志 parameter?VALIDATION_FEATURES????=?0,??//?關閉驗證功能 parameter?QUICK_STARTUP??????????=?1,??//?啟用快速啟動 parameter?STATISTICS_GATHERING???=?0,??//?關閉統計功能 parameter?C_LINK_WIDTH???????????=?4???//?4x通道將示例工程文件夾import拷貝到自己工程中:

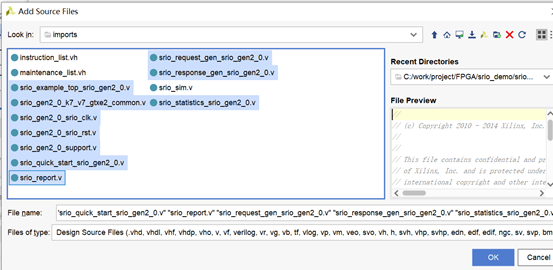

添加文件:

除了仿真文件其余都加進去。

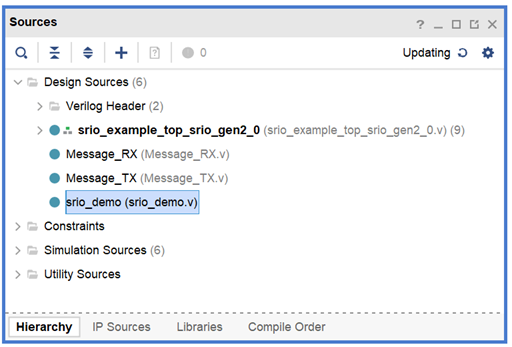

添加好的工程目錄如下:

搭建好總的框架,并對SRIO官方案例工程進行一些修改

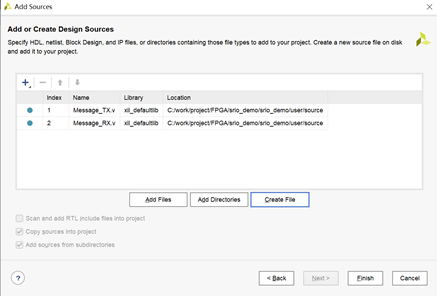

創建收發模塊:

首先創建好兩個模塊,分別是Message_TX數據發送模塊和Message_RX數據接收模塊。

創建頂層模塊:

創建一個頂層模塊srio_demo。

對srio_example模塊進行修改:

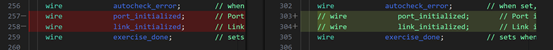

要提前對srio_example模塊進行一些處理,添加一些信號給數據收發模塊用。(下面圖片中左邊時示例程序,右邊是對其修改后的程序)

首先把一些不必要的報告和一些附加功能屏蔽掉

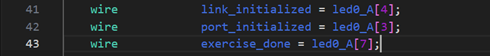

然后把port_initialized和link_initialized兩個信號引出來

![]()

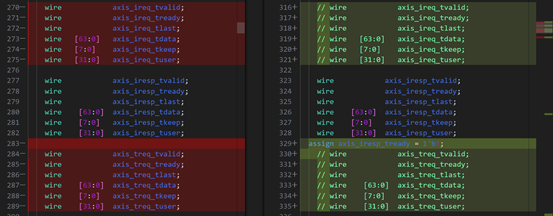

然后把log_clk用戶時鐘引出來給外部使用

![]()

![]()

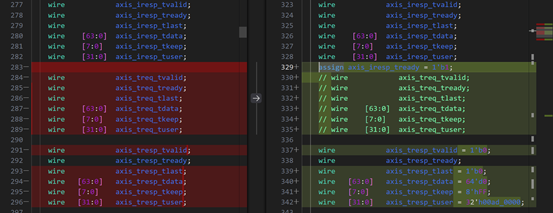

然后把ireq和treq相關AXI總線信號引出來

最后就是把IP核的其他輸入信號賦上一些初始值,主要是iresp和tresp,保證IP核正常運行。

最終修改好之后整體框架如下圖:

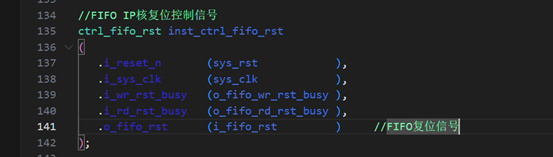

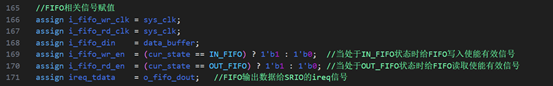

加上FIFO IP核,并配置好相應參數,編寫好發送模塊

這里描述簡單些,例化好FIFO IP,并給FIFO相關信號賦值

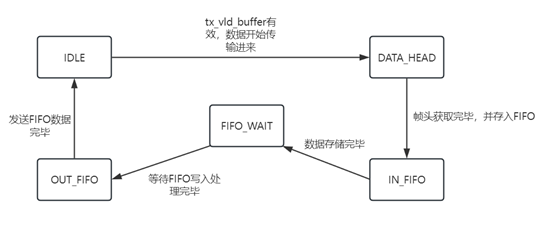

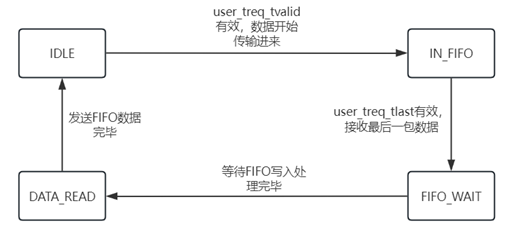

最后編寫發送模塊的剩余代碼,發送模塊狀態轉換圖如下圖所示

加上FIFO IP核,并配置好相應參數,編寫好接收模塊

這里描述簡單些,接收模塊的狀態轉換圖如下圖所示

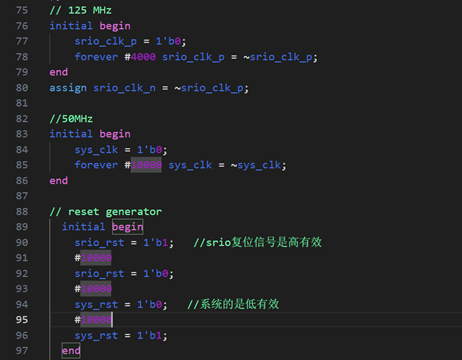

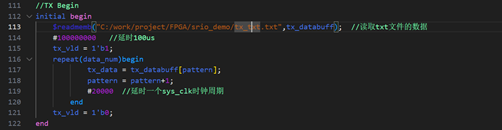

編寫仿真程序,仿真調試

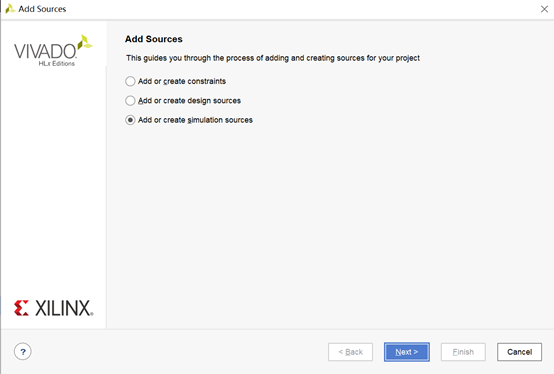

首先創建仿真文件

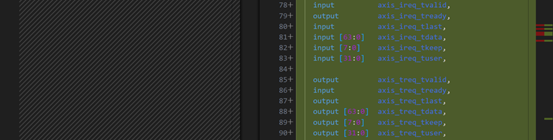

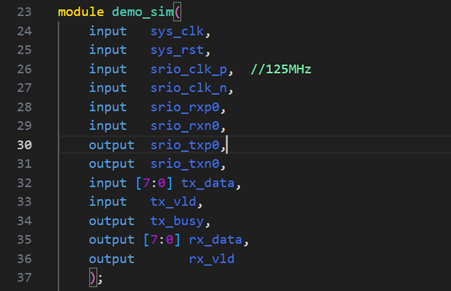

把頂層文件的端口添加到仿真文件中

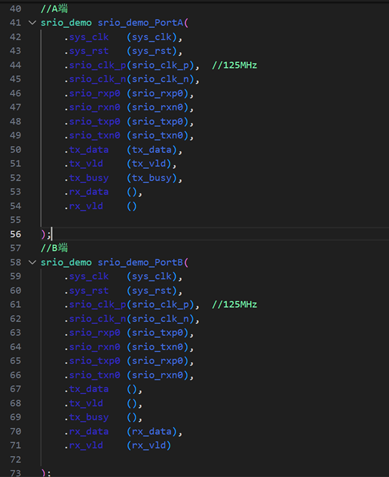

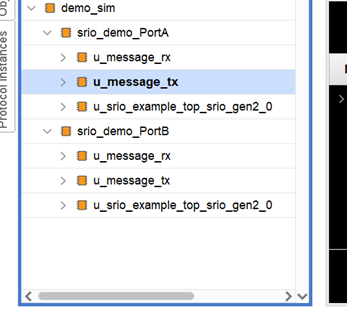

例化兩個端,分別是PORTA端和PORTB端,兩個端TX和RX引腳反接,并設置A端作為發送端,B端設為接收端

產生時鐘和復位信號

添加上一些監測信號

編譯完成后,點擊仿真,添加PORTA的tx模塊和PORTB的rx模塊進波形窗口

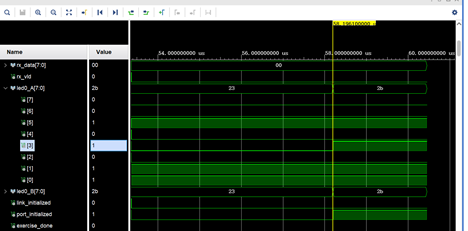

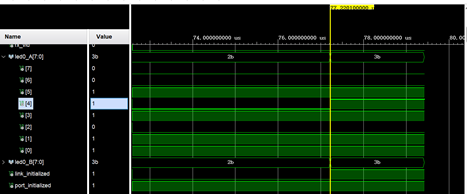

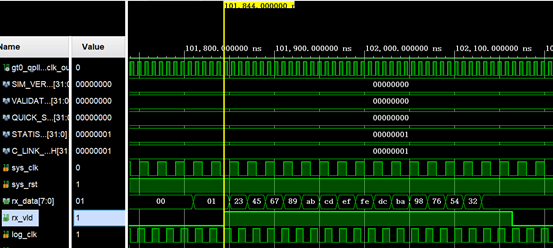

繼續運行仿真,看一下是否link上。在58us左右的時候,port_initialized拉高

在77us左右link_initialized拉高,表示建鏈成功。一般port_initialized&link_initialized作為初始化完成的標志。

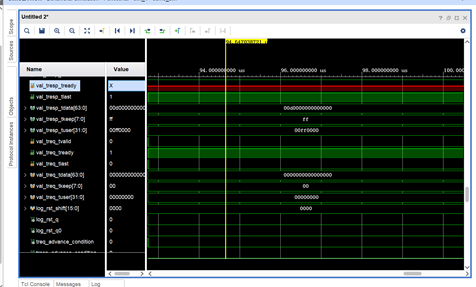

在94us左右treq_tdata不會有動作,跟之前示例工程有區別,這是沒有傳數過去,是正常的。

編寫傳輸數據流程:

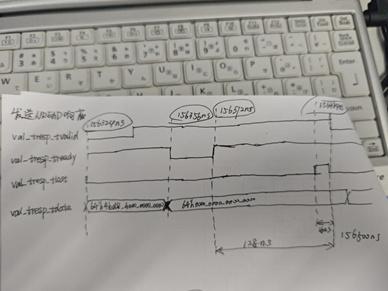

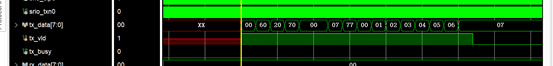

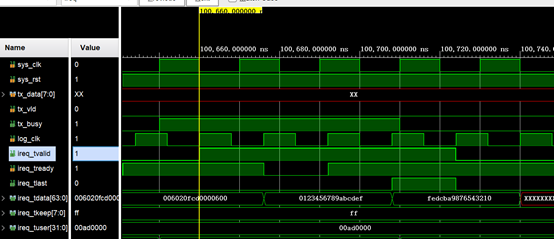

點擊開始仿真,100us時tx_vld正常拉高,tx_data數據傳輸也正常。

ireq信號啟動發送流程,時間大概再100.6us左右,這里幀頭是0x006020fcd0000600,事務類型是SWRITE。

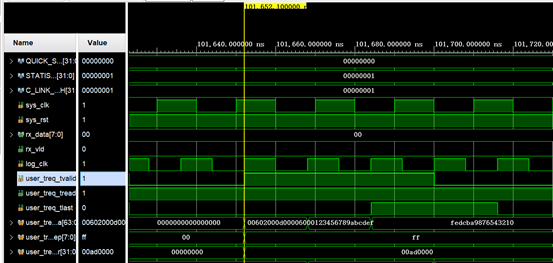

PORTB的接收模塊的treq信號在101.6us左右有動作。

接收模塊輸出的結果如下圖所示,即rx_vld信號拉高之后開始數據接收的數據,不包括SRIO幀頭。

至此,仿真驗證結束,結果符合預期。

本期分享結束,感謝大家看完,私信我可獲取相關源碼工程

)

:組合數據類型——集合類型:創建集合)

)

--字符指針變量,數組指針變量,二維數組傳參的本質,函數指針變量,函數指針數組)