軟件仿真擁有最佳的信號可見性和調試靈活性,被大多數工程師熟練使用,能夠高效捕獲很多顯而易見的常見錯誤。

然而,由軟件實現的數字仿真過程運行速度有限,很難做到100%代碼覆蓋。導致那些深度隱藏的設計問題,將不可避免的逃逸,只能以FPGA在線調試方式解決。

01

為什么全局可觀測能力如此重要

如果說調試是自動化最后的堡壘,那么數據則是調試的生命線。

在很大程度上,代碼是寫出來的,更是調試出來的。

走在異構計算、硬件加速最前沿的EDA硬件輔助驗證行業,一直代表了FPGA調試驗證的最先進水平。

不管是硬件仿真平臺(Emulation)、原型驗證系統(Prototyping),或是最新將兩者功能合二為一的EP1或者P2E,使得FPGA硬件在線調試,像軟件調試一樣,所見即所得。

能夠為用戶提供與軟件仿真類似的100%信號可見性,用于高效定位和修復設計問題。

如果說數字仿真器是為IC設計畫素描,那么用FPGA構建的仿真加速器,則有3D立體克隆效果。但這些昂貴的高端平臺,主要服務需要流片的超大規模IC設計。

近四十年來,始終不能惠及眾多的FPGA應用開發人員。

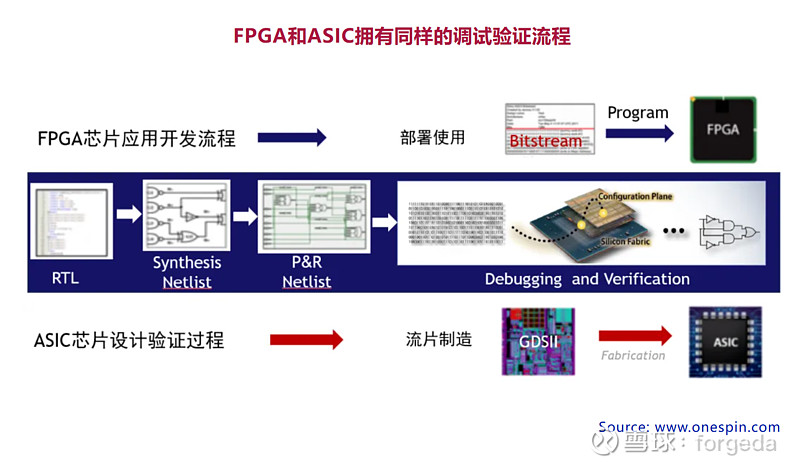

出廠狀態的FPGA芯片,內部只是空白的門海陣列,用戶使用時,是將設計的結果文件,即生成的位流(Bitstream)載入到芯片后,完成硬件電路的配置定制過程,與ASIC芯片的流片生產過程類似。

也被視為價格親民的“ASIC”芯片。

不同的是,對于ASIC芯片設計,用EDA硬件輔助驗證工具進行詳盡的硅前驗證,工程師擁有充足的武器庫,盡可能實現設計的“零缺陷(Zero Bug)”,減少流片失敗風險。

而FPGA用戶應用開發過程中的硬件電路設計,是在自家作坊完成。

可以是團隊,甚至“一人成團”的全棧工程師,完成從設計、調試、驗證等全部生產“制造”流程。

全局可觀測調試能力Full Visibility & Debugging,對提升設計生產力的重要作用,不言而喻。

在軟件行業,如果某個系統是不可觀測的,往往意味著距離“崩潰”不遠了。

一旦真正出現問題,將額外花費工程師解決問題的時間成本。

但FPGA工程師除外,更像是工作常態。

與以往相比,現在的商用FPGA芯片容量規模更大,大量的功能模塊、嵌入式軟件、第三方IP核被集成使用,設計更為復雜。

不同于軟件行業已經有大量工具和越來越多的APIs,構建整個技術棧,硬件行業還相對保守,也更為封閉。

在有限EDA工具支持下,很大程

![華為OD-2024年E卷-字符串化繁為簡[200分] -- python](http://pic.xiahunao.cn/華為OD-2024年E卷-字符串化繁為簡[200分] -- python)

)

比值函數atan2())

-- Java連接redis服務器)