目前FPGA的開發和官方的EDA工具是高度綁定的,用哪家的芯片只能用其配套的EDA工具進行開發(綜合可選工具,布局布線沒有可選的工具),那么有沒有其他的開發方式呢?今天就介紹一個使用開源工具鏈來開發FPGA的方式。

本文核心:開源 FPGA 工具鏈,例如 APIO、IceStrom、yosys OssCAD 等使用。

工具鏈簡介

APIO

簡介:

APIO(Advanced Python Integration for OpenFPGA)是一個基于Python的FPGA開發工具鏈封裝器,旨在簡化開源FPGA工具的使用。它整合了IceStorm、yosys等工具,提供一鍵式編譯、燒錄和調試功能。

官網/GitHub: https://github.com/FPGAwars/apio (注:APIO 是 FPGAwars 社區項目,GitHub 是主要資源庫)

特點:

支持多平臺(Linux/macOS/Windows)。

自動化依賴管理(如自動安裝IceStorm工具鏈)。

支持常見的FPGA開發板(如iCE40、ECP5等)。

提供項目模板和快速構建腳本。

用途:

適合快速原型開發,尤其適合初學者或希望避免手動配置工具鏈的用戶。

IceStorm

簡介:

IceStorm是Lattice iCE40 FPGA的開源工具鏈,包含綜合(yosys)、布局布線(arachne-pnr/nextpnr)、位流生成(icepack)和燒錄工具(iceprog)。

官網: http://www.clifford.at/icestorm/

GitHub: https://github.com/YosysHQ/icestorm

關鍵組件:

Yosys:RTL綜合工具,將Verilog轉換為iCE40支持的網表。

nextpnr:新一代布局布線工具,支持iCE40和ECP5。

iceprog:通過USB燒錄位流到FPGA。

特點:

完全開源,無需商業許可證。

支持低功耗、低成本FPGA開發。

用途:

適用于iCE40 FPGA的開發,如Lattice IceStick、TinyFPGA等開發板。

Yosys

簡介:

Yosys(Yosys Open SYnthesis Suite)是一個開源的RTL綜合工具,支持Verilog/VHDL到目標網表的轉換。

官網: https://yosyshq.net/yosys/

GitHub: https://github.com/YosysHQ/yosys

功能:

邏輯綜合、優化、形式化驗證。

支持多種FPGA架構(iCE40、ECP5、Xilinx 7系列等)。

可擴展的插件系統(如TinyTapeout流程)。

用途:

作為IceStorm和許多其他開源工具鏈的核心綜合引擎,廣泛應用于學術研究和工業項目。

OssCAD(或 OSSCAD)

簡介:

OssCAD(Open Source System for Chip and ASIC Design)是一個開源硬件設計生態系統,強調從RTL到GDSII的全流程工具鏈。

說明: "OssCAD" 并非單一工具,而是開源硬件工具鏈的統稱,指以下生態:

OSSCAD Suite(社區項目): https://github.com/osscda

相關工具鏈(Yosys + nextpnr + OpenROAD):

OpenROAD (ASIC 設計): https://theopenroadproject.org/

關鍵工具:

包含Yosys、nextpnr、OpenROAD(用于ASIC布局布線)、Magic(版圖編輯)等。

支持FPGA和ASIC設計。

特點:

社區驅動,強調開放性和協作。

與商業工具(如Cadence/Synopsys)互補,適合教學和小規模項目。

用途:

ASIC原型設計、FPGA驗證及開源芯片(如RISC-V)開發。

工具鏈關系與典型流程

FPGA開發流程(以iCE40為例):

使用Yosys將Verilog綜合為網表(.blif)。

用nextpnr進行布局布線,生成位流(.asc)。

通過icepack生成二進制文件(.bin),用iceprog燒錄到FPGA。

APIO可自動化上述步驟。

ASIC/OSSCAD流程:

Yosys + OpenROAD + Magic 實現從RTL到版圖的全流程。

其他關鍵鏈接

FPGAwars(APIO 所屬社區): https://fpgawars.github.io/

YosysHQ(Yosys/IceStorm/nextpnr 維護團隊): https://yosyshq.net/

注意事項

部分工具(如 IceStorm/Yosys)已合并到 YosysHQ 組織下統一維護。

開源工具更新較快,建議通過 GitHub 獲取最新版本。

雖然這些軟件在基于 Linux 的發行版或 WSL 中運行效果最佳,但在這里我們將在 Windows(10)上完成所有操作。

步驟 0. 準備系統。

要開始使用工具鏈,系統應該包含 Python 3.5 或更高版本,可以使用以下命令檢查系統上的 Python 版本

$ python --version應該得到這樣的輸出。

如果沒有,需要在系統上下載安裝 python 和 pip。

步驟1. 獲取系統上的 API

系統準備就緒后,我們現在需要在系統上安裝 apio。在 Windows 終端中使用此命令即可輕松完成。

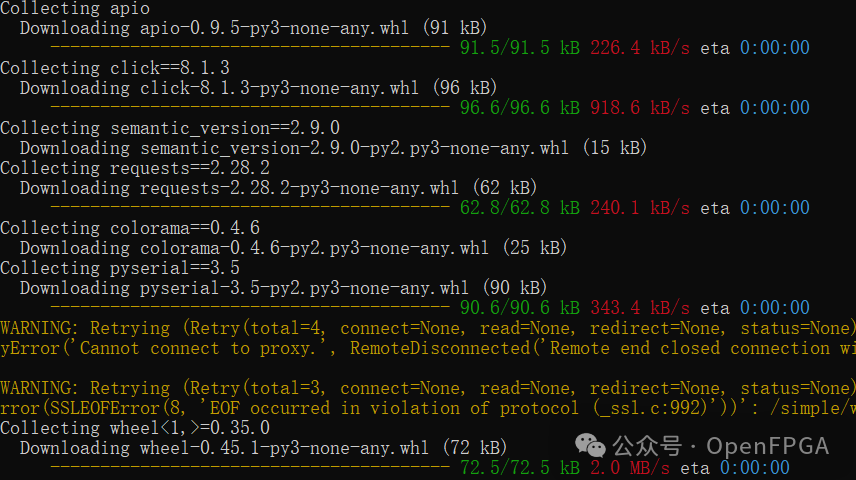

pip install -U apio此命令將下載系統上的 apio,apio 作為將用于 FPGA 開發的所有項目和工具的管理器。

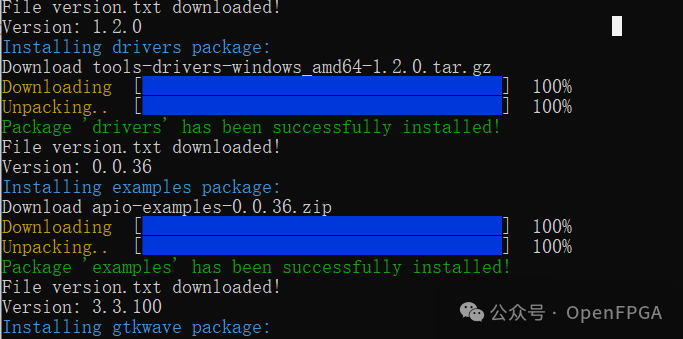

步驟3. 安裝所有軟件(Yosys,GTKwave,nxtpnr)

FPGA 開發過程中使用各種工具,這些是需要的

OSS CAD -Yosys(驗證)

Gtkwave(仿真)

IceStrom

這些軟件可以單獨下載安裝,但我們將使用命令下載完整的包。

apio install --allapio 將開始下載所有支持文件,這可能需要一些時間,具體取決于網絡速度。

可以在此文檔頁面上閱讀 apio 文檔

https://apiodoc.readthedocs.io/en/stable/source/quick_start.html

下載后,可以使用此命令檢查版本。

apio --version這顯示了系統中現有的 apio 版本。

下面這些都是我們將要使用的各種 apio 命令。

$ apio

Usage: apio [OPTIONS] COMMAND [ARGS]...Options:--version ?Show the version and?exit.--help? ? ?Show this message and?exit.Project commands:build ? ? ?Synthesize the bitstream.clean ? ? ?Clean the previous generated files.lint ? ? ? Lint the verilog code.sim ? ? ? ?Launch the verilog simulation.time ? ? ? Bitstream timing analysis.upload ? ? Upload the bitstream to the FPGA.verify ? ? Verify the verilog code.Setup commands:drivers ? ?Manage FPGA boards drivers.init ? ? ? Manage apio projects.install ? ?Install packages.uninstall ?Uninstall packages.Utility commands:boards ? ? Manage FPGA boards.config ? ? Apio configuration.examples ? Manage verilog examples.raw ? ? ? ?Execute commands using Apio packages.system ? ? System tools.upgrade ? ?Check the latest Apio version.可以在apio 的文檔中詳細閱讀這些命令

https://apiodoc.readthedocs.io/en/stable/index.html

安裝 apio 及其所需的所有軟件包后,將在系統中啟用串口和安裝 ftdi 驅動程序,需要在管理員模式下打開 Windows cmd 。

然后運行此命令。

apio drivers --ftdi-enable完成后關閉管理員提示。

到目前為止,無論主板是否受 apio 項目支持,都可以使用此命令找出所有受支持的主板的列表。

apio boards --list步驟4.創建第一個項目

現在研究如何創建我們的第一個項目。

現在打開或創建選擇的文件夾。

完成后,會顯示你想要的位置。

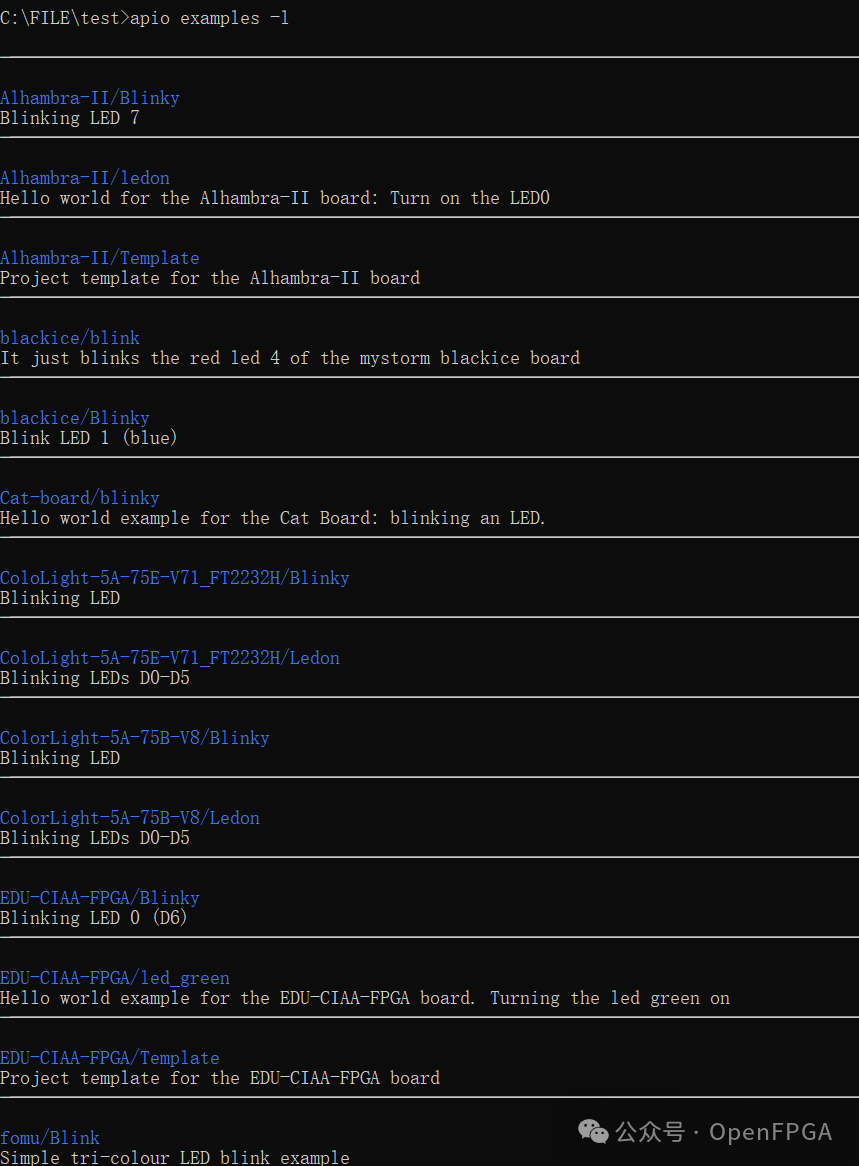

apio 的一大亮點是它自帶了所有支持板卡的示例。現在,我們將在 apio 項目中使用內置的示例文件。使用此命令,我們可以列出所有示例。

apio examples -l應該得到這樣的列表。

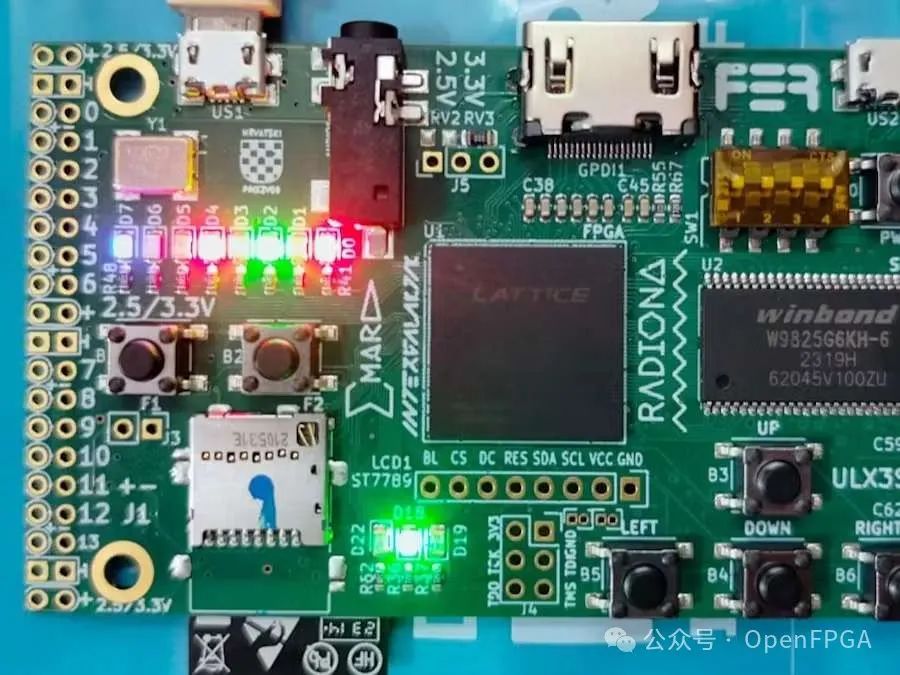

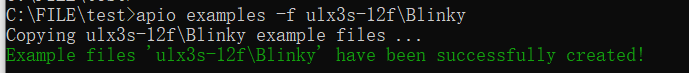

現在我們可以用列表中的示例來對應你的主板。我的主板是 ULX3S- 12f。

因此我將使用該命令來使用示例,可以根據自己板卡對其進行修改。

apio examples -f ulx3s-12f\Blinky如果示例創建成功,將看到如下輸出

該示例文件包含所有需要的 Verilog、Testbench、Simulation 和 Constraints 文件。

現在必須執行以下基本步驟

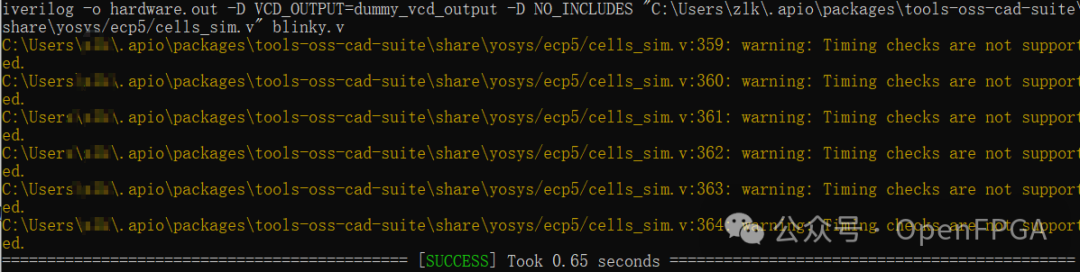

使用命令驗證 Verilog 代碼

apio verify如果所有語法都正確,將獲得如下輸出,因為這是一個示例,所以出現語法錯誤的可能性較小(幾乎為 0)。

驗證完成后,我們需要仿真這段代碼,我們的文件夾必須包含一個測試平臺文件。將使用這個命令進行仿真,并使用 Icarus Veriog 和 GTKwave 進行仿真,這樣我們就能看到波形了。

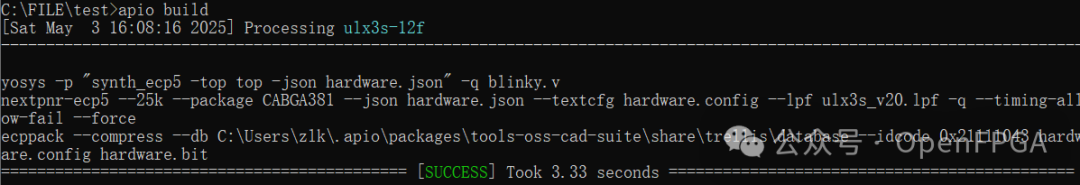

apio sim下一步是為項目構建比特流,使用以下命令完成。

apio build

現在比特流已經生成。我們將把這個比特流上傳到我們的開發板,首先我們需要使用這個命令將開發板連接到我們的電腦,然后運行這個命令。

apio upload恭喜您已成功安裝開源 apio 項目和工具鏈,并創建了一個示例項目。可以通過板上的 LED 閃爍來確認。

總結

簡單且高效,主要是不需要License,如果你對FPGA這一套EDA比較感興趣,那么這套工具也可以研究一下。

另外這一套工具其實也是某平臺官方源碼流出來后魔改的(流傳~)。

最后是一些相關參考資料:

https://apiodoc.readthedocs.io/en/stable/index.html

https://github.com/FPGAwars/apio

https://clifford.at/icestorm

https://www.youtube.com/watch?v=gtkQ84Euyww&list=PPSV

后端的逐元素操作(Per-element Operations))

)

的下一代 SQL 注入自動化漏洞獵手)

)