目錄

1.前言

2.AXI-Stream FIFO時序

3.AXI-Stream FIFO配置信息

4.時鐘控制模塊MMCM

5.ModelSim仿真

6.總結

1.前言

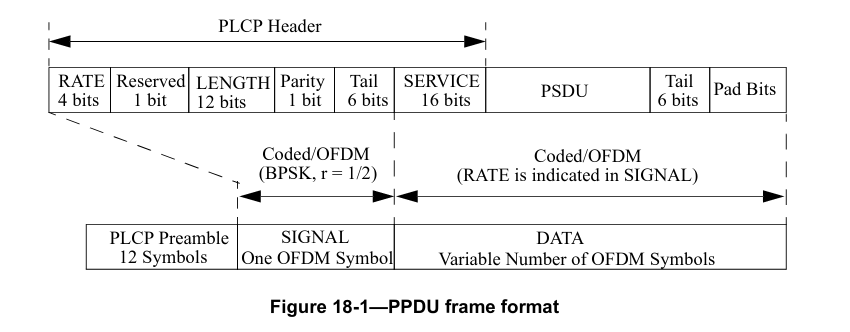

至此,通過前面的文章講解,對于OFDM 802.11a的發射基帶的一個完整的PPDU幀的所有處理已經全部完成,其結構如下圖所示:

PPDU幀結構

PPDU幀結構

接下來還需要完成兩個最為核心的模塊,一是主控模塊,負責與MAC進行數據交互、控制數據流按照上圖所示的幀結構進行輸出;二是在處理數據時,我們采用的是125M的時鐘,而DAC的時鐘是20M的,我們需要對數據流進行降頻處理,使125M的突發式數據流變為20M的連續數據流。

2.AXI-Stream FIFO時序

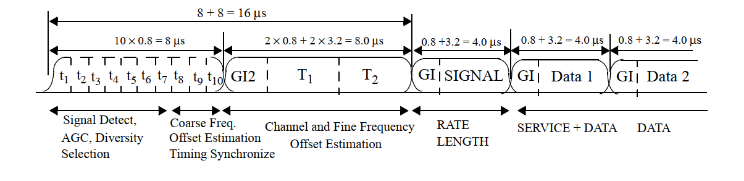

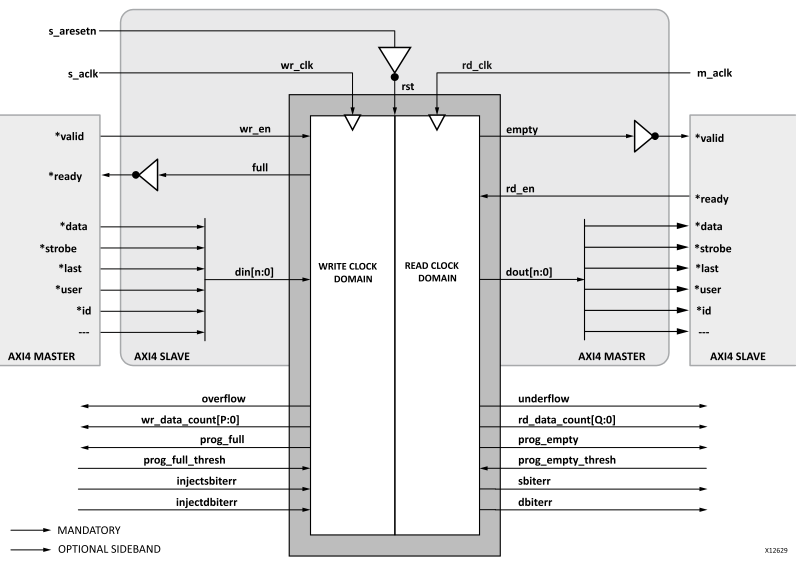

我們在數據處理時,一直使用的都是AXI-Stream協議,所以使用AXI-Stream FIFO進行跨時鐘域都不需要再進行額外的操作,直接連上就能用。但是為了讓大家對AXI-Stream協議有更深的理解,以及掌握AXI-Stream FIFO的使用方法,接下來還是詳細講講AXI-Stream FIFO這個IP核。其輸入輸出形式如下:

AXI-Stream FIFO

在AXI協議中,數據通過寫通道實現master到slave的傳輸,讀通道實現slave到master的傳輸。因此,在FIFO IP核中,接收數據的端口S_AXIS用來將數據寫入IP核,而發送數據的端口M_AXIS用來將數據讀出IP核。

舉個生活中的例子來讓大家便于理解FIFO:在數據的傳輸中當讀速率慢于寫速率時,FIFO便可被用作系統中的緩沖元件或隊列,類似于水流經過一個緩沖區,上游水流速度快,下游水流速度慢,部分水就可以被緩存在中間的緩沖區。

流水類比FIFO

AXI接口協議使用雙向valid和ready握手機制。數據源使用valid信號來顯示何時在信道上可獲得有效數據或控制數據。數據目的地使用ready信號來顯示何時可以接受數據。

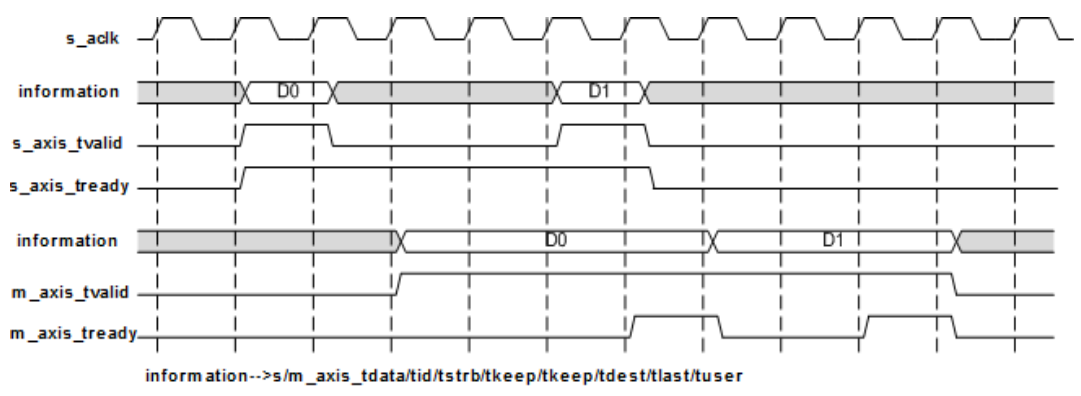

下圖顯示了AXI4-Stream FIFO的寫入和讀取操作的示例時序圖:

AXI-Stream FIFO時序圖

在上圖中,數據源生成valid信號以指示數據何時可用。目的地生成ready信號以指示其可以接受數據,并且僅當有效信號和就緒信號均為高時才發生傳輸。

AXI FIFO是普通FIFO的應用,它們之間的許多行為是相同的。ready信號是根據 FIFO 中的空間可用性生成的,并保持在高電平以允許寫入FIFO。僅當FIFO中沒有空間可供執行額外寫入時,ready信號才會拉低。 valid信號是根據FIFO中數據的可用性生成的,并保持為高電平以允許從FIFO執行讀取。僅當沒有數據可供從FIFO讀取時,valid信號才會拉低。數據信號被映射到本機接口 FIFO 的 din 和 doout 總線。AXI FIFO 的寬度是通過連接 AXI 接口的所有數據信號來確定的。 數據信號包括除有效和就緒握手信號之外的所有 AXI 信號。

AXI FIFO Derivation

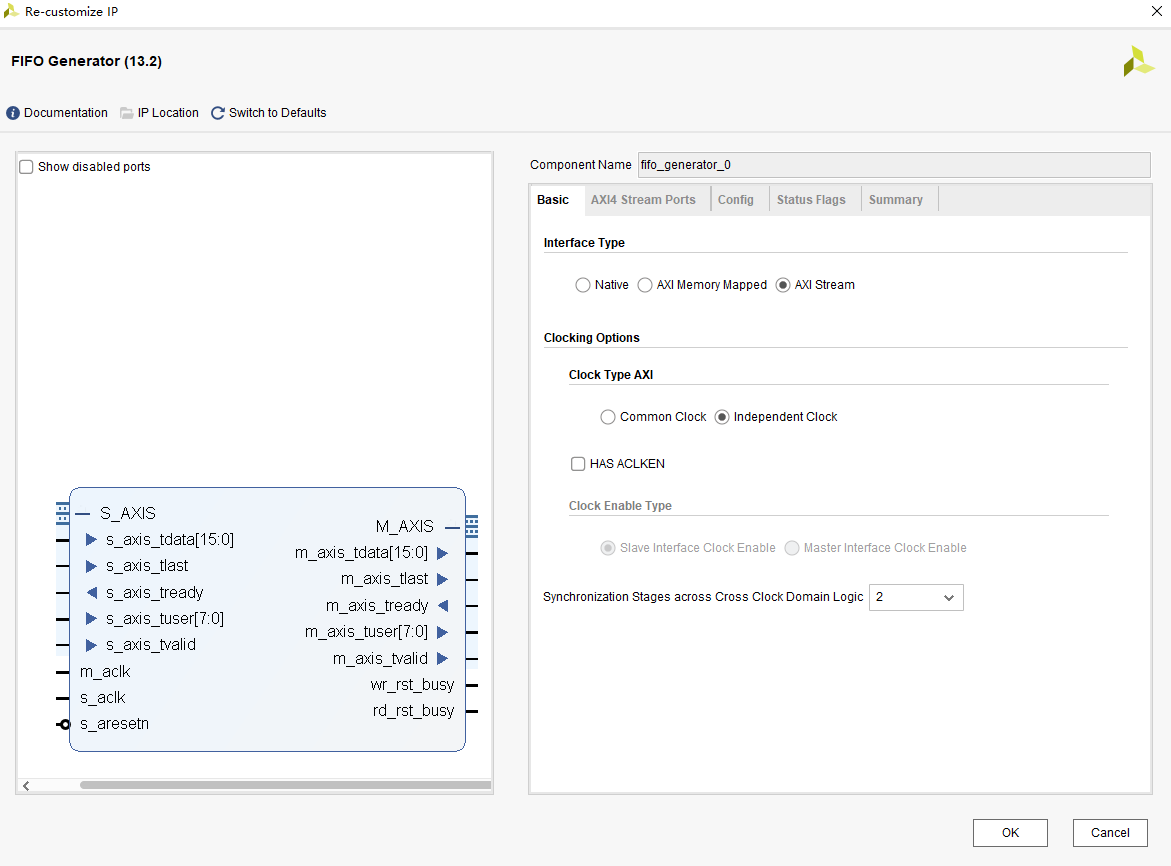

3.AXI-Stream FIFO配置信息

如下圖所示,是IP核的配置界面:

FIFO配置界面

關于IP核中各個信號的詳解,可翻閱官方手冊,以下對該實驗中所需信號進行解釋:

Basic:

Interface Type : FIFO的模式,選擇AXI-Stream;

Independent clocks:獨立時鐘設置,該實驗需要使用異步時鐘;

其余保持默認即可。

AXI-Stream Ports:

TDATA NUM BYTES:選擇兩個字節,因為IFFT輸出是16bit;

TUSER WIDTH:設置為8;

TLAST:勾選;

其余保持默認即可。

Config:

FIFO depth:FIFO深度,可選范圍16-32768,必須為2的整數次冪,根據需要設定為512,因為125/20 * 80=500;

其余保持默認即可。

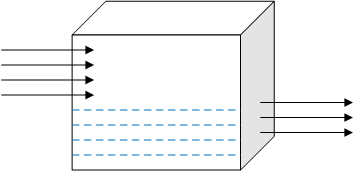

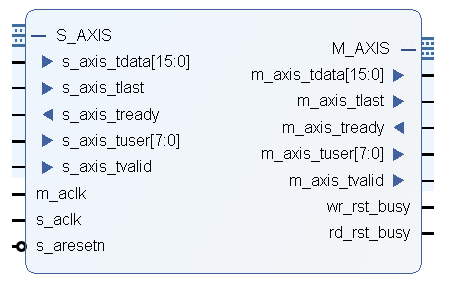

配置好,接口如下所示:

AXI-Stream FIFO

4.時鐘控制模塊MMCM

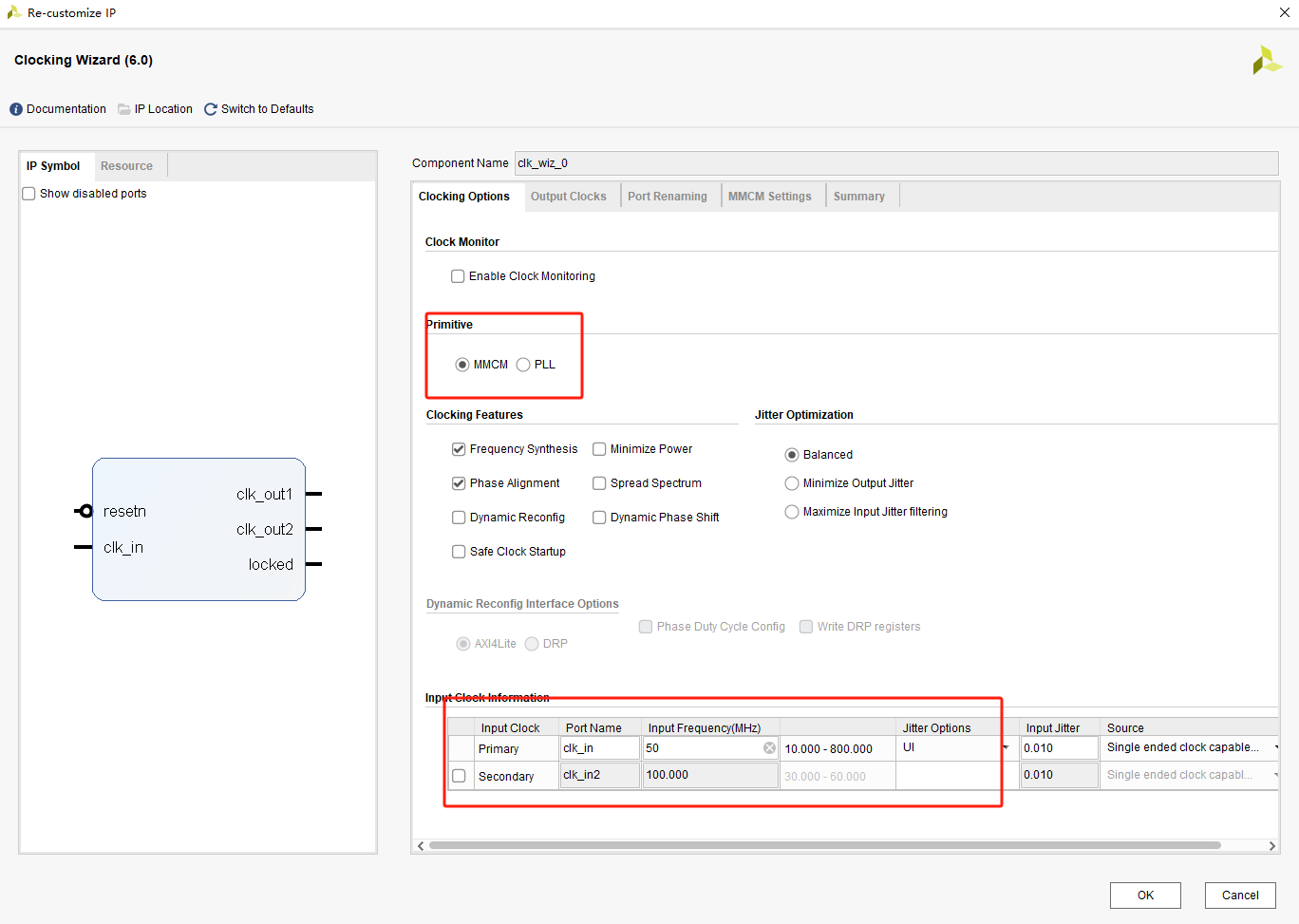

設計采用的開發板為ZYNQ7020,芯片是xc7z020clg400-1,板載時鐘為50M,需要通過鎖相環得到125M和20M的時鐘。Clocking Wizard IP核的配置界面如下:

Clocking Options

Clocking Options:選擇MMCM,輸入時鐘填寫50M。

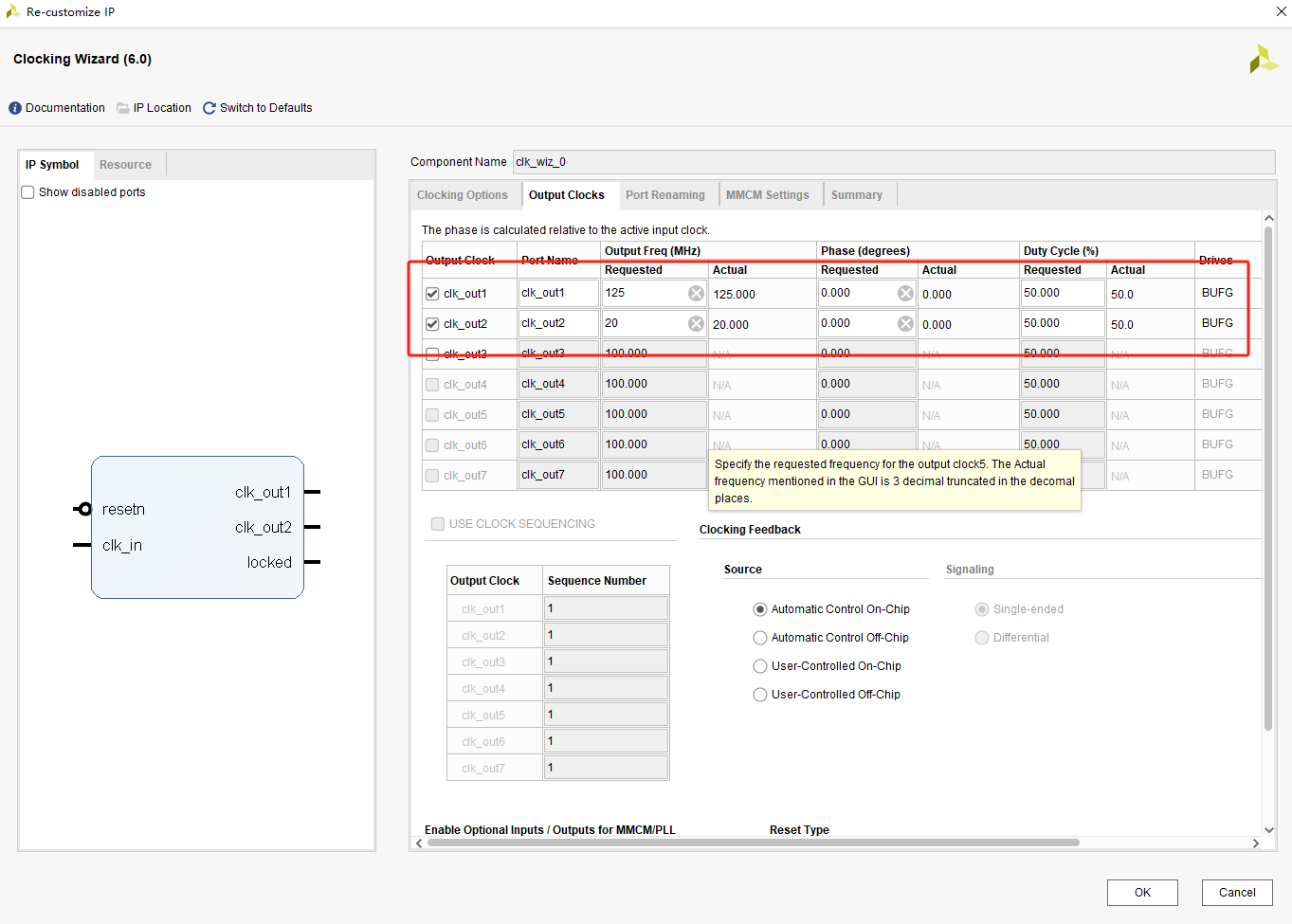

clk_out為125M,clk_out2為20M

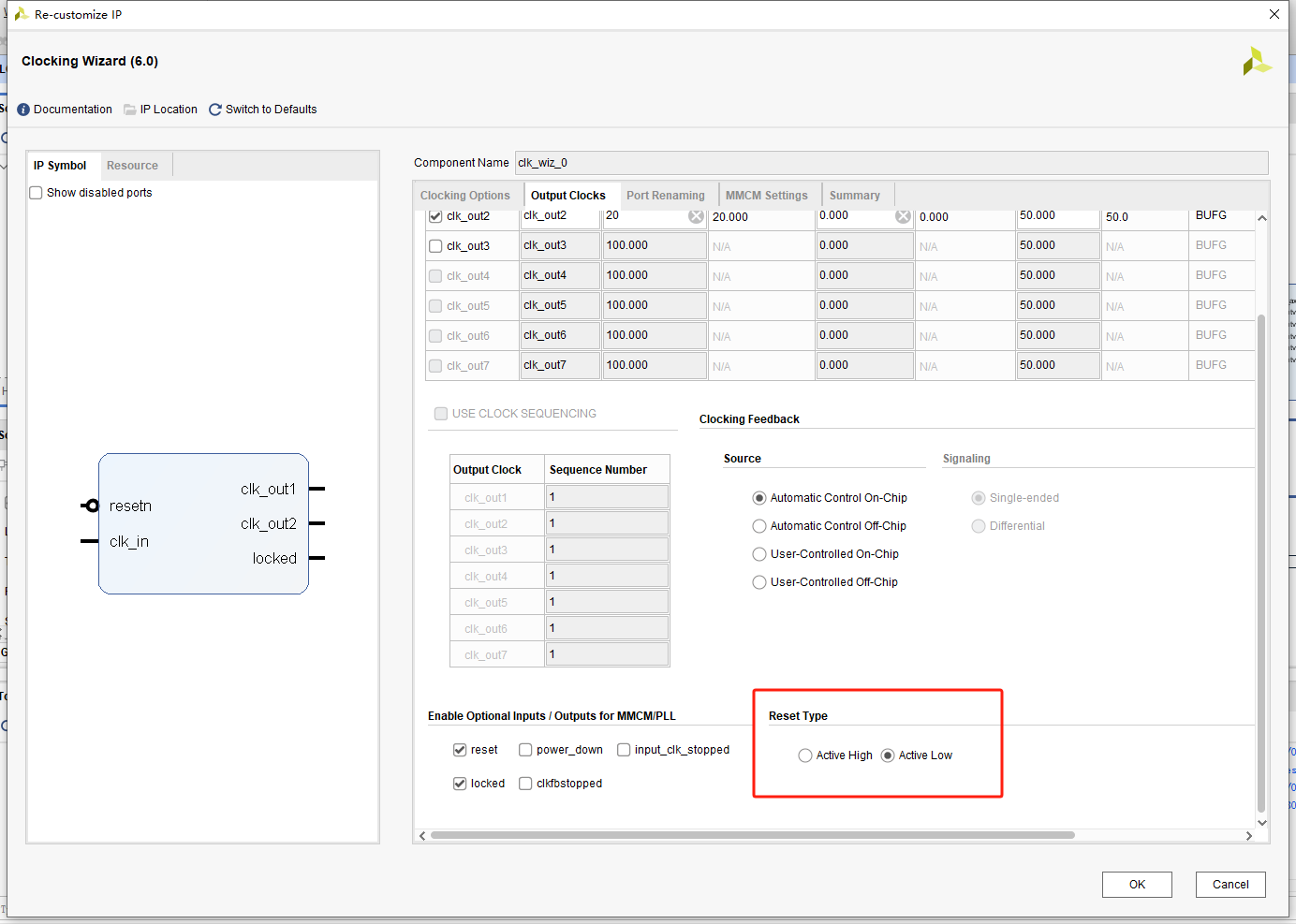

低電平復位

Output Clocks:填寫clk_out為125M,clk_out2為20M。并選擇低電平復位。

5.ModelSim仿真

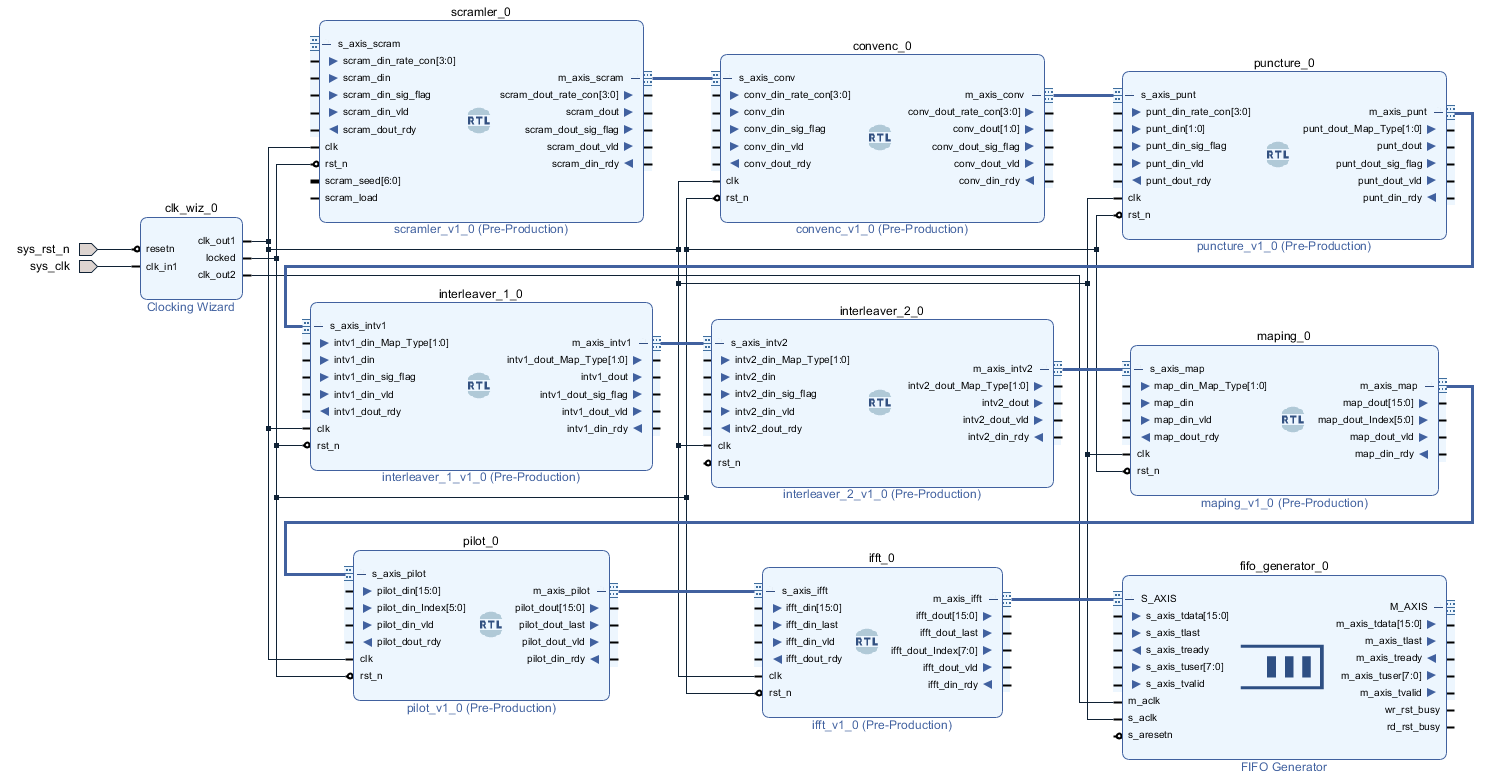

和之前的模塊一起,按照如下連接,進行仿真,這里省略了并串轉換。

仿真模塊連接圖

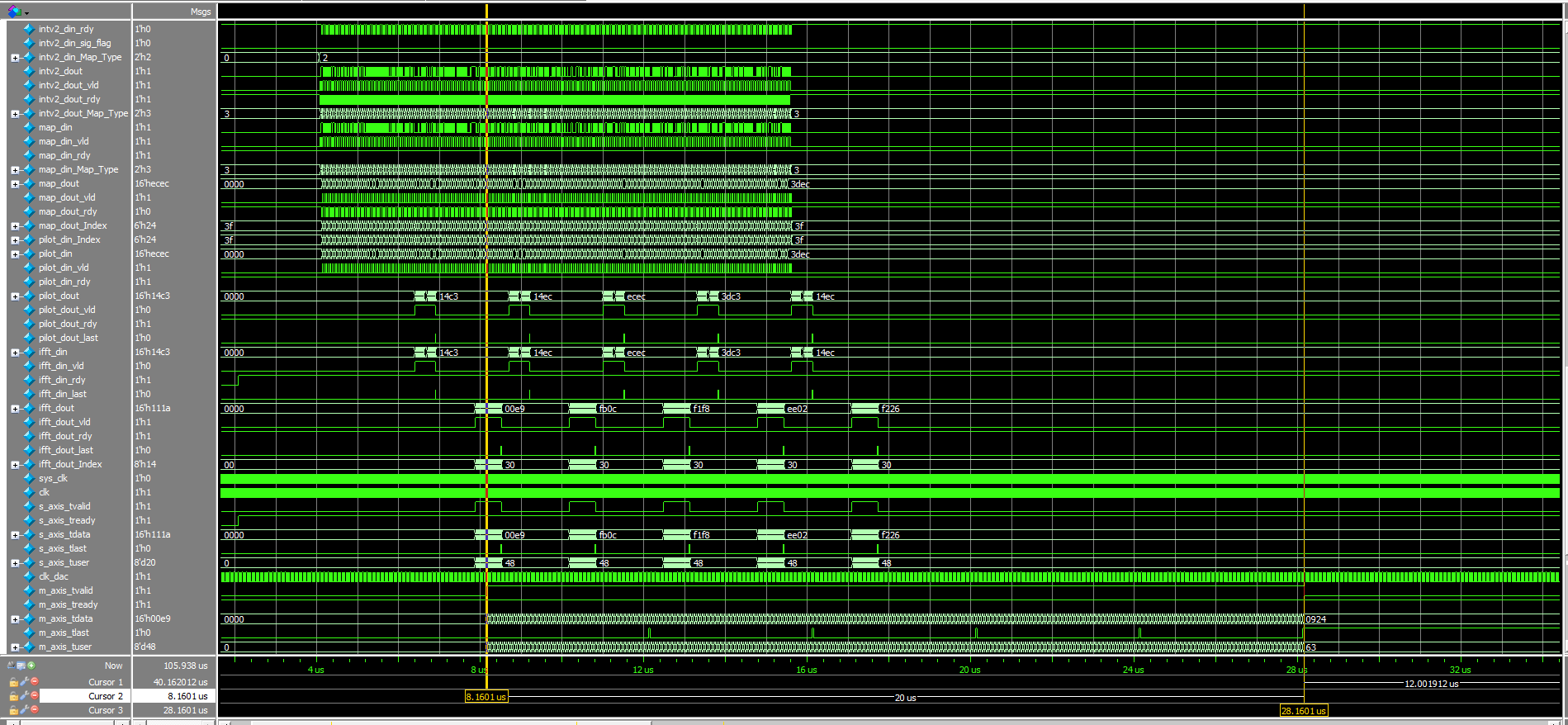

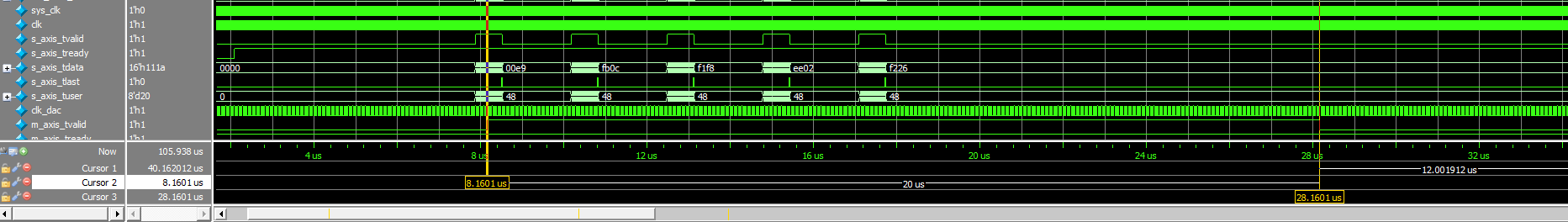

測試數據選擇5個OFDM符號,使用16-QAM調制,編碼效率為3/4,一共720個bit。仿真結果如下:

仿真全局截圖

仿真局部截圖

5個OFDM符號輸出的時間剛好為20us,說明是連續輸出的,即滿足了協議中符號之間不留間隙。

6.總結

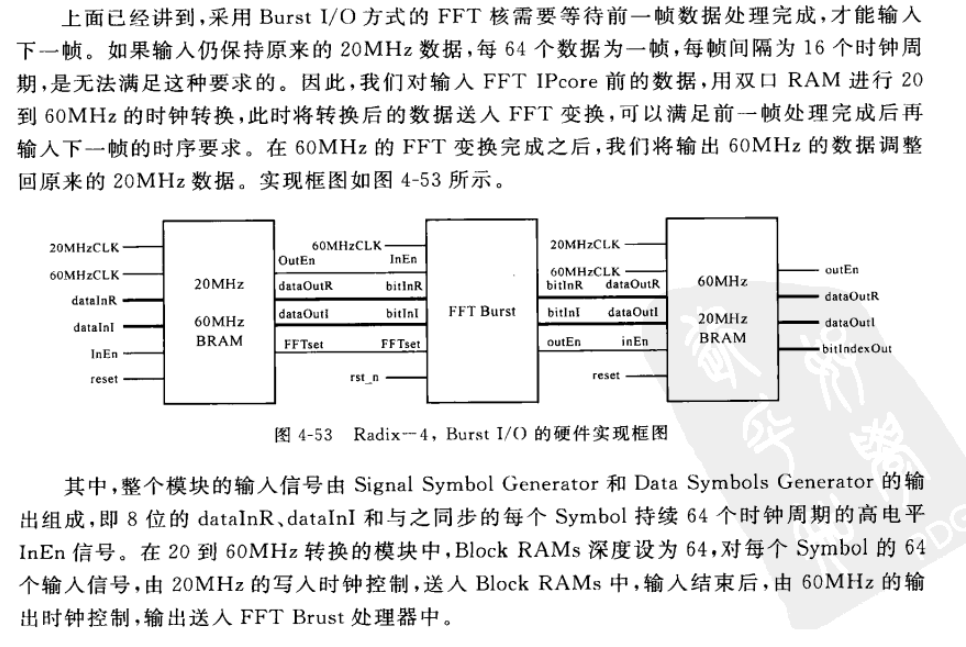

使用AXI-Stream協議處理數據流,下游模塊數據沒處理好會對上游進行反壓,上游數據沒處理完,不會往下游傳輸,可以很方便且高效的對數據進行流水線處理。個人認為相比于書籍《基于XILINX FPGA的OFDM通信系統基帶設計》中方法要可靠得多。

![]()

書中的實現方法

網上大多數博客都是根據書中的這種,不斷變換時鐘進行跨時鐘域處理來做這個項目,個人認為不是很可靠,所以從頭開始采用了AXI-Stream協議處理數據流的方式來寫。如果有什么不正確的地方,或者不理解的歡迎和我討論。

原文鏈接(相關文章合集):OFDM 802.11a的xilinx FPGA實現

)

數據技術篇之數據同步)

)

![[JDK工具-6] jmap java內存映射工具](http://pic.xiahunao.cn/[JDK工具-6] jmap java內存映射工具)

的使用)