痕量分離;長度平行度;stackup:有沒有一個脫穎而出?

我已經有一段時間沒有看到關于串擾的文章了,所以我決定借此機會為那些可能對為什么精通串擾的 PCB 設計人員和硬件工程師使用各種設計規則來控制串擾感興趣的 PCB 設計社區中的人簡要介紹一下這個主題。在此過程中,我們將確定哪些設計調整為控制遠端串擾提供了最大的杠桿作用。

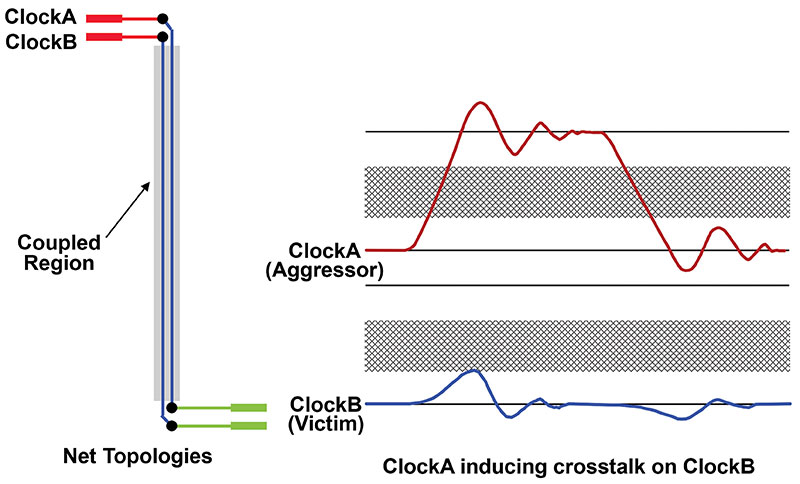

串擾是信號之間產生的不需要的噪聲。當 PCB 上的兩個或多個網絡通過電磁方式相互耦合時,就會發生這種情況(即使它們在導電上根本沒有連接)。這種耦合可能發生在兩個網絡彼此相鄰運行任何重要長度的任何時候。當信號在其中一條線路上驅動時,它產生的電場和磁場會導致意外信號也出現在附近的線路上,如圖?1 所示。

?

圖 1.?當兩個或多個相鄰跡線耦合在一起時,就會發生串擾。

許多因素結合在一起會產生不需要的串擾信號:走線耦合的長度、走線之間的距離、它們在 PCB 疊層中的位置、“干擾源”和“受害者”線路上使用的驅動器 IC、線路是否端接等。

除非進行仿真,否則串擾是一種特別難以預測和控制的現象,因為幾乎沒有辦法直觀地知道給定耦合會產生多少串擾電壓和電流。盡管如此,半保守的設計指南可能是有用的,盡管幾乎總是以犧牲電路板空間為代價。

在串擾術語中,“aggressor” 信號或走線會切換并導致串擾。“受害者” 信號或跟蹤通過產生意外信號來響應。效果本質上是三維的。受害者可以在同一層相鄰,也可以在攻擊者的上方或下方(圖 2)。

?

圖 2.?受害網可以位于侵略網的上方、下方或附近。

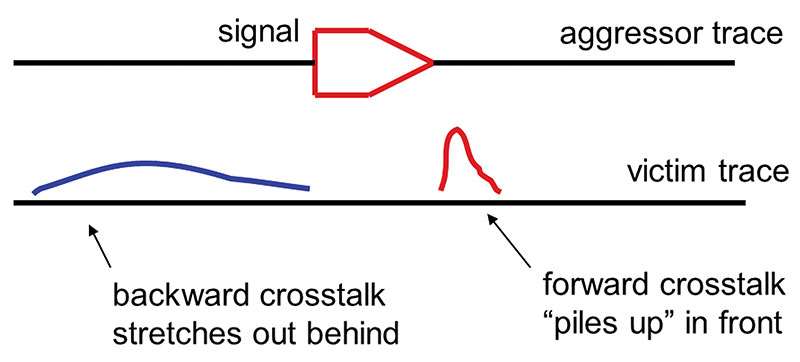

實際上,受害者網絡上施加了兩個耦合信號:一個正向信號和一個反向信號。“向前”脈沖與干擾源信號一起傳播,而“向后”脈沖則從干擾源信號向后傳播。受害者遠端的串擾稱為“遠端串擾”或 FEXT,近端的耦合電壓稱為“近端串擾”(NEXT)。圖 3?顯示了正向和反向串擾。倒車信號通常在從駕駛員反射后最終向前傳播。

?

圖 3.?受害者跡線上的前向和后向串擾圖示。

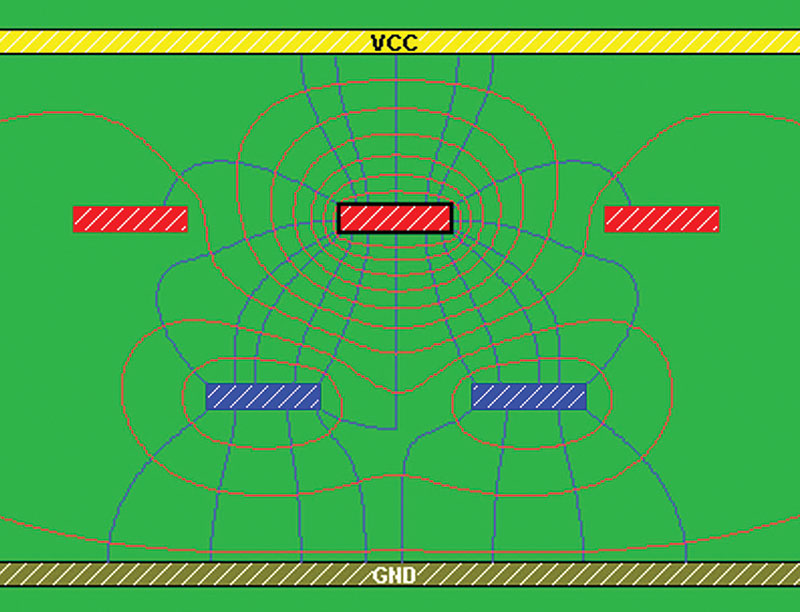

電流通過電場(與圖 2 中的走線正交的線路)注入受害者,這是由攻擊者和受害者網絡之間的電容耦合相互作用引起的。這些相互作用受導體表面積和距離的影響,通常終止于相鄰導體。磁場在受害者身上感應出電壓。這些是感應(變壓器)耦合相互作用,有點圓形——圍繞著攻擊者和受害者網絡。這些相互作用通常不會被導體阻止,因此可以圍繞多個相鄰導體擴展。

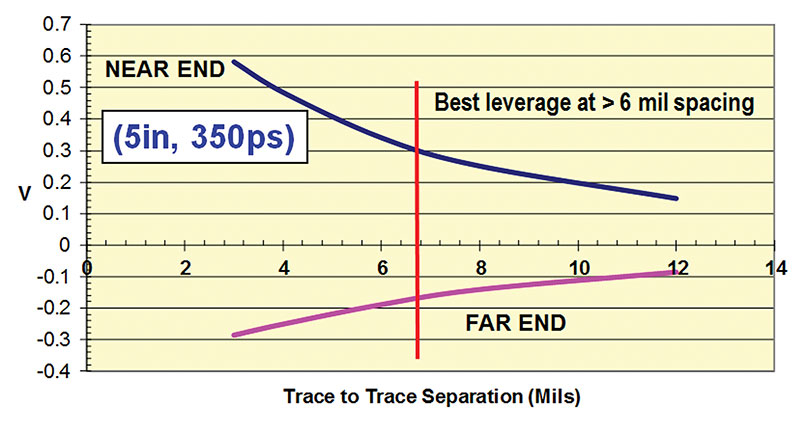

串擾指南。最常見的串擾設計規則涉及跡線到跡線分離。例如,PCB 設計人員可以將 auto-router 設置為 4-mil 走線寬度和 4-mil 間距。當然,這將最大限度地提高 router 的完成度,但最終設計將產生 20 至 60mV 的串擾。將噪聲敏感的受害者調整為超過 6 mil 的走線間距可以幫助避免這個問題(圖 4)。

?

圖 4.?該圖使用兩條平行的 5 英寸線,顯示 NEXT 和 FEXT 的曲線在攻擊者網絡和受害者網絡之間大約 7 mil 的間距處開始變平。垂直線左側的間距越窄,串擾越多,垂直線右側間距越大,好處越小。

由于電場終止于參考平面,因此靠近參考平面的走線減少了串擾。電容性走線到走線耦合與參考平面的距離呈二次方下降,因此與距離最近參考平面 6 mil 或更多 mil 的走線相比,參考平面 4 mil 范圍內的走線更不受串擾的影響。對稱帶狀線 - 因為它們不是一個,而是兩個參考平面 - 比微帶信號具有相對更高的抗擾度。

此外,還需要考慮介電常數效應。高介電常數 (Dk) 使電場集中,導致串擾性能相對較差,在 Dk 和電容串擾之間大致呈線性關系。

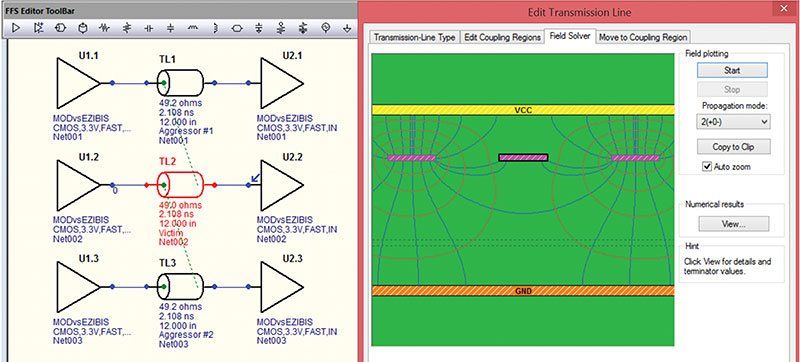

示例:總線上的串擾。?假設您正在設計一條總線,并希望保證任何信號上都不會發生超過200mV的串擾。以下是開發適當的 routing constraints 以實現它的過程。現代數字系統中的典型總線包含許多物理并行的走線 – 16、32、64 – 甚至更多信號。但是,要分析此類總線上的串擾,您可以將范圍縮小到單個 “victim” 跡線,兩端都有 “aggressor” 網絡。

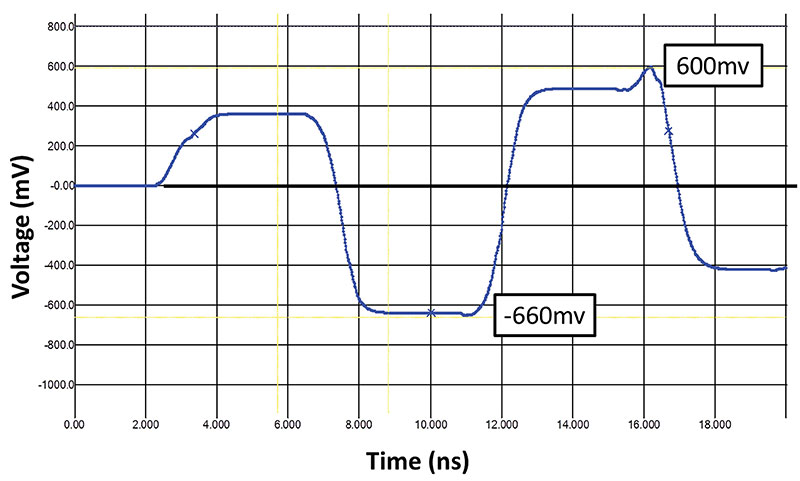

讓我們從耦合的共面 6.0 mil 寬 (W) 帶狀線開始,通過高度為 5.0 mil (H) 的 4.3 Dk 電介質,平行運行12 英寸,走線間距為 8.0 mil (S)(圖 5)。使用 HyperLynx LineSim 進行模擬(圖 6)顯示了遠端串擾,以查看初始排列中發生了多少串擾。在兩個干擾源網絡上的驅動器切換速度為 590ps (0.59ns),并且沒有在受擾網絡上注入信號,正極約 600mV 的受擾波形將被注入,負極的 660mV 將被注入 – 兩者都遠遠超過了我們 200mV 最大串擾的設計標準。

?

圖 5.?串擾很容易用所示的 aggressor-victim-aggressor 示例來說明。(與 Mentor 的 HyperLynx LineSim 一起顯示。

?

圖 6.?受害網絡上的遠端串擾 (FEXT) 如圖 5 所示。

串擾是一種復雜的效應,受許多不同的幾何因素影響:例如,驅動器 IC 技術(Tr、Tf、輸出阻抗和驅動強度)、走線寬度 (W)、銅重量 (T)、平行線長度 (Lp)、走線分離 (S)、PCB 疊層 [層排序、Dk 和介電厚度 (H)]和線端端接。(串擾通常需要比單線反射更復雜的端接。存在控制串擾的經驗法則,但要在控制特定設計成本的同時最大限度地減少串擾,需要一個好的仿真工具。在下一節中,我們將通過一個迭代過程來處理圖 5 和圖 6 中設計的串擾,看看是否出現了一些合理的設計規則。

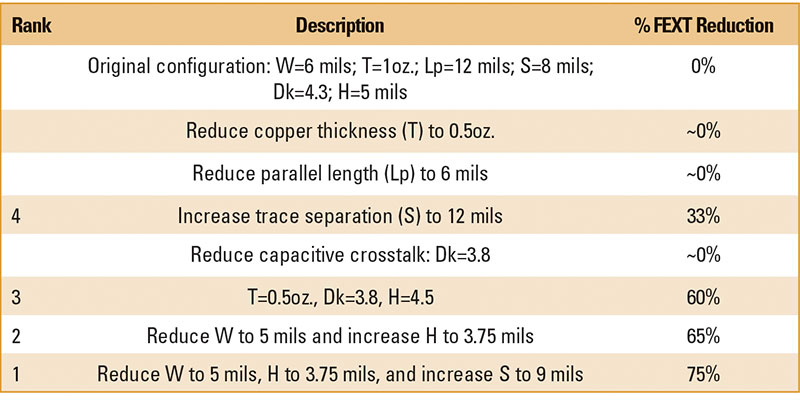

串擾減少技術。有時可能被忽視的串擾杠桿是銅的厚度。在上面的示例中,信號使用了 1 盎司的銅。這對于 signal trace 來說很粗。有人可能會認為減小銅厚度會降低電容耦合,盡管仿真表明結果在實踐中并不顯著。盡管如此,在本次討論的其余部分,我們將使用更常見的 0.5 盎司銅。

減少串擾的一種可能技術是減少攻擊者和受害者彼此平行的長度。這在布線方面帶來了一些實際問題——這些走線在電路板上是平行的,這是有原因的——但看看當并聯耦合區域從 12.0“ 減少到 6.0” 時會發生什么是有指導意義的。令人驚訝的是,這根本沒有減少串擾;它只是在時域中將峰值串擾幅度向左移動。作為串擾杠桿,僅減少并行性并不像我們想象的那么強大。

減少串擾的另一種常見方法是增加走線之間的分離 S。將走線間隔從 8 mils 增加到 12 mils 將正側的串擾降低到 400mV,將負側的串擾降低到 -400mV – 仍然遠遠超出我們想要的水平,在進行此更改的過程中,我們使用了更多的電路板空間。

除了 trace separation 和 length parallelism 之外,還有很多方法可以影響串擾。有時被忽視的是 PCB 疊層。回想一下,我們從 Dk=4.3 開始。如果我們嘗試使用低 Dk 材料(比如 D=3.8)來減少電容串擾,會發生什么情況?通過模擬,事實證明,僅此更改帶來的改進可以忽略不計。然而,在使用 0.5 盎司銅并降低電介質的 Dk 的過程中,走線阻抗從大約 50Ω 增加到略低于 57Ω。(請記住:阻抗與走線電容的平方根成反比,走線電容與電介質的 Dk 有關。因此,將目標帶狀線層和最近的參考平面之間的介電厚度 (H) 從 5.0 mils 減小到 4.5 mils,電容再次增加,將阻抗拉回 50Ω 左右。這些因素的結合使我們更接近目標,導致正側的 211mV 降至負側的約 230 mV – 超過 60%,但仍高于我們的 200mV 目標。

減小走線寬度 (W),從而增加阻抗 (Z0),然后縮小介電厚度 (H) 以將阻抗拉回 50Ω 左右,這是減少串擾的另一種可能方法。將 W 降低到 5.0 mils,將 H 降低到 3.75 mils,會產生大約 200mV 的正和負串擾。

通過將走線寬度 (W) 縮小 1.0 mil,總總線寬度(以 mils 為單位)減少了位數減 1。為了獲得更多的裕量,同時保持初始設計中的總線總寬度,在間距上再增加一個mil(即,將S從8.0 mils增加到9.0 mils)會產生大量的裕量:正側為160mV,負側為170mV。

表 1?總結了對圖 5 中拓撲的影響,以及它們對 FEXT 的相對影響,按最壞情況下串擾的相對減少排序。

?

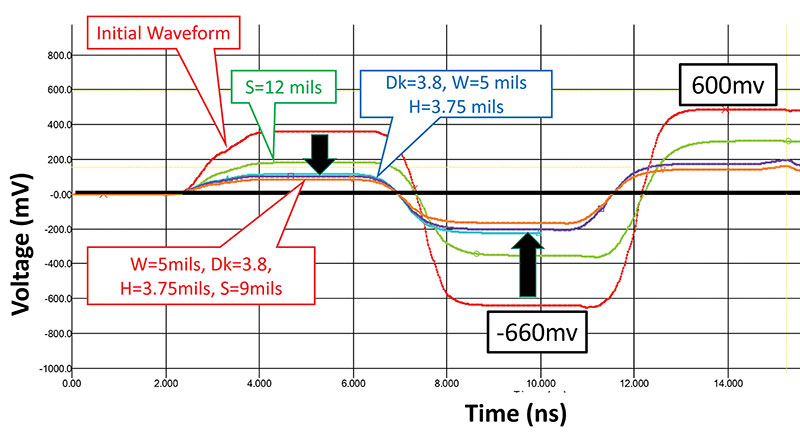

圖 7 顯示了減少這種特定總線設計中串擾的前四種方法。最終的設計規則是使用 W=5.0 mils、Dk=3.8、H=3.75 mils 和 S=9.0 mils。

?

圖 7.?減少圖 5 總線設計中串擾的四種主要方法。得到的設計規則是 W=5.0 mils,Dk=3.8,H=3.75 mils,S=9.0 mils。

離別的思念。?在過去的 10 年里,我一直在與工程師和 PCB 設計師交談,我聽到了很多關于使用更薄的電介質的參考資料,因此對于一些讀者來說,本文的內容可能是評論。但我還沒有看到一篇文章比較了用于控制串擾的不同杠桿,強調材料選擇,特別是層壓板厚度在控制遠端串擾 (FEXT) 中起著最關鍵的作用。

在以后的專欄中,我將詳細介紹更緊密的電場耦合到最近的參考平面的工作原理,并附帶一些視覺效果,也許還會回顧麥克斯韋方程組。

引用

1. Bill Hargin,《印刷電路手冊》,第 7 版,McGraw-Hill Education,第 20 章,2016 年。

?

SQL數據庫)

)

![[Java 基礎]正則表達式](http://pic.xiahunao.cn/[Java 基礎]正則表達式)