一、緩存機制基礎

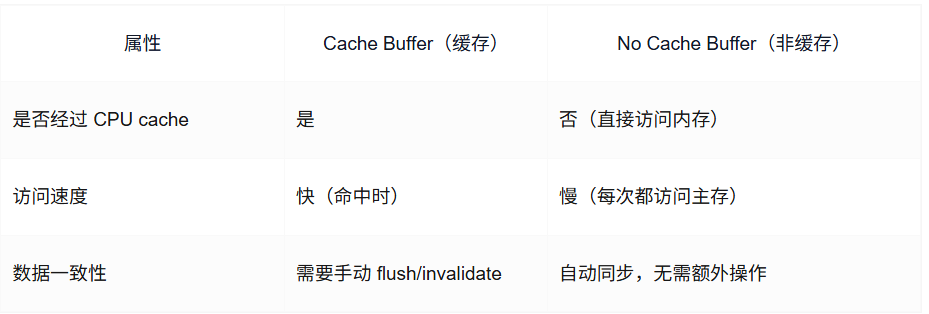

1.1 緩存類型對比

1.2 典型應用場景

緩存緩沖區 :適用于高頻 CPU 訪問場景(如 AI 推理中間數據)

非緩存緩沖區 :適用于設備直傳場景(如 DMA 數據流)

二、數據一致性問題深度解析

2.1 DMA-CPU 緩存協同問題

當 DMA 設備與 CPU 緩存系統協同工作時,可能引發以下同步異常:

場景現象后果CPU寫入未FlushDMA讀取到過期數據處理結果基于舊數據DMA寫入未InvalidateCPU使用緩存舊數據計算邏輯錯誤并發訪問未同步內存與緩存數據不一致系統穩定性風險

典型異常表現 :

感知輸出圖像中出現非連續綠色偽影(數據不同步導致的像素錯位)

三、緩存管理技術方案

3.1 手動緩存控制接口

// CPU寫入后執行Cache刷新(確保DMA獲取最新數據)

int32_t hb_mem_flush_buf_with_vaddr(uint64_t virt_addr, uint64_t size);// DMA寫入后執行Cache失效(確保CPU讀取最新數據)

int32_t hb_mem_invalidate_buf_with_vaddr(uint64_t virt_addr, uint64_t size);

3.2 自動化緩存配置

1.輸入緩沖區配置

“in_buf_noclean”: 0 # 0=自動執行 flush(默認 1 不執行)

“in_buf_noncached”: 0 # 0=使用緩存內存(默認)

2.輸出緩沖區配置

“out_buf_noinvalid”: 0 # 0=自動執行 invalidate(默認 1 不執行)

“out_buf_noncached”: 0 # 0=使用緩存內存(默認)

四、配置策略建議

4.1 性能敏感場景

“in_buf_noclean”: 1 # 關閉自動 flush

“out_buf_noinvalid”: 1 # 關閉自動 invalidate

適用場景:高頻數據流(>60fps 視頻流)

注意事項:需配合手動緩存控制接口使用

4.2 數據安全場景

“in_buf_noclean”: 0 # 強制自動 flush

“out_buf_noncached”: 1 # 使用非緩存內存

適用場景:自動駕駛感知推理場景

性能影響:增加約 15-20%的 CPU 開銷

五、最佳實踐指南

混合使用策略 :對處理流水線中的中間緩沖區采用 Cache Buffer,終端輸出使用 No Cache Buffer

五、最佳實踐指南

混合使用策略 :對處理流水線中的中間緩沖區采用 Cache Buffer,終端輸出使用 No Cache Buffer

批處理

)

操作函數remap())