1. 時鐘的概念

時鐘是由電路產生的具有周期性的脈沖信號,相當于單片機的心臟,要想使用單片機的外設必須開啟時鐘。

時鐘對單片機有什么作用?

? ? ? ? 1. 驅動外設的本質是寄存器,而寄存器需要時鐘觸發才能改寫值。

? ? ? ? 2. 時鐘頻率越高,CPU在相同的時間能夠執行更多的指令,運行速度更快。

2. 時鐘樹

?STM32微控制器芯片上的時鐘分配和控制結構,它定義了各種時鐘源、時鐘分頻、時鐘分配等,形成一個樹狀結構。

時鐘樹的作用?

1. 給相對獨立的外設模塊提供時鐘,不同的外設需要的時鐘頻率不一致,需要通過時鐘樹分配相應的時鐘。

?2. 降低整個芯片的功耗, 所有外設時鐘默認都是關閉狀態(disable)當我們使用某個外設就要開啟這個外設的時鐘(enable) ,沒有讓所有外設都使用高速時鐘造成浪費。?

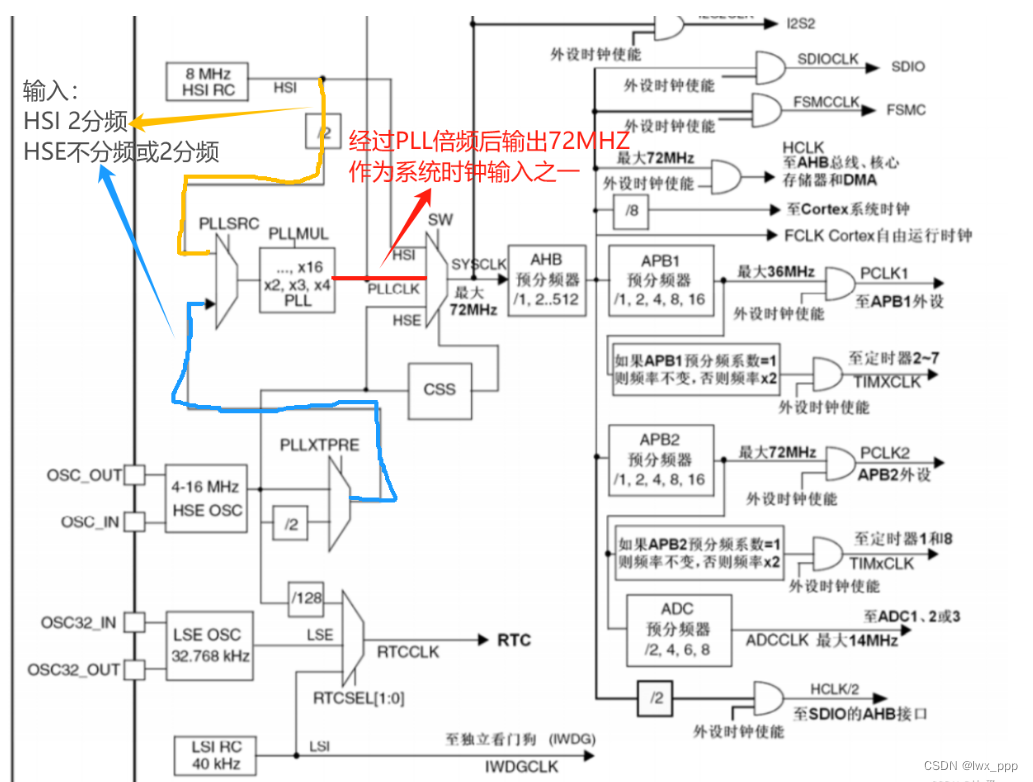

2.1 時鐘源

STM32總共有四個時鐘源為什么要有四個時鐘源,兼容不同速度的外設, STM32的四個時鐘源分別為HSE, LSE, HSI, LSI。

HSE時鐘:高速的外部時鐘。

來源: 無源晶振,通常使用8M, STM32F1系列為(4~16M)

作用:可不分頻或2分頻(頻率/2)作為PLL鎖相環的輸入,還可直接不分頻作為系統時鐘,128分頻作為外設RTC時鐘的輸入

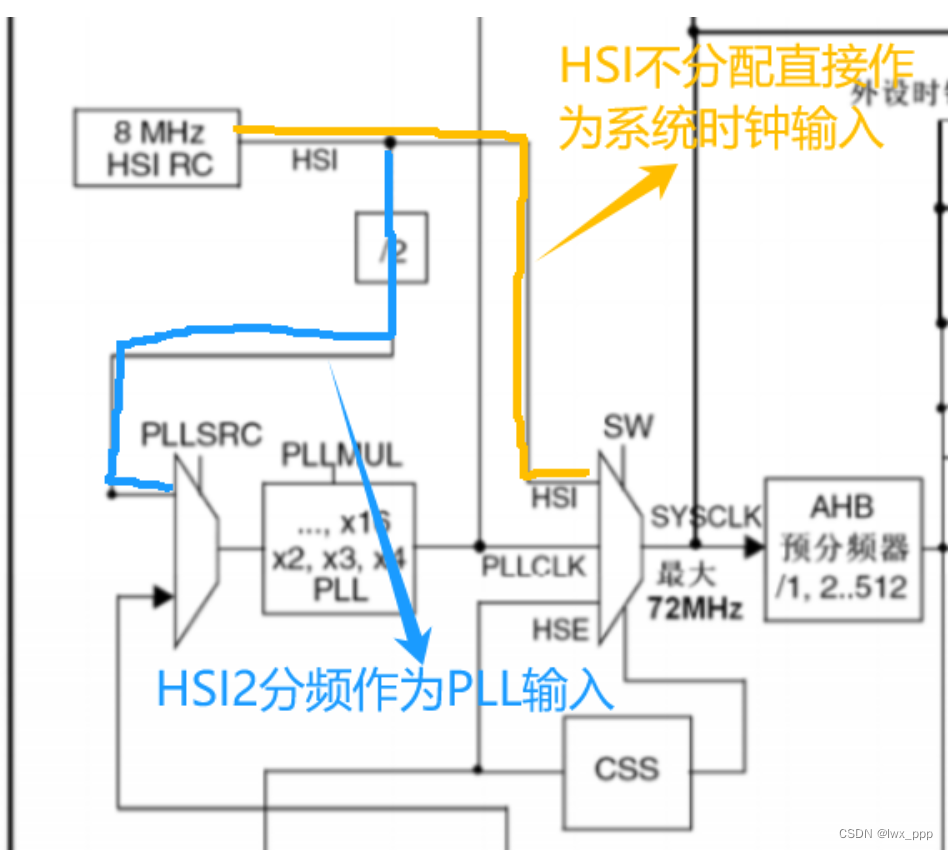

HSI時鐘: 高速的內部時鐘

來源: 芯片內部,大小為8M,當HSE故障時,系統時鐘會自動切換到HSI,直到HSE啟動成功。

作用: 可直接作為系統時鐘或在2分頻后作為PLL輸入。HSI RC振蕩器能夠在不需要任何外部器件的條件下提供系統時鐘。它的啟動時間比HSE晶體振蕩器短。然而,即使在校準之后它的時鐘頻率精度仍較差。

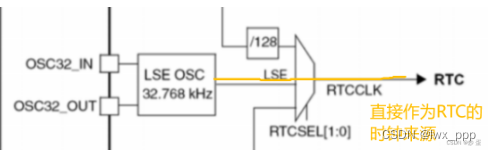

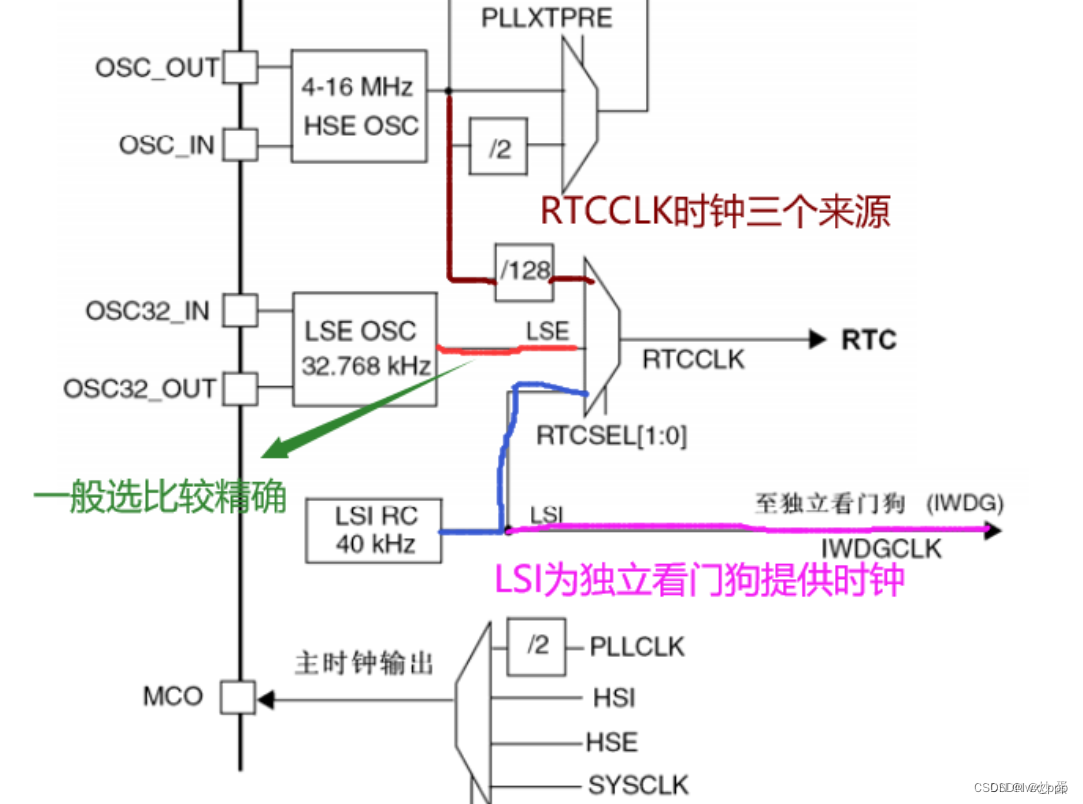

LSE: 低速的外部時鐘

來源:芯片內部,LSE晶體是一個32.768kHz的低速外部晶體或陶瓷諧振器。它為實時時鐘或者其他定時功能提供一個低功耗且精確的時鐘源。?

作用: 直接作為RTC的時鐘來源

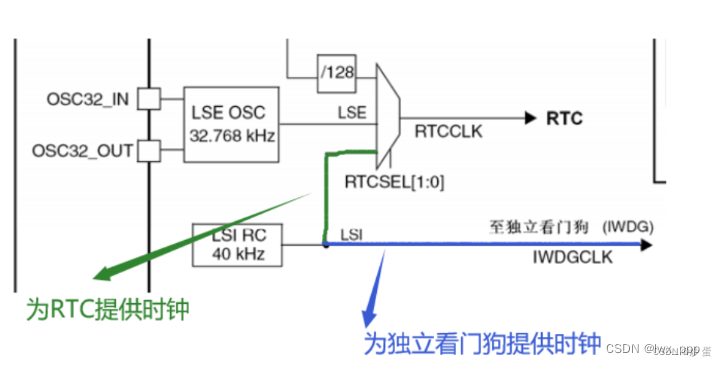

LSI: 低速的內部時鐘

來源: 內部芯片,LSI RC擔當一個低功耗時鐘源的角色,它可以在停機和待機模式下保持運行,LSI時鐘頻率大約40kHz(在30kHz和60kHz之間)。

作用: 為獨立看門狗和自動喚醒單元(RTC)提供時鐘。

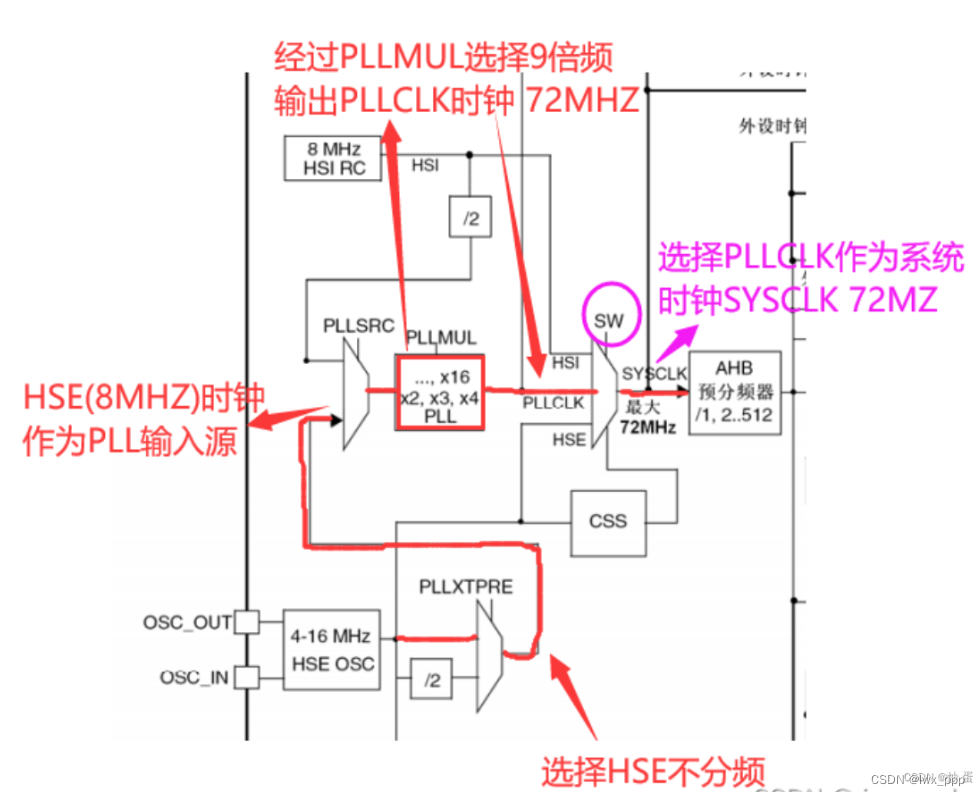

2.2 鎖相環時鐘PLLCLK

鎖相環時鐘:PLLCLK

來源: 選擇HIS振蕩器除2或HSE振蕩器為PLL的輸入時鐘,和選擇倍頻因子,必須在其被激活前完成。一旦PLL被激活,這些參數就不能被改動。

作用: 內部PLL可以用來倍頻HSI的輸出時鐘或HSE晶體輸出時鐘(倍頻數2~16倍),而經過倍頻變成PLLCLK可以作為系統時鐘源

注意: PLL時鐘源頭使用HIS/2的時候,PLLMUL最大只能 是16,這個時候PLLCLK最大只能是64M,小于ST官方推 薦的最大時鐘72M。如果需要在應用中使用USB接口,PLL必須被設置為輸出48或72MHZ時鐘,用于提供48MHz的USBCLK時鐘。

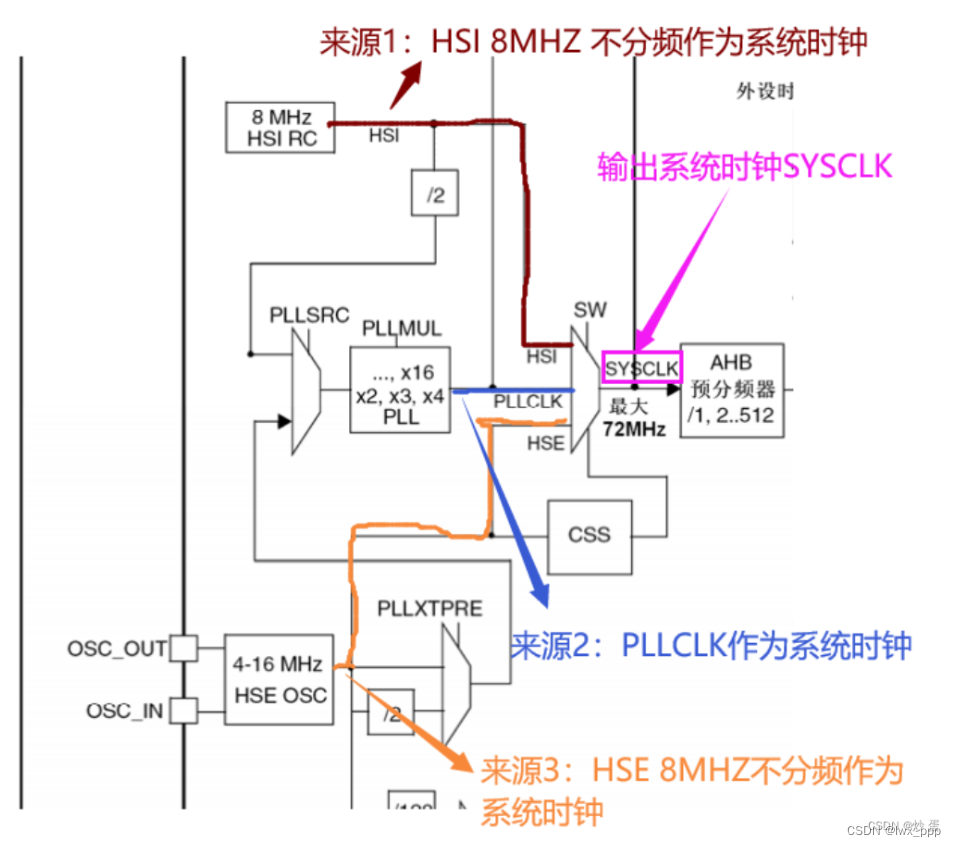

2.3 系統時鐘

系統時鐘:SYSCLK系統時鐘是時鐘樹的最終輸出,它是整個微控制器系統的主時鐘。

來源:HSI,HSE,PLLCLK

注意:F103通常的配置是SYSCLK = PLLCLK=72M(最大的時鐘頻率, STM32官方推薦)

通常系統時鐘配置的輸出流程:

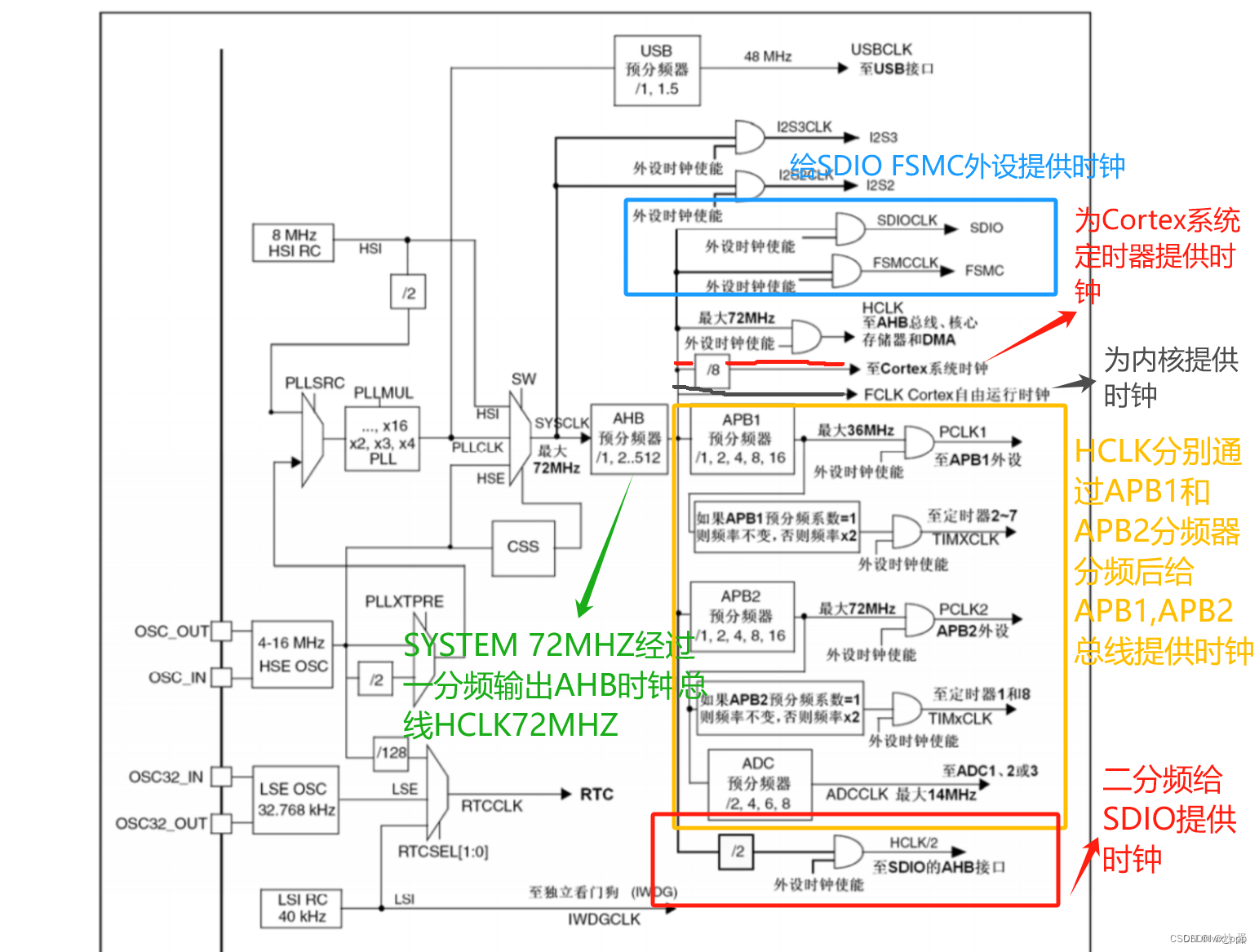

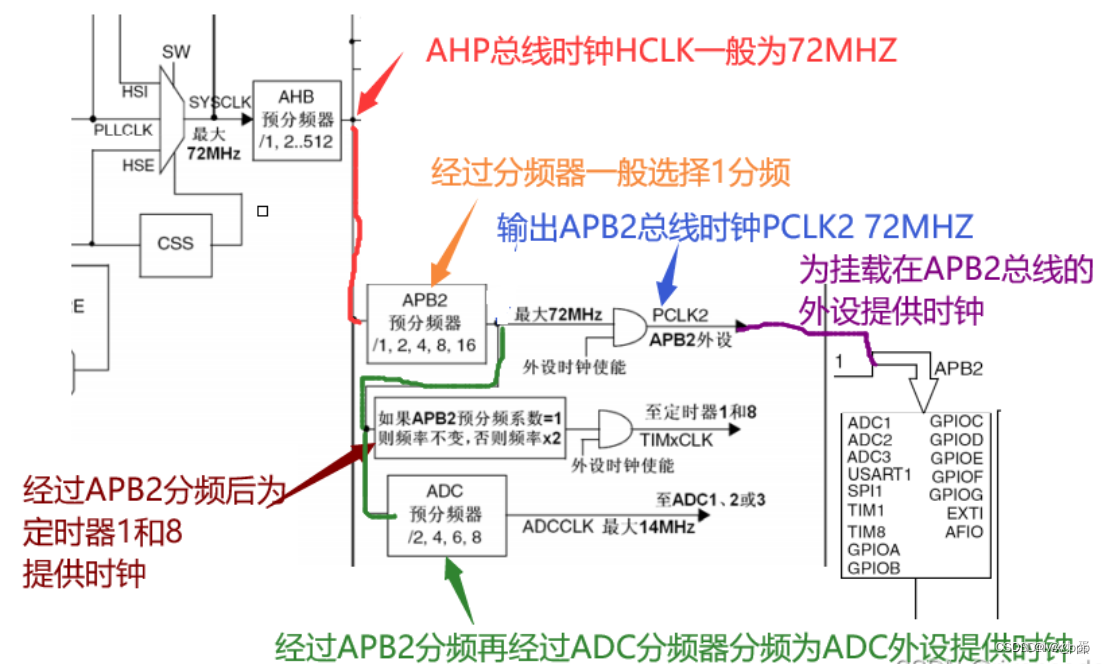

2.4 HCLK時鐘

HCLK: AHB高速總線時鐘,速度最高為72MHZ

來源:?系統時鐘分頻得到,一般設置HCLK=SYSCLK=72M

作用: 為AHB總線的外設提供時鐘、為Cortex系統定時器提供時鐘(SysTick)、為內核提供時鐘(FCLK)。

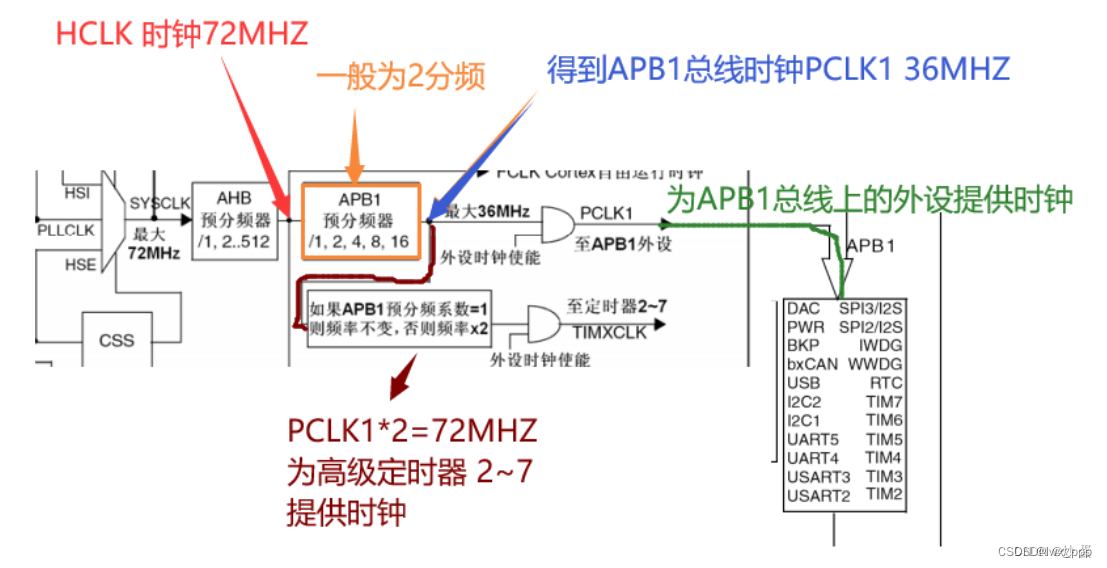

2.5 PCLK1時鐘

PCLK1: APB1低速總線時鐘,最高為36MHZ。

來源: HCLK分頻得到,一般配置PCLK1 = HCLK/2 = 36MHZ。

作用:?為APB1總線的外設提供時鐘。1或2倍頻之后則為APB1總線的定時器2~7提供時鐘,最大為72M。

2.6 PCLK2時鐘

PCLK2: APB2高速總線時鐘,最高為72MHZ

來源: HCLK分頻得到,一般配置PCLK1=HCLK=72M

作用: 為APB2總線的外設提供時鐘。為APB2總線的定時器1和8提供時鐘,最大為72M。APB2分頻器還有一路輸出供ADC分頻器使用,分頻后送給ADC模塊使用。

2.7 RTC時鐘

RTC:實時時鐘。

來源:HSE分頻得到, LSE、 LSI

作用:它擁有一組連續計數的計數器,可提供時鐘日歷的功能。修改計數器的值可以重新設置系統當前的時間和日期。實質上它是一個掉電后還可以繼續運行的定時器。

帶來的安全風險?)

-- 矩陣)

和反向迭代器適配器的實現)