Repeaters

-

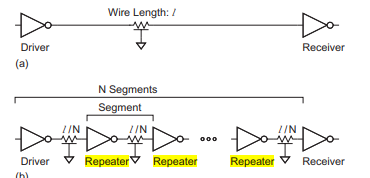

RC延遲與導線長度的關系:

- 導線的電阻(R)和電容(C)都會隨著導線長度(l)的增加而增大。

- RC延遲是電阻和電容共同作用導致的信號延遲。由于RC延遲與R和C的乘積有關,因此它會隨著導線長度的平方(l2)而增加。

-

使用中繼器(Repeater)降低延遲:

- 為了減少這種延遲,可以將長導線分成N段,并在每段之間插入一個叫做“中繼器”的裝置(通常是一個反相器或緩沖器)。

- 中繼器的作用是主動驅動信號,使信號能夠更快地通過下一段導線。

- 每段導線的RC延遲大致與 (l/N)2 成正比。因為總共有N段,所以總的延遲大約是 l2 / N。

-

中繼器數量與延遲關系的優化:

- 如果中繼器的數量(即分段數N)與導線長度l成正比,那么總的延遲就不再是隨l2增長,而是只與l成正比。

- 這樣就可以顯著改善長導線帶來的信號延遲問題。

如何優化中繼器(repeater)之間的距離和尺寸,以達到最小的信號傳輸延遲。

背景設定:

- 使用反相器(inverter)作為中繼器可以提高信號驅動能力,從而減少導線上的RC延遲。

- 每個中繼器本身也會引入一定的延遲。

- 如果中繼器之間間隔太遠 → 延遲主要由長導線的RC效應決定;

- 如果中繼器之間間隔太近 → 延遲主要由大量中繼器本身的延遲累積造成;

- 所以需要在兩者之間找到一個平衡點,使總延遲最小。

參數定義:

-

一個“單位大小”的反相器具有:

- 電阻 R

- 柵極電容 C

- 擴散電容 Cp_inv(即輸出端口的寄生電容)

-

導線每單位長度的參數為:

- 電阻 Rw

- 電容 Cw

-

插入的中繼器是“W倍單位大小”的反相器。也就是說,中繼器的尺寸可以放大 W 倍來增強驅動能力。

分析思路:

-

延遲來源分解:

- 中繼器輸入到輸出的延遲 = 驅動器(前一級)通過導線給中繼器輸入端的電容充電的時間。

- 中繼器輸出驅動下一段導線時,也要對導線電容以及下一級中繼器的輸入電容進行充放電。

-

中繼器尺寸的影響:

- 如果中繼器尺寸變大(W增大),它的內部電阻會減小,驅動能力增強,延遲降低;

- 但同時它的輸入電容(C × W)也會增加,導致前一級驅動它時產生更多延遲;

- 因此,中繼器尺寸也需要優化,不能太大也不能太小。

-

目標:

- 找到最優的中繼器插入間隔(即每段導線的長度);

- 找到最優的中繼器尺寸放大倍數 W;

- 使得整個路徑上的信號傳播延遲最小。

總結:

為了最小化長導線引起的信號延遲,可以通過插入適當數量、適當尺寸的中繼器來分段驅動導線。這涉及到兩個關鍵參數的優化:

- 中繼器之間的距離(導線分段長度)

- 中繼器的尺寸放大倍數 W

公式(編號對應CMOS VLSI Design A Circuits and Systems Perspecctive)

| 公式編號 | 公式文本形式 (純文本) | 新變量名稱及解釋 | 公式內容描述 | 影響最大的幾個變量及其關系 |

|---|---|---|---|---|

| (6.26) | t_pd = N * [ R / W * ( (C_w * l / N) + CW(1 + p_inv) ) + Rw * (l/N) * ( (C_w / 2* (l/N)) + C*W ) ] | t _ p d t\_{pd} t_pd: 傳播延遲 (總延遲)。<br> N N N: 重復器(Repeater/Inverter)的數量。<br> R R R: 每個重復器的輸出電阻 (Effective resistance of each repeater)。<br> C _ w C\_w C_w: 單位長度導線電容 (Capacitance per unit length of wire)。<br> C C C: 每個重復器的輸入電容 (Input capacitance of each repeater)。<br> W W W: 重復器的寬度,通常指驅動晶體管的寬度。<br> p _ i n v p\_{inv} p_inv: 反相器延遲因子,通常與扇出(fanout)有關,描述反相器相對于其內部RC常數的延遲倍數。對于FO4(fanout-of-4)反相器,通常 p _ i n v a p p r o x 0.5 p\_{inv} \\approx 0.5 p_invapprox0.5 (對于折疊晶體管)。<br> C _ s w C\_{sw} C_sw: 單位長度導線開關電容 (Switching capacitance per unit length of wire),這可能是導線與襯底或相鄰導線之間的邊緣效應電容。 | 這是重復導線的Elmore延遲模型,表示一個具有 N N N個重復器的互連線的總傳播延遲。它包含兩部分:重復器本身的延遲和驅動導線的延遲。 | N (重復器數量): 復雜關系,存在最佳值,N過小或過大都會增加延遲。<br> R (重復器電阻): 成正比。<br> C_w (單位長度導線電容): 成正比。<br> C (重復器輸入電容): 成正比。<br> W (重復器寬度): 通常W越大R越小C越大,存在一個權衡。<br> R_w (單位長度導線電阻): 存在于R項中,與延遲呈正比。 |

| (6.27) | l / N = sqrt( (2 * R * C * (1 + p_inv)) / (R_w * C_w) ) | l l l: 導線總長度 (Total wire length)。<br> R _ w R\_w R_w: 單位長度導線電阻 (Resistance per unit length of wire)。 | 這個公式表示在實現最小總延遲時,每段導線的最佳長度 ( l / N l/N l/N)。它通過對(6.26)式關于 N N N和 W W W求導并優化得到,平衡了重復器本身的延遲和驅動導線的延遲。 | R (重復器電阻): 每段長度與R的平方根成正比。<br> C (重復器輸入電容): 每段長度與C的平方根成正比。<br> R_w (單位長度導線電阻): 每段長度與R_w的平方根成反比。<br> C_w (單位長度導線電容): 每段長度與C_w的平方根成反比。 |

| (6.28) | l / N = 0.77* sqrt( FO4 / (R_w *C_w)) | FO4: FO4反相器的延遲,這里假設是 5 R C 5RC 5RC。 | 這是(6.27)的簡化形式,假設FO4反相器延遲為 5 R C 5RC 5RC,并且 p _ i n v = 0.5 p\_{inv} = 0.5 p_inv=0.5(對于折疊晶體管)。這個常數 0.77 0.77 0.77是經過經驗優化或簡化得到的。 | FO4 (FO4反相器延遲): 平方根成正比。<br> R_w (單位長度導線電阻): 每段長度與R_w的平方根成反比。<br> C_w (單位長度導線電容): 每段長度與C_w的平方根成反比。 |

| (6.29) | t_pd / l = (2 + sqrt(2 * (1 + p_inv))) * sqrt(R * C * R_w * C_w) = 1.67 * sqrt(FO4 * R_w * C_w) | 這個公式表示在最佳重復器配置下,每單位長度的重復導線的最小延遲。它表明了在理想情況下,延遲與導線長度的平方根成正比(這是著名的Elmore延遲的平方根定律)。 | R (重復器電阻): 單位長度延遲與R的平方根成正比。<br> C (重復器輸入電容): 單位長度延遲與C的平方根成正比。<br> R_w (單位長度導線電阻): 單位長度延遲與R_w的平方根成正比。<br> C_w (單位長度導線電容): 單位長度延遲與C_w的平方根成正比。<br> FO4 (FO4反相器延遲): 單位長度延遲與FO4的平方根成正比。 | |

| (6.30) | W = sqrt( (R * C_w) / (R_w * C) ) | 為了實現上述最小延遲,該公式給出了反相器應使用的nMOS晶體管的寬度。這個寬度是優化重復器性能的關鍵參數之一。 | R (重復器電阻): 重復器寬度與R的平方根成正比。<br> C (重復器輸入電容): 重復器寬度與C的平方根成反比。<br> R_w (單位長度導線電阻): 重復器寬度與R_w的平方根成反比。<br> C_w (單位長度導線電容): 重復器寬度與C_w的平方根成正比。 | |

| (6.31) | E / l = C_w + NWC*(1 + p_inv) = C_w * ( 1 + sqrt( (1 + p_inv) / 2 ) ) * V_DD^2 = 1.87 * C_w * V_DD^2 | E E E: 傳輸一個比特所需的能量 (Energy to send a bit).<br> V _ D D V\_{DD} V_DD: 電源電壓 (Supply voltage). | 這個公式表示每單位長度傳輸一個比特所需的能量。在優化延遲的重復器配置下,能量主要由導線電容和重復器電容的充放電決定。最終簡化式說明,對于優化后的重復導線,能量消耗主要與單位長度導線電容和電源電壓的平方成正比。 | C_w (單位長度導線電容): 成正比。<br> V_DD (電源電壓): 成二次方正比。 |

📌 關鍵術語中英對照表(便于快速查閱)

| 中文術語 | 英文術語 |

|---|---|

| 中繼器 | Repeater |

| 反相器 | Inverter |

| 擴散電容 | Diffusion Capacitance |

| 單位長度線電容 | Unit-length wire capacitance |

| 折疊晶體管 | Folded transistor |

| 非反相中繼器 | Noninverting repeater |

| 延遲 | Delay |

| 能量-延遲乘積 | Energy-Delay Product (EDP) |

| 導線 | Wire |

| 段 | Segment |

| 尺寸倍數 | Size multiple |

| 三態總線 | Tristate bus |

| 分布式總線 | Distributed bus |

| 點對點通信 | Point-to-point communication |

| 方向性 | Directionality |

導線延遲與能耗優化之間的權衡關系,以及中繼器設計對電路性能的影響。

1. 延遲與能量的折中(EDP 最小點)

- 在最優驅動尺寸和中繼器間距附近,延遲隨距離和驅動尺寸的變化曲線比較平坦。這意味著:

- 如果允許延遲略微增加,可以顯著降低能量消耗。

- 當達到能量延遲積(EDP, Energy-Delay Product)最小點時:

- 每段導線長度變為原來的 1.7 倍。

- 驅動器寬度減小到原來的 0.6 倍。

- 延遲增加了 14%,但中繼器只使總能量增加 30%(相比沒有中繼器的情況)。

- 對于 Example 6.10 中的參數:

- 最優 EDP 點出現在:

- 中繼器間距約為 0.8 mm

- 驅動器寬度為 11 Rm(即 110x 單位寬度)

- 能量降低至 0.26 pJ/mm

- 延遲為 47 ps/mm

- 最優 EDP 點出現在:

- 缺點是:由于導線段更長,系統更容易受到噪聲干擾。

2. 中繼器類型對設計的影響

- 使用反相中繼器inverting repeaters會帶來一些設計復雜性:

- 必須確保每根線上有偶數個中繼器,以保證信號極性不變;

- 或者接收端邏輯要能處理反轉后的輸入信號。

- 為了避免這個問題,有些設計師使用緩沖器結構(兩個反相器串聯)代替單個反相器:

- 這樣不會改變信號極性;

- 但會引入額外的延遲。

- 緩沖器中的第一個反相器可以做得較小(

W1),因為它對前級導線的負載更輕; - 第二個反相器可以做得更大(

W2 = k × W1),以更好地驅動下一段導線;- 當

p_inv = 0.5時,最佳比例因子k = 2.25。

- 當

- 使用緩沖器后,中繼器之間的最優間距也會相應增大(具體公式見練習題 6.6)。

總結

該段內容強調了在實際高速數字電路設計中,如何在延遲、能量、噪聲和設計復雜度之間進行權衡:

- 在延遲略有上升的情況下,可以顯著節省能量;

- 使用緩沖器結構雖然解決了信號極性問題,但會增加延遲;

- 中繼器的設計需要綜合考慮驅動強度、段長、噪聲容忍度和功耗等多方面因素。

公式

由于圖片中沒有明確給出所有變量的定義,我將根據集成電路設計中的常見慣例進行推斷和解釋。

| 公式編號 | 公式文本形式 (純文本) | 新變量名稱及解釋 | 公式內容描述 | 影響最大的幾個變量及其關系 |

|---|---|---|---|---|

| (6.33) | l / N = sqrt( (2 * R * C * (k + (1/k) + 2 * p_inv)) / (R_w * C_w) ) = 1.22 * FO4 / sqrt(R_w * C_w) | l l l: 導線總長度 (Total wire length)。<br> N N N: 重復器(Repeater/Inverter)的數量。<br> R R R: 每個重復器的輸出電阻 (Effective resistance of each repeater)。<br> C C C: 每個重復器的輸入電容 (Input capacitance of each repeater)。<br> k k k: 重復器(緩沖器)的扇出比(或級聯比),表示相鄰兩級重復器之間的尺寸比例或驅動能力比例。通常用于優化多級緩沖器的延遲。<br> p _ i n v p\_{inv} p_inv: 反相器延遲因子,通常與扇出(fanout)有關,描述反相器相對于其內部RC常數的延遲倍數。<br> R _ w R\_w R_w: 單位長度導線電阻 (Resistance per unit length of wire)。<br> C _ w C\_w C_w: 單位長度導線電容 (Capacitance per unit length of wire)。<br> FO4: FO4反相器的延遲,這里假設是 5 R C 5RC 5RC。 | 這個公式表示在優化延遲時,每段導線的最佳長度 ( l / N l/N l/N)。它考慮了重復器(緩沖器)的級聯比 k k k,以進一步優化性能。等式右側是簡化后的經驗公式,使用FO4延遲來表示。 | R (重復器電阻): 每段長度與R的平方根成正比。<br> C (重復器輸入電容): 每段長度與C的平方根成正比。<br> k (級聯比): 影響復雜,存在最佳k值。<br> R_w (單位長度導線電阻): 每段長度與R_w的平方根成反比。<br> C_w (單位長度導線電容): 每段長度與C_w的平方根成反比。<br> FO4 (FO4反相器延遲): 成正比。 |

| (6.34) | t_pd / l = 1.81 * sqrt(FO4 * R_w * C_w) | t _ p d t\_{pd} t_pd: 傳播延遲 (總延遲)。 | 這個公式表示在最佳重復器(緩沖器)配置下,每單位長度的重復導線的最小延遲。常數 1.81 1.81 1.81是經過優化和簡化后得到的經驗值。 | FO4 (FO4反相器延遲): 單位長度延遲與FO4的平方根成正比。<br> R_w (單位長度導線電阻): 單位長度延遲與R_w的平方根成正比。<br> C_w (單位長度導線電容): 單位長度延遲與C_w的平方根成正比。 |

| (6.35) | W_1 = W / sqrt(k) , W_2 = W * sqrt(k) | W _ 1 W\_1 W_1: 第一級(或輸入級)晶體管的寬度。<br> W _ 2 W\_2 W_2: 第二級(或輸出級)晶體管的寬度。<br> W W W: 基礎晶體管寬度,可能是指某個參考尺寸或未優化的寬度。<br> k k k: 重復器(緩沖器)的扇出比(或級聯比)。 | 這些公式給出了在優化延遲時,不同級重復器(或緩沖器)中晶體管的寬度。通常,多級緩沖器會按照一定的比例(如 k k k)進行尺寸遞增,以有效地驅動大負載。 | k (級聯比): 影響晶體管寬度,W1與k的平方根成反比,W2與k的平方根成正比。<br> W (基礎寬度): 成正比。 |

| (6.36) | E / l = 2.2 * C_w * V_DD^2 | E E E: 傳輸一個比特所需的能量 (Energy to send a bit).<br> V _ D D V\_{DD} V_DD: 電源電壓 (Supply voltage). | 這個公式表示每單位長度傳輸一個比特所需的能量。常數 2.2 2.2 2.2是經過優化和簡化后得到的經驗值。它表明,對于優化后的重復導線,能量消耗主要由單位長度導線電容和電源電壓的平方決定。 | C_w (單位長度導線電容): 成正比。<br> V_DD (電源電壓): 成二次方正比。 |

非反相中繼器(noninverting repeaters)與反相中繼器(inverting repeaters)在性能、面積和設計復雜性方面的差異,導線方向性對通信結構的影響。

1. 非反相中繼器的延遲代價

- 使用非反相中繼器(即緩沖器,由兩個反相器組成)時,每單位長度的導線延遲僅比使用單個反相中繼器增加約8%。

- 雖然引入了額外的延遲,但這種代價相對較小。

2. 中繼器數量減少帶來的好處

- 因為非反相中繼器允許更長的段長(見前文關于 EDP 最小點的分析),所以所需的中繼器數量大約只有原來的三分之二。

- 這帶來了以下優勢:

- 簡化布局規劃(floorplanning):因為需要放置的中繼器更少,所以在芯片上尋找合適位置變得更簡單;

- 布線資源壓力減小:減少了中繼器占用的空間和布線干擾。

3. 面積與功耗略有上升

- 雖然中繼器數量減少,但由于每個非反相中繼器包含兩個反相器,因此:

- 總面積略增;

- 總功耗也略有上升;

- 但這些增加通常是可以接受的,尤其是在考慮了布局便利性和信號完整性之后。

4. 延遲對中繼器間距不敏感

- 整體延遲對中繼器之間的距離變化并不敏感,也就是說:

- 即使稍微增加中繼器間距,整體延遲不會顯著上升;

- 因此,為了便于布局,可以合理地增加段長,從而減少中繼器數量,而不必擔心嚴重的性能損失。

5. 中繼器導致導線具有方向性

- 中繼器本質上是單向器件,它們只能在一個方向上傳播信號;

- 因此,使用中繼器的導線就變成了有方向性的導線;

- 這帶來了一些限制:

? 對雙向總線和三態總線的影響:

- 雙向總線(bidirectional busses) 和 分布式三態總線(distributed tristate busses):

- 無法使用簡單的中繼器;

- 因為中繼器不能處理反向傳播的信號;

- 所以這些類型的總線速度較慢;

- ? 相對而言,點對點、單向通信結構(point-to-point unidirectional communication)更適合使用中繼器;

- 可以充分利用中繼器帶來的延遲優化;

- 更適合現代高性能數字系統的設計趨勢(如高速串行鏈路、片上網絡等)。

總結

這段話的核心思想是:

在實際電路設計中,使用非反相中繼器雖然會略微增加延遲和功耗,但能顯著簡化布局、減少中繼器數量,同時避免信號極性反轉的問題。由于整體延遲對中繼器間距不敏感,適當增加段長是一個合理的選擇。然而,中繼器的使用也意味著導線變得有方向性,這使得傳統的雙向或三態總線不再適用,從而推動了現代系統向點對點、單向通信架構的發展。

)

版本發布情況)

)

)

)