摘要由于?SiC MOSFET?在高速開關電源中的廣泛應用,導致嚴重的電磁干擾(EMI)問題,因此?EMI?濾波器的設計成為研究熱點。為了滿足電磁兼容(EMC)標準,無源?EMI?濾波器可以有效地降低?DC-DC?變換器產生的電磁干擾,但是無源磁性器件的體積較大,不利于提高?DC-DC變換器的功率密度。該文分析?DC-DC?變換器的電磁干擾源和噪聲源阻抗特性,建立無源和有源EMI?濾波器的理論模型,提出寬頻混合?EMI?濾波器的設計方法。最后,通過實驗驗證寬頻混合EMI?濾波器對?DC-DC?變換器?EMI?的抑制效果。

引言

寬禁帶半導體器件碳化硅場效應晶體管(Silicon ?Carbide Metal-Oxide-Semiconductor Field-Effect ?Transistor, SiC MOSFET)在導通和關斷時,由于其較高的?du/dt?和?di/dt,會產生嚴重的電磁干擾(Electro-magnetic Interference, EMI)噪聲。隨著?SiC MOSFET的廣泛應用,功率變換器,如?Buck DC-DC?變換器,會產生傳導和輻射?EMI,較高的?EMI?可能導致保護電路的運行故障,以及系統?EMI?超標[1]。為了使待測電力電子設備滿足相應的電磁兼容(?Electro-magnetic Compatibility, EMC)標準,通常需要在主回路中添加?EMI?濾波器來抑制系統的電磁干擾[2-3]。濾波作為解決?EMI?問題的主要措施之一,需要將濾波器放置在對外干擾嚴重或者非常敏感的電子設備的輸入輸出端,使?EMI?被衰減,從而提高系統的EMC?性能[4]。EMI?濾波器主要有無源?EMI?濾波器(Passive EMI Filter, PEF)和有源?EMI?濾波器(ActiveEMI Filter, AEF)[5-8]兩種。PEF?主要使用電感和電容來衰減?EMI,而?AEF?主要使用晶體管和運算放大器(Operational Amplifier, OPAMP)將補償電壓或電流注入電路來衰減?EMI[9]。

PEF?已經成熟應用,并且早已實現商業化,由于電力電子系統逐漸向高功率密度發展,因此針對系統功率密度的?EMI?濾波器設計方法是目前的研究熱點。文獻[10-11]在?LCL?型濾波器的基礎上,分別研究了?PWM?整流控制策略和自適應共模?3?次諧波抑制方法。文獻[12]分別針對共模(Common-Mode, CM)和差模(Differential-Mode, DM)無源EMI?濾波器分析并提出了一種對稱型?EMI?濾波器集成設計方案。AEF?是提高系統功率密度的一種非常有效的方法,AEF?可以分為模擬?AEF?和數字?AEF兩種類型。文獻[9]基于電機驅動系統分析了?CM?噪聲傳播路徑,提出在共模接地點嵌入模擬?AEF?抑制CM?噪聲,極大地減小?CM?濾波組件的體積。文獻[13]建立了?DM?模擬?AEF,針對建立的?AC-DC?功率變換器系統模型,計算了?DM?有源濾波器的插入損耗和環路增益。文獻[14]在復數濾波器結構完全復數化的三相鎖相環技術基礎上構建了數字?AEF?從而實現完全消除電網諧波對系統輸出的影響。文獻[15]基于穩定性、頻偏性、幅值增益以及正交特性四個角度為自適應數字?AEF?提供了理論指導依據。

AEF?可以有效地抑制低頻?EMI,而?PEF?可以有效抑制高頻?EMI,為了進一步提高系統的功率密度并結合兩種?EMI?濾波器的優點,混合?EMI?濾波器(Hybrid EMI Filter, HEF)設計成為了當前的研究熱點。文獻[16-18]基于模擬?AEF?拓撲,在不增加PEF?體積的情況下,等效增加了?PEF?的電感電容值,取得了良好的?EMI?抑制效果。文獻[16-17]設計了一種?AEF,通過注入反饋電流來等效增加?CM?電容值,從而抑制系統的共模電磁干擾。文獻[18]提出了一個三繞組的共模電感,基于運算放大器在第三個繞組上搭建了負阻抗網絡來增加共模電感值,因此在不增加共模電感體積的情況下增大了共模電感值,通過等效電感值,不需要增大電感體積,就可以更好地抑制系統的?EMI。

由于高功率密度的需求,在設計階段就要考慮量化?EMI?濾波器電子元件的尺寸和質量,因此需要針對?EMI?濾波器進行規范化設計。文獻[19-22]針對基于插入損耗(Insertion Loss, IL)的?PEF?進行了設計并驗證。PEF?設計需要掌握功率變換器的噪聲源特性,基于線性阻抗穩定網絡(Line Impedance ?Stabilization Network, LISN)的測試平臺對插入損耗進行限定以達到?EMC?標準。為了使?EMI?濾波器達到預期的插入損耗,文獻[23]提出了基于插入無源二端口網絡的噪聲源阻抗提取方法。文獻[24]針對?AC-DC?功率變換器研究了模擬?AEF?的設計過程,對電壓采樣電流補償(?Voltage-Sensing Current-Compensating, VSCC)拓撲模擬有源?EMI?濾波器進行建模和分析,找到了與插入損耗有關的函數關系,最后提出了?VCCS?一般設計準則。文獻[25]針對由于小型體積的?PEF?的低頻段衰減能力較低以及高頻增益限制情況下?AEF?高頻段衰減能力有限的問題,利用電機驅動系統設計了一種基于?LCL-LC PEF?和模擬?AEF?集成的混合?EMI?濾波器,改進了混合?EMI濾波器的設計方法。文獻[26]采用了一種電流采樣電流補償(Current-Sensing Current-Compensating, ?CSCC)模式模擬?AEF?電路,同時增加高諧振頻率的小型?PEF?以抑制高頻段從而得到了良好的?CM ?EMI?衰減。

在上述的文獻研究中,由于?PEF?的體積限制和模擬?AEF?的高頻環路增益限制,集成無源和有源的EMI?濾波器是抑制?EMI?的可行解決方案,但已有參考文獻中基于系統的混合噪聲進行?EMI?濾波器設計,沒有針對性考慮系統?DM?和?CM?噪聲源特性。本文首先研究了同步?Buck DC-DC?變換器的?DM?和CM?噪聲源特性,然后基于噪聲源阻抗模型提出了一種混合?EMI?濾波器設計方法,以規范化設計寬頻混合有源?EMI?濾波器。

1同步?Buck DC-DC?變換器的電磁干擾分析

首先,分析同步?Buck DC-DC?變換器的噪聲源及其阻抗特性,研究同步?Buck DC-DC?變換器電磁干擾的產生特性;然后,基于同步?Buck DC-DC?變換器的電磁干擾分析,規范化設計相應的?EMI?濾波器或者優化設計現有的?EMI?濾波器。

1.1同步?Buck DC-DC?變換器的噪聲源阻抗分析

由于?SiC MOSFET?在導通和關斷時產生較高的du/dt?和?di/dt,與變換器本身存在的寄生電感和寄生電容相互作用,從而在同步?Buck DC-DC?變換器中產生了嚴重的電磁干擾。通過對同步?Buck DC-DC變換器中噪聲的路徑進行分析和測量,得到同步Buck DC-DC?變換器的噪聲源阻抗,可以分為?CM噪聲源阻抗和?DM?噪聲源阻抗。

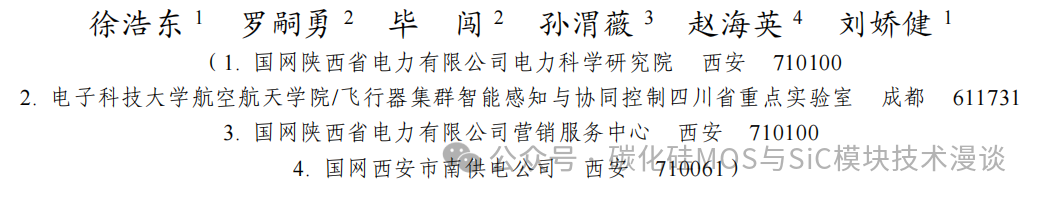

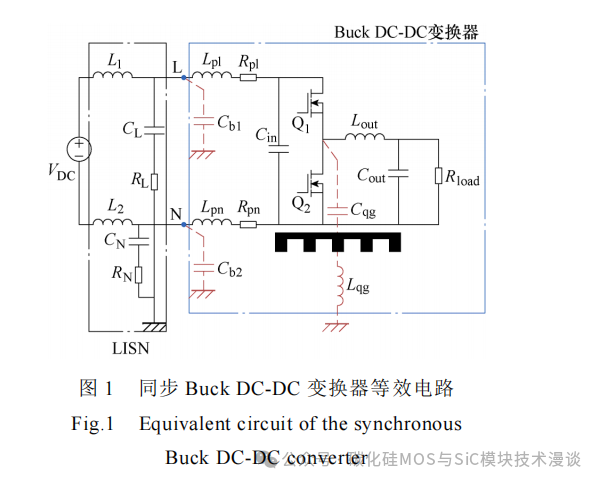

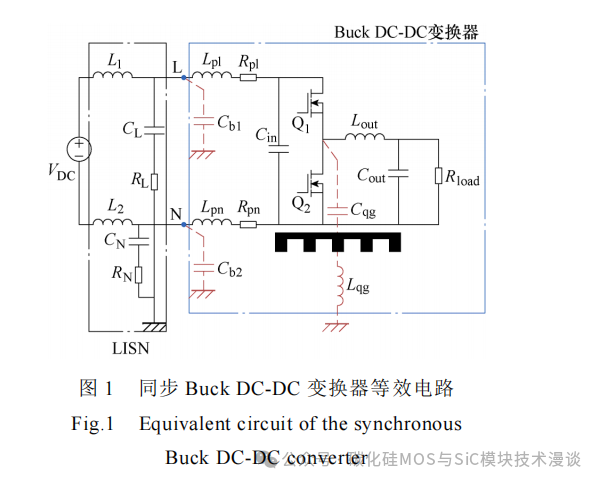

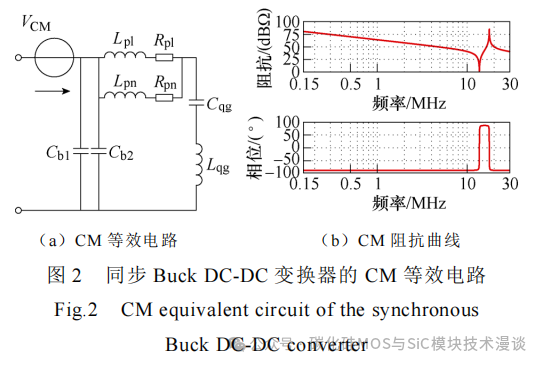

同步?Buck DC-DC?轉換器的等效電路如圖?1?所示。CM?噪聲通過寄生電容?Cqg?和寄生電感?Lqg?從同步?Buck DC-DC?變換器半橋中點轉移到地面,考慮到散熱器和地之間的不完全連接,因此引入寄生電感?Lqg?的影響。同時分別考慮母線中?L?線和?N?線對地的寄生電容?Cb1?和?Cb2?的影響,以及印制電路板(Printed Circuit Board, PCB)布局寄生參數?Lpl、Lpn、Rpl?和?Rpn,可以得到同步?Buck DC-DC?轉換器中?CM阻抗網絡的等效電路和?CM?阻抗特性曲線,如圖?2

所示。VDC?為直流電壓源,L1?和?L2?分別為?L?線和?N線的直流隔離電感,Q1?和?Q2?分別為同步?Buck?控制管和續流管,Lout、Cout、Rout?分別為輸出電感、輸出電容和輸出負載。

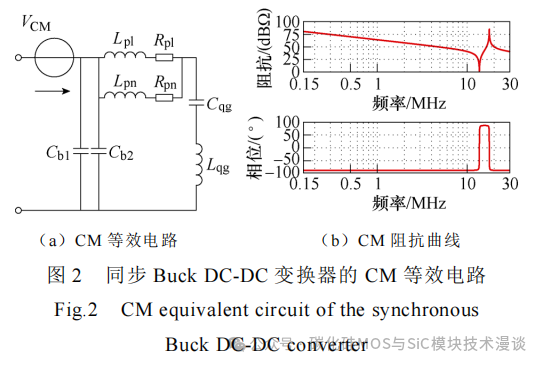

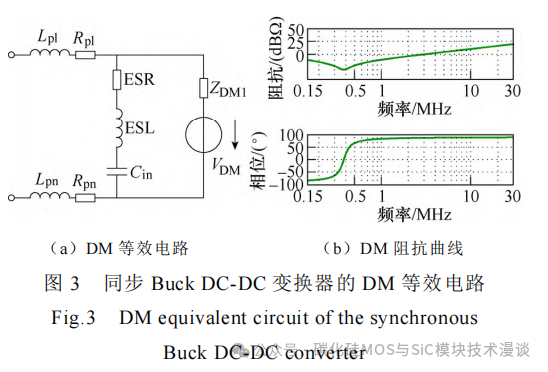

同理,DM?阻抗網絡的等效電路和?DM?阻抗特性曲線如圖?3?所示。由于直流母線支撐電容的低阻抗特性,變換器的差模噪聲源阻抗?ZDM1?可以被忽略,因此直流母線支撐電容?Cin?決定了變換器的?DM阻抗特性,ESR、ESL?分別為直流母線支撐電容?Cin的寄生電阻和寄生電感。

1.2同步?Buck DC-DC變換器的CM/DM噪聲源分析

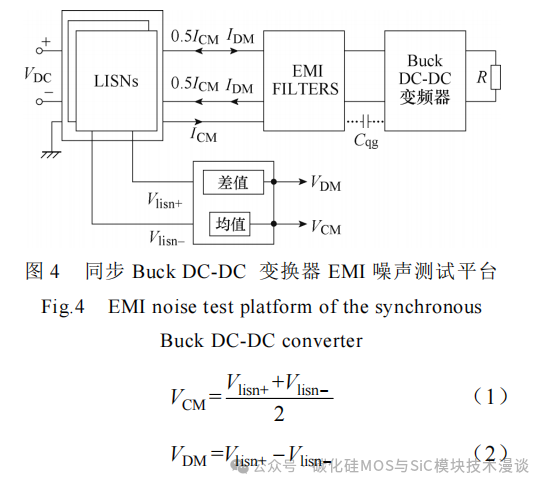

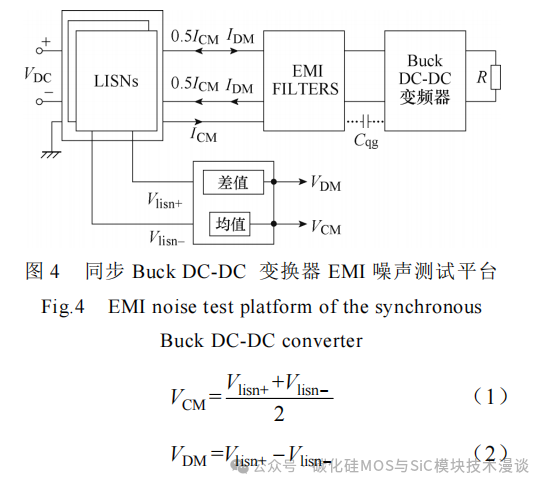

Buck DC-DC?變換器傳導?EMI?的實驗測試平臺如圖?4?所示,由?Buck DC-DC?變換器、EMI?濾波器、線路阻抗穩定網絡(Line Impedance Stabilization ?Network, LISN)、直流電壓源和電阻負載組成。基于?EMI?測試標準國際無線電干擾特別委員會?25(International Special Committee on Radio Interference 25, ?CISPR 25),可以分別測量?DC-DC?變換器的?DM?和CM?電磁干擾噪聲。

Buck DC-DC?變換器的兩個輸入端口分別接?L線和?N?線,測量設備?LISN?被放置在直流電源和?EMI濾波器之前。被測對象的傳導電磁干擾由?LISN?測量,分別可以得到?L?線和?N?線上對地的電壓?Vlisn+和?Vlisn-,然后經過差值和均值運算,分別得到變換器的?CM?電壓?VCM?和?DM?電壓?VDM。

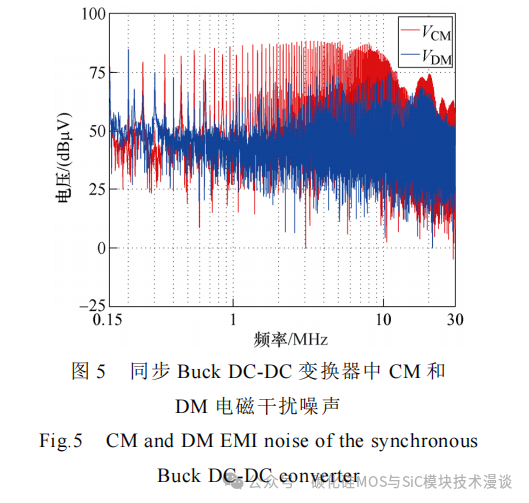

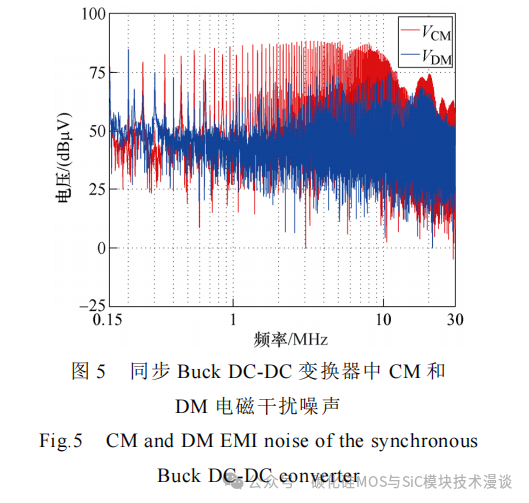

基于實驗測量結果,通過式(1)和式(2)對CM?和?DM?電磁干擾噪聲進行分離提取,得到同步Buck DC-DC?轉換器中?CM?和?DM EMI?的頻域波形(150 kHz~30 MHz),如圖?5?所示。同步?Buck DC-DC?轉換器的原始電磁干擾噪聲,在?150~200 kHz頻段?DM?噪聲會對?EMI?濾波器的設計產生重要影響。為了有效地設計混合?EMI?濾波器,需要考慮低頻段?DM?噪聲的抑制,在?1~10 MHz?頻段?CM?噪聲幅值高于?DM?噪聲幅值,可以考慮通過有源濾波器進行抑制,在高頻段?10~30 MHz,考慮設計合理的無源濾波器參數進行電磁干擾的抑制。

2混合?EMI?濾波器設計

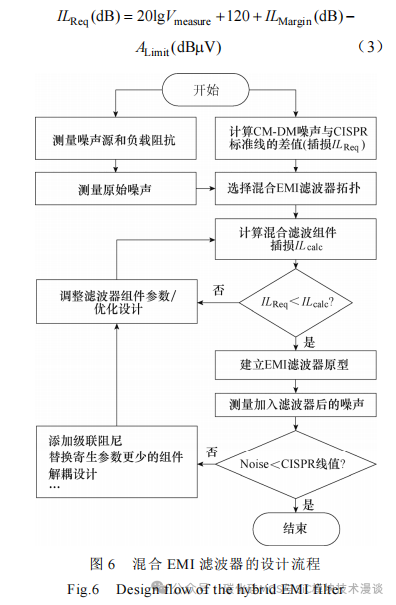

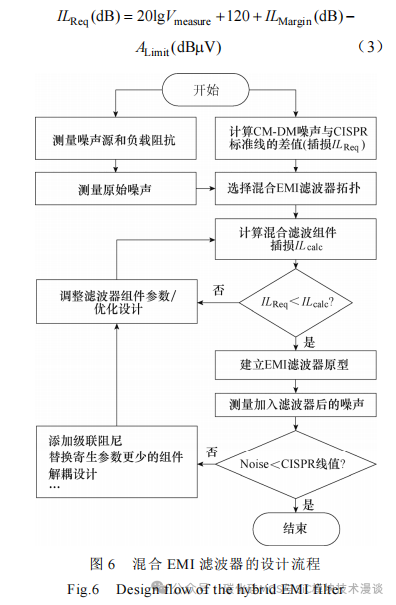

為了設計一個適合開關電源的混合?EMI?濾波器,基于文獻[1-2]中?EMI?濾波器設計過程,本文提出了一個系統的?EMI?設計流程,所提出的混合?EMI濾波器設計流程如圖?6?所示。EMI?濾波器的最重要的特性是衰減電磁干擾源的發射能力,其衰減率定義為插入損耗(Insertion Loss, IL)。為了讓?EMI?濾波器獲得最大插入損耗,在計算濾波器?IL?時需要考慮濾波器輸入輸出端的阻抗參數,在選擇?EMI?濾波器的拓撲結構時需考慮噪聲源和負載阻抗,包括LISN?的?CM-DM?回路阻抗。在確定所需的插入損耗ILReq?后,可以得到?EMI?濾波器組件的參數值。因此,必須利用?LISN?對同步?Buck DC-DC?變換器的原始噪聲進行測量,即沒有加入?EMI?濾波器情況下的CM?和?DM?電磁干擾噪聲測量。根據?CISPR 25?給定的峰值標準線,通過從測量的噪聲?Vmeasure?中減去指定的極限?ALimit?可以計算出所需的插入損耗?ILReq,并適當增加安全裕度值?ILMargin,有

通過計算?EMI?濾波器參數,使加入?EMI?濾波器后同步?Buck DC-DC?變換器符合?EMC?標準要求。為了確定?EMI?濾波器組件的參數值,需要將?ILReq與所計算的插入損耗?ILcalc?進行比較,在符合?EMC標準的要求情況下(包括?CM?和?DM?電磁干擾),計算?EMI?濾波器組件參數,使?ILReq?和?ILcalc?的二次方均值在整個頻率范圍內最小。同時,整個過程的必要條件為?ILcalc≥ILReq。

設計同步?Buck DC-DC?變換器對應的?EMI?濾波器之前,必須計算出各個濾波器組件的實際參數值,實際參數值可以用矢量/阻抗網絡分析儀進行測量,然后給定方程再次計算插入損耗?ILcalc。如果?CM?和DM?的?ILcalc?仍然大于?ILReq,則可以從選定的組件參數設計?EMI?濾波器。若不滿足?ILcalc≥ILReq,則需要調整所選組件參數值,重新計算?ILcalc?是否滿足條件。在滿足條件后,搭建混合?EMI?濾波器原型,插入?LISN?和同步?Buck DC-DC?變換器之間,通過測量插入?EMI?濾波器前后的?EMI?噪聲來評估?EMI?濾波器的抑制效果。由于所選定的?EMI?濾波器組件存在高頻寄生參數,往往并不具有理想的特性,比如組件內部元器件的高頻寄生參數和組件間電磁耦合的影響,因此會導致測量的?EMI?噪聲和期望的?EMI噪聲不一樣。當?EMI?噪聲仍然大于?CISPR 25?標準限值時,需要添加級聯阻尼、替換寄生參數更少的組件以及解耦設計(若混合有源濾波器無法滿足設計要求,需要設計解耦電路以隔離?Buck?電路與外部電路之間的噪聲干擾),進而需要對整體布局或者組件進行優化設計,并重新計算?ILcalc?直至滿足所需EMI?抑制要求。

2.1無源?EMI?濾波器設計

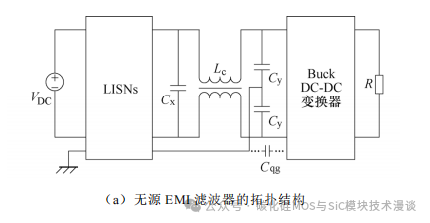

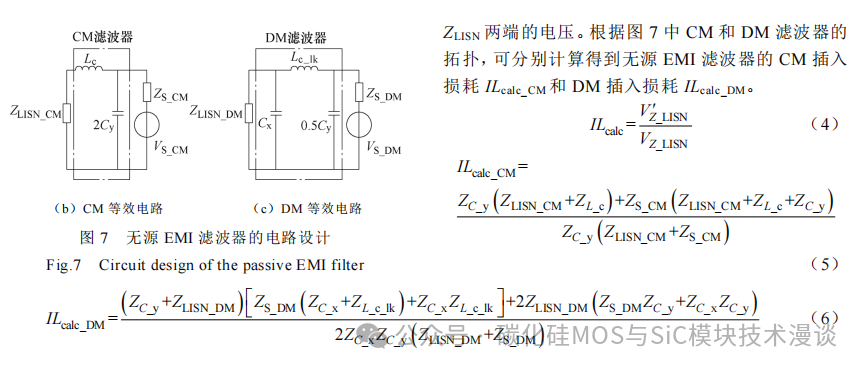

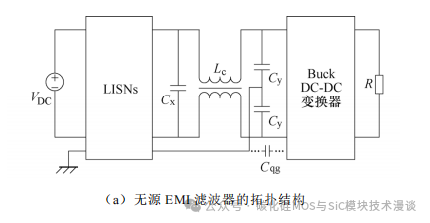

無源?EMI?濾波器采用?CL?結構和?π?型結構來分別衰減?CM?和?DM?信號,如圖?7a?所示。無源?EMI濾波器的?CM?和?DM?等效電路,如圖?7b?和圖?7c?所示。無源?CM?濾波器由兩個并聯的?Y?型電容器?Cy和一個共模扼流圈?Lc?組成(見圖?7b)。同理,無源DM?濾波器由?X?電容器?Cx、共模扼流圈漏感?Lc_lk和兩個?Y?型電容器串聯組成(見圖?7c)。

由式(4)可計算無源?EMI?濾波器插入損耗ILcalc,VZ'_LISN?為未插入濾波器前?ZLISN?兩端的電壓,ZLISN?為?LISN?兩端的阻抗,VZ_LISN?為插入濾波器后

式中,ZLISN_CM、ZLISN_DM?分別為?LISN?的共模阻抗、LISN?的差模阻抗;ZL_c、ZL_c_lk?分別為共模扼流圈Lc?阻抗、共模扼流圈漏感?Lc_lk?阻抗;ZC_y、ZC_x?分別為?Y?型電容器?Cy阻抗、X?型電容器?Cx阻抗;ZS_CM、ZS_DM?分別為噪聲源共模阻抗以及噪聲源差模阻抗。

設定無源?EMI?濾波器各個組件的參數值,通過設計流程得到滿足?EMC?標準的無源?EMI?濾波器,但由于單一的無源?EMI?濾波器通常體積較大,為了提高開關電源的功率密度,本文在基于無源?EMI?濾波器的基礎上,加入模擬有源?EMI?濾波器設計,從而在寬頻范圍內增加系統的?EMI?抑制效果。

2.2模擬有源?EMI?濾波器設計

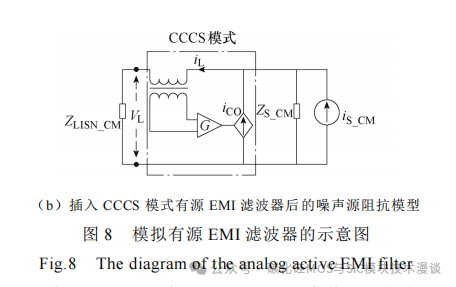

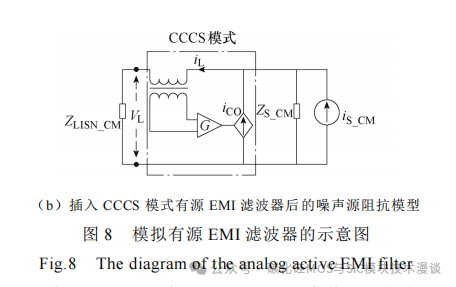

本文采用電流采樣電流補償?CSCC?模式模擬有源濾波器電路(基于式(11)和?Buck DC-DC?變換器中低頻段?ZS_CM?ZLISN_CM,抑制同步?Buck DC-DC變換器中共模回路的共模?EMI?噪聲信號,其等效電路拓撲如圖?8?所示。

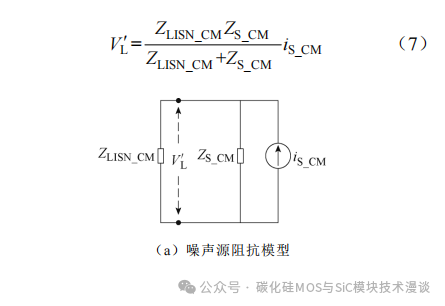

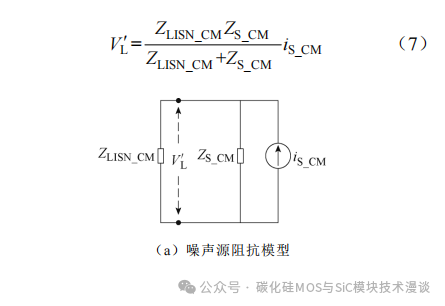

圖?8a?展示了沒有插入模擬有源濾波器的同步Buck DC-DC?變換器、LISN?和直流源的測試電路中共模回路等效拓撲,圖中,iS_CM?為同步?Buck DC-DC變換器中共模噪聲的等效電流源,因此同步?Buck DC-DC?變換器共模回路中?LISN?兩端的電壓可以表示為

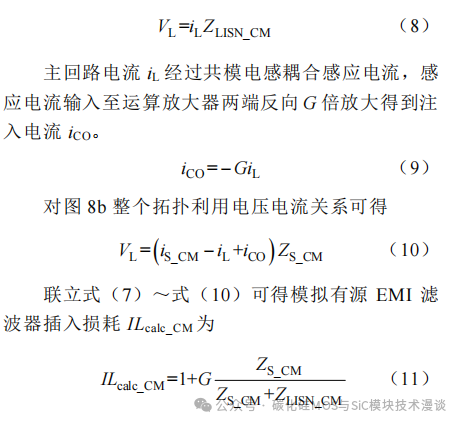

在?LISN?和同步?Buck DC-DC?變換器之間插入CSCC?模式模擬有源濾波器電路后,其共模回路等效拓撲,如圖?8b?所示。共模回路中?LISN?兩端的電壓可以表示為

模擬有源?EMI?濾波器與無源?EMI?濾波器類似,插入損耗與測試平臺?LISN?阻抗和噪聲源阻抗有關。當?Z Z?S_CM LISN_CM???時,模擬有源?EMI?濾波器插入損耗?ILcalc?滿足最大插入損耗的條件,且?ZLISN_CM?≈25?Ω,約為?28 dBΩ,由圖?2?可知,在中低頻情況下(?ZS_CM> ≈?250 48 dB?Ω Ω?)容易滿足?ZS_CM??ZLISN_CM?。

2.3混合?EMI?濾波器設計

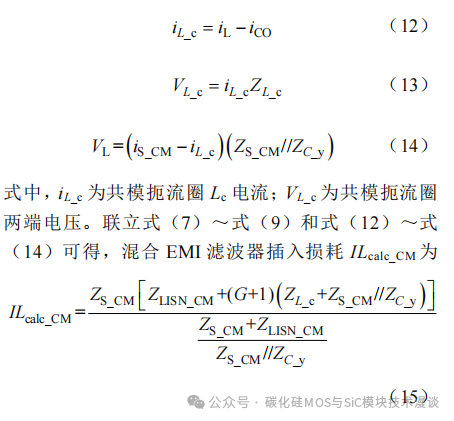

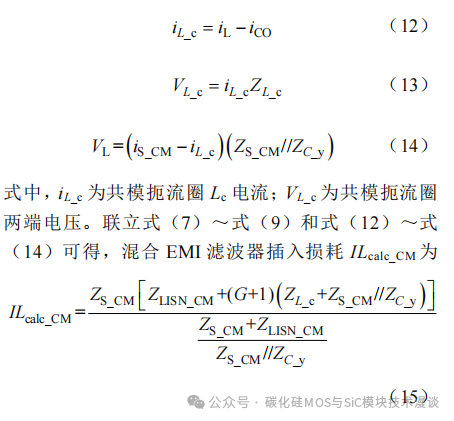

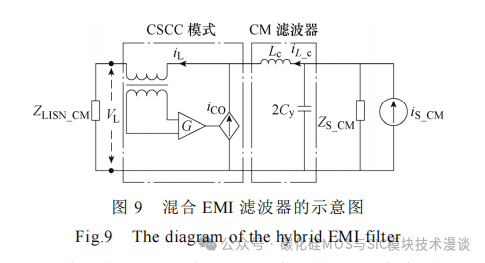

由于同步?Buck DC-DC?變換器的共模阻抗?ZS_CM在高頻階段通常會產生?RLC?諧振點(見圖?2),阻抗不能總是滿足?Z Z?S_CM LISN_CM???,因此為了減少高頻信號對有源?EMI?濾波器的影響,基于模擬有源EMI?濾波器的拓撲結構,將無源?EMI?濾波器插入在模擬有源?EMI?濾波器與噪聲源之間,從而得到混合模擬有源和無源?EMI?濾波器,如圖?9?所示。插入混合?EMI?濾波器后,在電流注入節點可得

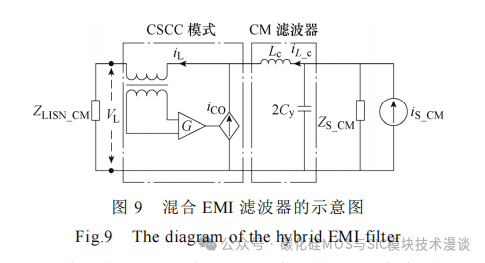

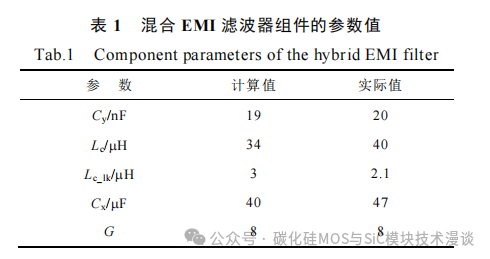

基于式(6)和式(15),將混合?EMI?濾波器插入損耗?ILcalc?代入圖?6?設計流程,完成濾波組件參數計算,最終實現混合?EMI?濾波器的設計,所計算得到的混合?EMI?濾波器組件的參數值見表?1。

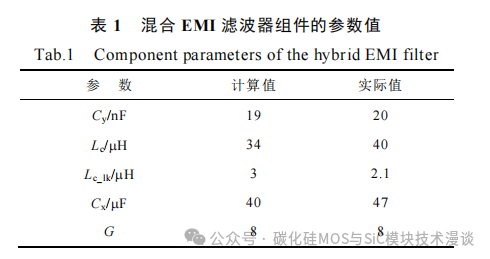

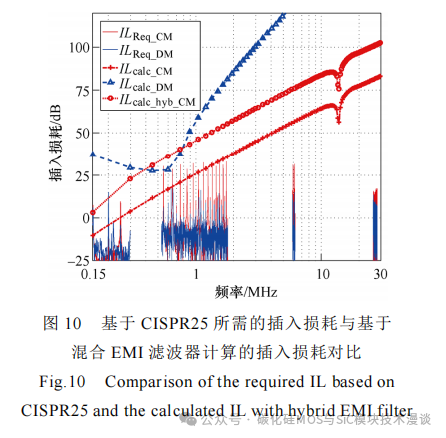

將式(1)、式(2)所得到的結果,以及?CISPR ?25?準峰值代入式(3),可得到?ILReq_CM?和?ILReq_DM所需?CM?和?DM?插入損耗,如圖?10?所示。在無源EMI?濾波器設計部分,通過式(5)、式(6)代入

表?1?參數值和噪聲源阻抗(見圖?2?和圖?3),可計算得到?ILcalc_CM?和?ILcalc_DM,由于參數值選擇以及電路諧振的影響,計算得到的無源?EMI?濾波器的共模插入損耗?ILcalc_DM?并不滿足?ILcalc≥ILReq?的條件,因此本文加入模擬有源?EMI?濾波器部分增加共模插入損耗。在增益為?8?倍的情況下,通過式(15)計算得到混合?EMI?濾波器的寬頻共模插入損耗ILcalc_hyb_CM?均滿足?ILcalc≥ILReq。

3實驗驗證

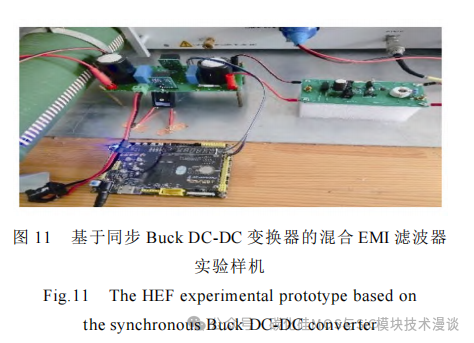

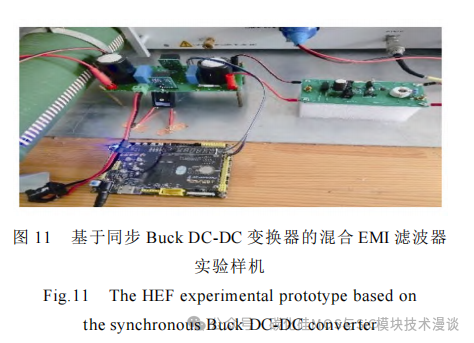

為了驗證第?2?節中理論計算的準確性,在本節中進行基于同步?Buck DC-DC?變換器的濾波器實驗,如圖?11?所示。在實驗中,控制管?Q1?和同步管Q2均采用?CREE?公司的?SiC MOSFET C2M1000170D,由現場可編程邏輯門陣列(Field Programmable Gate ?Array, FPGA)產生驅動信號,運算放大器為德州儀器?LM7171,直流源電壓設置為?400 V,水泥負載為20?Ω。雙管?SiC MOSFET?的開關頻率為交替互補的50 kHz,死區時間為?0.05?μs。

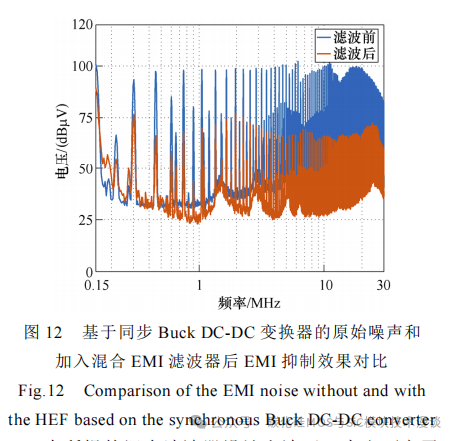

基于表?1?中混合?EMI?濾波器組件的參數,選取對應的元器件,搭建實驗平臺,分別通過?LISN?測

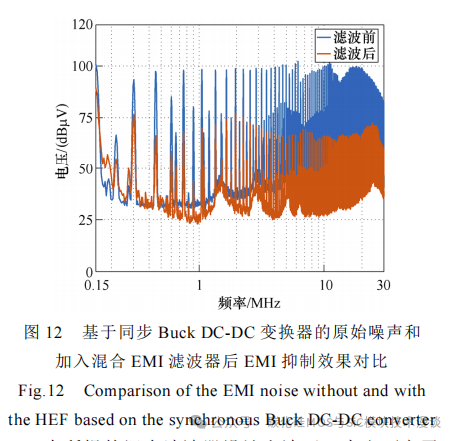

量同步?Buck DC-DC?變換器的原始?EMI?噪聲和加入混合?EMI?濾波器后的?EMI?噪聲效果,對比如圖?12所示。通過實驗結果可知,加入混合?EMI?濾波器后EMI?噪聲抑制效果較好,整個頻段內平均抑制近35 dB。

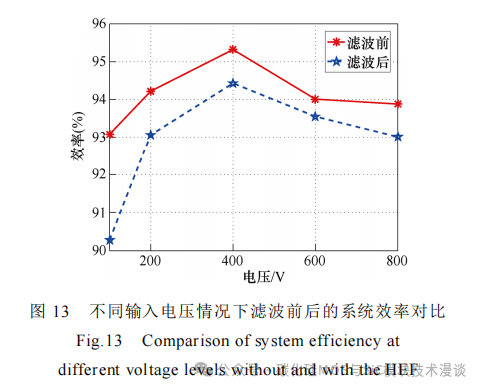

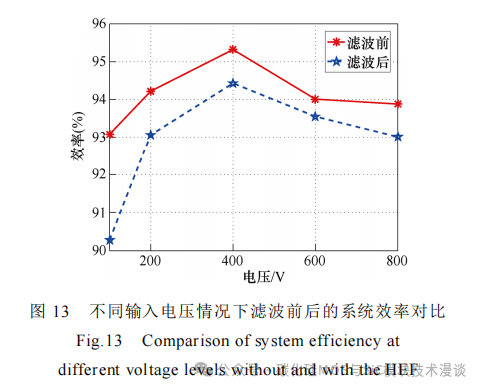

在所提的混合濾波器設計方法下,本文研究了不同輸入電壓情況下濾波前后的系統效率對比,如圖?13?所示。由于增加了混合濾波器部分,會使得系統的效率有所下降,效率平均下降?1.24%。

4結論

本文提出了一種基于同步?Buck DC-DC?變換器的寬頻混合?EMI?濾波器設計方法。為了一個有效的EMI?濾波器,在設計過程中,除了需要了解同步Buck DC-DC?變換器?CM?和?DM?噪聲源的電磁干擾特性,還需要考慮同步?Buck DC-DC?變換器的?CM和?DM?噪聲源阻抗以及負載阻抗。 ? ? ?通過計算?EMI?濾波器的插入損耗,得到?EMI

濾波器的設計參數,但由于較小體積的無源?EMI?濾波器組件不能滿足插入損耗的要求,這將使得設計的?EMI?濾波器不能滿足?EMC?標準的要求。為了增大?EMI?濾波器的插入損耗而不增加無源?EMI?濾波器體積,給出了混合有源和無源?EMI?濾波器的設計流程,以滿足?EMI?濾波器插入損耗的需求和?EMC標準。最后,基于同步?Buck DC-DC?變換器實驗平臺,制作了混合?EMI?濾波器的實驗電路,驗證了寬頻混合?EMI?濾波器的電磁干擾抑制效果。

摘要由于?SiC MOSFET?在高速開關電源中的廣泛應用,導致嚴重的電磁干擾(EMI)問題,因此?EMI?濾波器的設計成為研究熱點。為了滿足電磁兼容(EMC)標準,無源?EMI?濾波器可以有效地降低?DC-DC?變換器產生的電磁干擾,但是無源磁性器件的體積較大,不利于提高?DC-DC變換器的功率密度。該文分析?DC-DC?變換器的電磁干擾源和噪聲源阻抗特性,建立無源和有源EMI?濾波器的理論模型,提出寬頻混合?EMI?濾波器的設計方法。最后,通過實驗驗證寬頻混合EMI?濾波器對?DC-DC?變換器?EMI?的抑制效果。

引言

寬禁帶半導體器件碳化硅場效應晶體管(Silicon ?Carbide Metal-Oxide-Semiconductor Field-Effect ?Transistor, SiC MOSFET)在導通和關斷時,由于其較高的?du/dt?和?di/dt,會產生嚴重的電磁干擾(Electro-magnetic Interference, EMI)噪聲。隨著?SiC MOSFET的廣泛應用,功率變換器,如?Buck DC-DC?變換器,會產生傳導和輻射?EMI,較高的?EMI?可能導致保護電路的運行故障,以及系統?EMI?超標[1]。為了使待測電力電子設備滿足相應的電磁兼容(?Electro-magnetic Compatibility, EMC)標準,通常需要在主回路中添加?EMI?濾波器來抑制系統的電磁干擾[2-3]。濾波作為解決?EMI?問題的主要措施之一,需要將濾波器放置在對外干擾嚴重或者非常敏感的電子設備的輸入輸出端,使?EMI?被衰減,從而提高系統的EMC?性能[4]。EMI?濾波器主要有無源?EMI?濾波器(Passive EMI Filter, PEF)和有源?EMI?濾波器(ActiveEMI Filter, AEF)[5-8]兩種。PEF?主要使用電感和電容來衰減?EMI,而?AEF?主要使用晶體管和運算放大器(Operational Amplifier, OPAMP)將補償電壓或電流注入電路來衰減?EMI[9]。

PEF?已經成熟應用,并且早已實現商業化,由于電力電子系統逐漸向高功率密度發展,因此針對系統功率密度的?EMI?濾波器設計方法是目前的研究熱點。文獻[10-11]在?LCL?型濾波器的基礎上,分別研究了?PWM?整流控制策略和自適應共模?3?次諧波抑制方法。文獻[12]分別針對共模(Common-Mode, CM)和差模(Differential-Mode, DM)無源EMI?濾波器分析并提出了一種對稱型?EMI?濾波器集成設計方案。AEF?是提高系統功率密度的一種非常有效的方法,AEF?可以分為模擬?AEF?和數字?AEF兩種類型。文獻[9]基于電機驅動系統分析了?CM?噪聲傳播路徑,提出在共模接地點嵌入模擬?AEF?抑制CM?噪聲,極大地減小?CM?濾波組件的體積。文獻[13]建立了?DM?模擬?AEF,針對建立的?AC-DC?功率變換器系統模型,計算了?DM?有源濾波器的插入損耗和環路增益。文獻[14]在復數濾波器結構完全復數化的三相鎖相環技術基礎上構建了數字?AEF?從而實現完全消除電網諧波對系統輸出的影響。文獻[15]基于穩定性、頻偏性、幅值增益以及正交特性四個角度為自適應數字?AEF?提供了理論指導依據。

AEF?可以有效地抑制低頻?EMI,而?PEF?可以有效抑制高頻?EMI,為了進一步提高系統的功率密度并結合兩種?EMI?濾波器的優點,混合?EMI?濾波器(Hybrid EMI Filter, HEF)設計成為了當前的研究熱點。文獻[16-18]基于模擬?AEF?拓撲,在不增加PEF?體積的情況下,等效增加了?PEF?的電感電容值,取得了良好的?EMI?抑制效果。文獻[16-17]設計了一種?AEF,通過注入反饋電流來等效增加?CM?電容值,從而抑制系統的共模電磁干擾。文獻[18]提出了一個三繞組的共模電感,基于運算放大器在第三個繞組上搭建了負阻抗網絡來增加共模電感值,因此在不增加共模電感體積的情況下增大了共模電感值,通過等效電感值,不需要增大電感體積,就可以更好地抑制系統的?EMI。

由于高功率密度的需求,在設計階段就要考慮量化?EMI?濾波器電子元件的尺寸和質量,因此需要針對?EMI?濾波器進行規范化設計。文獻[19-22]針對基于插入損耗(Insertion Loss, IL)的?PEF?進行了設計并驗證。PEF?設計需要掌握功率變換器的噪聲源特性,基于線性阻抗穩定網絡(Line Impedance ?Stabilization Network, LISN)的測試平臺對插入損耗進行限定以達到?EMC?標準。為了使?EMI?濾波器達到預期的插入損耗,文獻[23]提出了基于插入無源二端口網絡的噪聲源阻抗提取方法。文獻[24]針對?AC-DC?功率變換器研究了模擬?AEF?的設計過程,對電壓采樣電流補償(?Voltage-Sensing Current-Compensating, VSCC)拓撲模擬有源?EMI?濾波器進行建模和分析,找到了與插入損耗有關的函數關系,最后提出了?VCCS?一般設計準則。文獻[25]針對由于小型體積的?PEF?的低頻段衰減能力較低以及高頻增益限制情況下?AEF?高頻段衰減能力有限的問題,利用電機驅動系統設計了一種基于?LCL-LC PEF?和模擬?AEF?集成的混合?EMI?濾波器,改進了混合?EMI濾波器的設計方法。文獻[26]采用了一種電流采樣電流補償(Current-Sensing Current-Compensating, ?CSCC)模式模擬?AEF?電路,同時增加高諧振頻率的小型?PEF?以抑制高頻段從而得到了良好的?CM ?EMI?衰減。

在上述的文獻研究中,由于?PEF?的體積限制和模擬?AEF?的高頻環路增益限制,集成無源和有源的EMI?濾波器是抑制?EMI?的可行解決方案,但已有參考文獻中基于系統的混合噪聲進行?EMI?濾波器設計,沒有針對性考慮系統?DM?和?CM?噪聲源特性。本文首先研究了同步?Buck DC-DC?變換器的?DM?和CM?噪聲源特性,然后基于噪聲源阻抗模型提出了一種混合?EMI?濾波器設計方法,以規范化設計寬頻混合有源?EMI?濾波器。

1同步?Buck DC-DC?變換器的電磁干擾分析

首先,分析同步?Buck DC-DC?變換器的噪聲源及其阻抗特性,研究同步?Buck DC-DC?變換器電磁干擾的產生特性;然后,基于同步?Buck DC-DC?變換器的電磁干擾分析,規范化設計相應的?EMI?濾波器或者優化設計現有的?EMI?濾波器。

1.1同步?Buck DC-DC?變換器的噪聲源阻抗分析

由于?SiC MOSFET?在導通和關斷時產生較高的du/dt?和?di/dt,與變換器本身存在的寄生電感和寄生電容相互作用,從而在同步?Buck DC-DC?變換器中產生了嚴重的電磁干擾。通過對同步?Buck DC-DC變換器中噪聲的路徑進行分析和測量,得到同步Buck DC-DC?變換器的噪聲源阻抗,可以分為?CM噪聲源阻抗和?DM?噪聲源阻抗。

同步?Buck DC-DC?轉換器的等效電路如圖?1?所示。CM?噪聲通過寄生電容?Cqg?和寄生電感?Lqg?從同步?Buck DC-DC?變換器半橋中點轉移到地面,考慮到散熱器和地之間的不完全連接,因此引入寄生電感?Lqg?的影響。同時分別考慮母線中?L?線和?N?線對地的寄生電容?Cb1?和?Cb2?的影響,以及印制電路板(Printed Circuit Board, PCB)布局寄生參數?Lpl、Lpn、Rpl?和?Rpn,可以得到同步?Buck DC-DC?轉換器中?CM阻抗網絡的等效電路和?CM?阻抗特性曲線,如圖?2

所示。VDC?為直流電壓源,L1?和?L2?分別為?L?線和?N線的直流隔離電感,Q1?和?Q2?分別為同步?Buck?控制管和續流管,Lout、Cout、Rout?分別為輸出電感、輸出電容和輸出負載。

同理,DM?阻抗網絡的等效電路和?DM?阻抗特性曲線如圖?3?所示。由于直流母線支撐電容的低阻抗特性,變換器的差模噪聲源阻抗?ZDM1?可以被忽略,因此直流母線支撐電容?Cin?決定了變換器的?DM阻抗特性,ESR、ESL?分別為直流母線支撐電容?Cin的寄生電阻和寄生電感。

1.2同步?Buck DC-DC變換器的CM/DM噪聲源分析

Buck DC-DC?變換器傳導?EMI?的實驗測試平臺如圖?4?所示,由?Buck DC-DC?變換器、EMI?濾波器、線路阻抗穩定網絡(Line Impedance Stabilization ?Network, LISN)、直流電壓源和電阻負載組成。基于?EMI?測試標準國際無線電干擾特別委員會?25(International Special Committee on Radio Interference 25, ?CISPR 25),可以分別測量?DC-DC?變換器的?DM?和CM?電磁干擾噪聲。

Buck DC-DC?變換器的兩個輸入端口分別接?L線和?N?線,測量設備?LISN?被放置在直流電源和?EMI濾波器之前。被測對象的傳導電磁干擾由?LISN?測量,分別可以得到?L?線和?N?線上對地的電壓?Vlisn+和?Vlisn-,然后經過差值和均值運算,分別得到變換器的?CM?電壓?VCM?和?DM?電壓?VDM。

基于實驗測量結果,通過式(1)和式(2)對CM?和?DM?電磁干擾噪聲進行分離提取,得到同步Buck DC-DC?轉換器中?CM?和?DM EMI?的頻域波形(150 kHz~30 MHz),如圖?5?所示。同步?Buck DC-DC?轉換器的原始電磁干擾噪聲,在?150~200 kHz頻段?DM?噪聲會對?EMI?濾波器的設計產生重要影響。為了有效地設計混合?EMI?濾波器,需要考慮低頻段?DM?噪聲的抑制,在?1~10 MHz?頻段?CM?噪聲幅值高于?DM?噪聲幅值,可以考慮通過有源濾波器進行抑制,在高頻段?10~30 MHz,考慮設計合理的無源濾波器參數進行電磁干擾的抑制。

2混合?EMI?濾波器設計

為了設計一個適合開關電源的混合?EMI?濾波器,基于文獻[1-2]中?EMI?濾波器設計過程,本文提出了一個系統的?EMI?設計流程,所提出的混合?EMI濾波器設計流程如圖?6?所示。EMI?濾波器的最重要的特性是衰減電磁干擾源的發射能力,其衰減率定義為插入損耗(Insertion Loss, IL)。為了讓?EMI?濾波器獲得最大插入損耗,在計算濾波器?IL?時需要考慮濾波器輸入輸出端的阻抗參數,在選擇?EMI?濾波器的拓撲結構時需考慮噪聲源和負載阻抗,包括LISN?的?CM-DM?回路阻抗。在確定所需的插入損耗ILReq?后,可以得到?EMI?濾波器組件的參數值。因此,必須利用?LISN?對同步?Buck DC-DC?變換器的原始噪聲進行測量,即沒有加入?EMI?濾波器情況下的CM?和?DM?電磁干擾噪聲測量。根據?CISPR 25?給定的峰值標準線,通過從測量的噪聲?Vmeasure?中減去指定的極限?ALimit?可以計算出所需的插入損耗?ILReq,并適當增加安全裕度值?ILMargin,有

通過計算?EMI?濾波器參數,使加入?EMI?濾波器后同步?Buck DC-DC?變換器符合?EMC?標準要求。為了確定?EMI?濾波器組件的參數值,需要將?ILReq與所計算的插入損耗?ILcalc?進行比較,在符合?EMC標準的要求情況下(包括?CM?和?DM?電磁干擾),計算?EMI?濾波器組件參數,使?ILReq?和?ILcalc?的二次方均值在整個頻率范圍內最小。同時,整個過程的必要條件為?ILcalc≥ILReq。

設計同步?Buck DC-DC?變換器對應的?EMI?濾波器之前,必須計算出各個濾波器組件的實際參數值,實際參數值可以用矢量/阻抗網絡分析儀進行測量,然后給定方程再次計算插入損耗?ILcalc。如果?CM?和DM?的?ILcalc?仍然大于?ILReq,則可以從選定的組件參數設計?EMI?濾波器。若不滿足?ILcalc≥ILReq,則需要調整所選組件參數值,重新計算?ILcalc?是否滿足條件。在滿足條件后,搭建混合?EMI?濾波器原型,插入?LISN?和同步?Buck DC-DC?變換器之間,通過測量插入?EMI?濾波器前后的?EMI?噪聲來評估?EMI?濾波器的抑制效果。由于所選定的?EMI?濾波器組件存在高頻寄生參數,往往并不具有理想的特性,比如組件內部元器件的高頻寄生參數和組件間電磁耦合的影響,因此會導致測量的?EMI?噪聲和期望的?EMI噪聲不一樣。當?EMI?噪聲仍然大于?CISPR 25?標準限值時,需要添加級聯阻尼、替換寄生參數更少的組件以及解耦設計(若混合有源濾波器無法滿足設計要求,需要設計解耦電路以隔離?Buck?電路與外部電路之間的噪聲干擾),進而需要對整體布局或者組件進行優化設計,并重新計算?ILcalc?直至滿足所需EMI?抑制要求。

2.1無源?EMI?濾波器設計

無源?EMI?濾波器采用?CL?結構和?π?型結構來分別衰減?CM?和?DM?信號,如圖?7a?所示。無源?EMI濾波器的?CM?和?DM?等效電路,如圖?7b?和圖?7c?所示。無源?CM?濾波器由兩個并聯的?Y?型電容器?Cy和一個共模扼流圈?Lc?組成(見圖?7b)。同理,無源DM?濾波器由?X?電容器?Cx、共模扼流圈漏感?Lc_lk和兩個?Y?型電容器串聯組成(見圖?7c)。

由式(4)可計算無源?EMI?濾波器插入損耗ILcalc,VZ'_LISN?為未插入濾波器前?ZLISN?兩端的電壓,ZLISN?為?LISN?兩端的阻抗,VZ_LISN?為插入濾波器后

式中,ZLISN_CM、ZLISN_DM?分別為?LISN?的共模阻抗、LISN?的差模阻抗;ZL_c、ZL_c_lk?分別為共模扼流圈Lc?阻抗、共模扼流圈漏感?Lc_lk?阻抗;ZC_y、ZC_x?分別為?Y?型電容器?Cy阻抗、X?型電容器?Cx阻抗;ZS_CM、ZS_DM?分別為噪聲源共模阻抗以及噪聲源差模阻抗。

設定無源?EMI?濾波器各個組件的參數值,通過設計流程得到滿足?EMC?標準的無源?EMI?濾波器,但由于單一的無源?EMI?濾波器通常體積較大,為了提高開關電源的功率密度,本文在基于無源?EMI?濾波器的基礎上,加入模擬有源?EMI?濾波器設計,從而在寬頻范圍內增加系統的?EMI?抑制效果。

2.2模擬有源?EMI?濾波器設計

本文采用電流采樣電流補償?CSCC?模式模擬有源濾波器電路(基于式(11)和?Buck DC-DC?變換器中低頻段?ZS_CM?ZLISN_CM,抑制同步?Buck DC-DC變換器中共模回路的共模?EMI?噪聲信號,其等效電路拓撲如圖?8?所示。

圖?8a?展示了沒有插入模擬有源濾波器的同步Buck DC-DC?變換器、LISN?和直流源的測試電路中共模回路等效拓撲,圖中,iS_CM?為同步?Buck DC-DC變換器中共模噪聲的等效電流源,因此同步?Buck DC-DC?變換器共模回路中?LISN?兩端的電壓可以表示為

在?LISN?和同步?Buck DC-DC?變換器之間插入CSCC?模式模擬有源濾波器電路后,其共模回路等效拓撲,如圖?8b?所示。共模回路中?LISN?兩端的電壓可以表示為

模擬有源?EMI?濾波器與無源?EMI?濾波器類似,插入損耗與測試平臺?LISN?阻抗和噪聲源阻抗有關。當?Z Z?S_CM LISN_CM???時,模擬有源?EMI?濾波器插入損耗?ILcalc?滿足最大插入損耗的條件,且?ZLISN_CM?≈25?Ω,約為?28 dBΩ,由圖?2?可知,在中低頻情況下(?ZS_CM> ≈?250 48 dB?Ω Ω?)容易滿足?ZS_CM??ZLISN_CM?。

2.3混合?EMI?濾波器設計

由于同步?Buck DC-DC?變換器的共模阻抗?ZS_CM在高頻階段通常會產生?RLC?諧振點(見圖?2),阻抗不能總是滿足?Z Z?S_CM LISN_CM???,因此為了減少高頻信號對有源?EMI?濾波器的影響,基于模擬有源EMI?濾波器的拓撲結構,將無源?EMI?濾波器插入在模擬有源?EMI?濾波器與噪聲源之間,從而得到混合模擬有源和無源?EMI?濾波器,如圖?9?所示。插入混合?EMI?濾波器后,在電流注入節點可得

基于式(6)和式(15),將混合?EMI?濾波器插入損耗?ILcalc?代入圖?6?設計流程,完成濾波組件參數計算,最終實現混合?EMI?濾波器的設計,所計算得到的混合?EMI?濾波器組件的參數值見表?1。

將式(1)、式(2)所得到的結果,以及?CISPR ?25?準峰值代入式(3),可得到?ILReq_CM?和?ILReq_DM所需?CM?和?DM?插入損耗,如圖?10?所示。在無源EMI?濾波器設計部分,通過式(5)、式(6)代入

表?1?參數值和噪聲源阻抗(見圖?2?和圖?3),可計算得到?ILcalc_CM?和?ILcalc_DM,由于參數值選擇以及電路諧振的影響,計算得到的無源?EMI?濾波器的共模插入損耗?ILcalc_DM?并不滿足?ILcalc≥ILReq?的條件,因此本文加入模擬有源?EMI?濾波器部分增加共模插入損耗。在增益為?8?倍的情況下,通過式(15)計算得到混合?EMI?濾波器的寬頻共模插入損耗ILcalc_hyb_CM?均滿足?ILcalc≥ILReq。

3實驗驗證

為了驗證第?2?節中理論計算的準確性,在本節中進行基于同步?Buck DC-DC?變換器的濾波器實驗,如圖?11?所示。在實驗中,控制管?Q1?和同步管Q2均采用?CREE?公司的?SiC MOSFET C2M1000170D,由現場可編程邏輯門陣列(Field Programmable Gate ?Array, FPGA)產生驅動信號,運算放大器為德州儀器?LM7171,直流源電壓設置為?400 V,水泥負載為20?Ω。雙管?SiC MOSFET?的開關頻率為交替互補的50 kHz,死區時間為?0.05?μs。

基于表?1?中混合?EMI?濾波器組件的參數,選取對應的元器件,搭建實驗平臺,分別通過?LISN?測

量同步?Buck DC-DC?變換器的原始?EMI?噪聲和加入混合?EMI?濾波器后的?EMI?噪聲效果,對比如圖?12所示。通過實驗結果可知,加入混合?EMI?濾波器后EMI?噪聲抑制效果較好,整個頻段內平均抑制近35 dB。

在所提的混合濾波器設計方法下,本文研究了不同輸入電壓情況下濾波前后的系統效率對比,如圖?13?所示。由于增加了混合濾波器部分,會使得系統的效率有所下降,效率平均下降?1.24%。

4結論

本文提出了一種基于同步?Buck DC-DC?變換器的寬頻混合?EMI?濾波器設計方法。為了一個有效的EMI?濾波器,在設計過程中,除了需要了解同步Buck DC-DC?變換器?CM?和?DM?噪聲源的電磁干擾特性,還需要考慮同步?Buck DC-DC?變換器的?CM和?DM?噪聲源阻抗以及負載阻抗。 ? ? ?通過計算?EMI?濾波器的插入損耗,得到?EMI

濾波器的設計參數,但由于較小體積的無源?EMI?濾波器組件不能滿足插入損耗的要求,這將使得設計的?EMI?濾波器不能滿足?EMC?標準的要求。為了增大?EMI?濾波器的插入損耗而不增加無源?EMI?濾波器體積,給出了混合有源和無源?EMI?濾波器的設計流程,以滿足?EMI?濾波器插入損耗的需求和?EMC標準。最后,基于同步?Buck DC-DC?變換器實驗平臺,制作了混合?EMI?濾波器的實驗電路,驗證了寬頻混合?EMI?濾波器的電磁干擾抑制效果。

![[java八股文][Java并發編程面試篇]場景](http://pic.xiahunao.cn/[java八股文][Java并發編程面試篇]場景)

)

基礎命令和操作)

)

![[Linux]從零開始的STM32MP157 Buildroot根文件系統構建](http://pic.xiahunao.cn/[Linux]從零開始的STM32MP157 Buildroot根文件系統構建)

:LeetCode 239. 滑動窗口最大值(Sliding Window Maximum)詳解)

轉為 pdf)