設計目的

為后級提供足夠的增益以克服后級電路噪聲

盡可能小的噪聲和信號失真

確保輸入和輸出端的阻抗匹配

確保信號線性度

評價標準

噪聲系數

功率增益

工作頻率和帶寬

輸入信號功率動態范圍

端口電壓駐波比

穩定性

基于SP模型的LNA設計

直流分析

S參數分析

設計指標 :

噪聲系數:

增益:

工作頻率和帶寬

輸入信號功率動態范圍

端口駐波比

穩定性

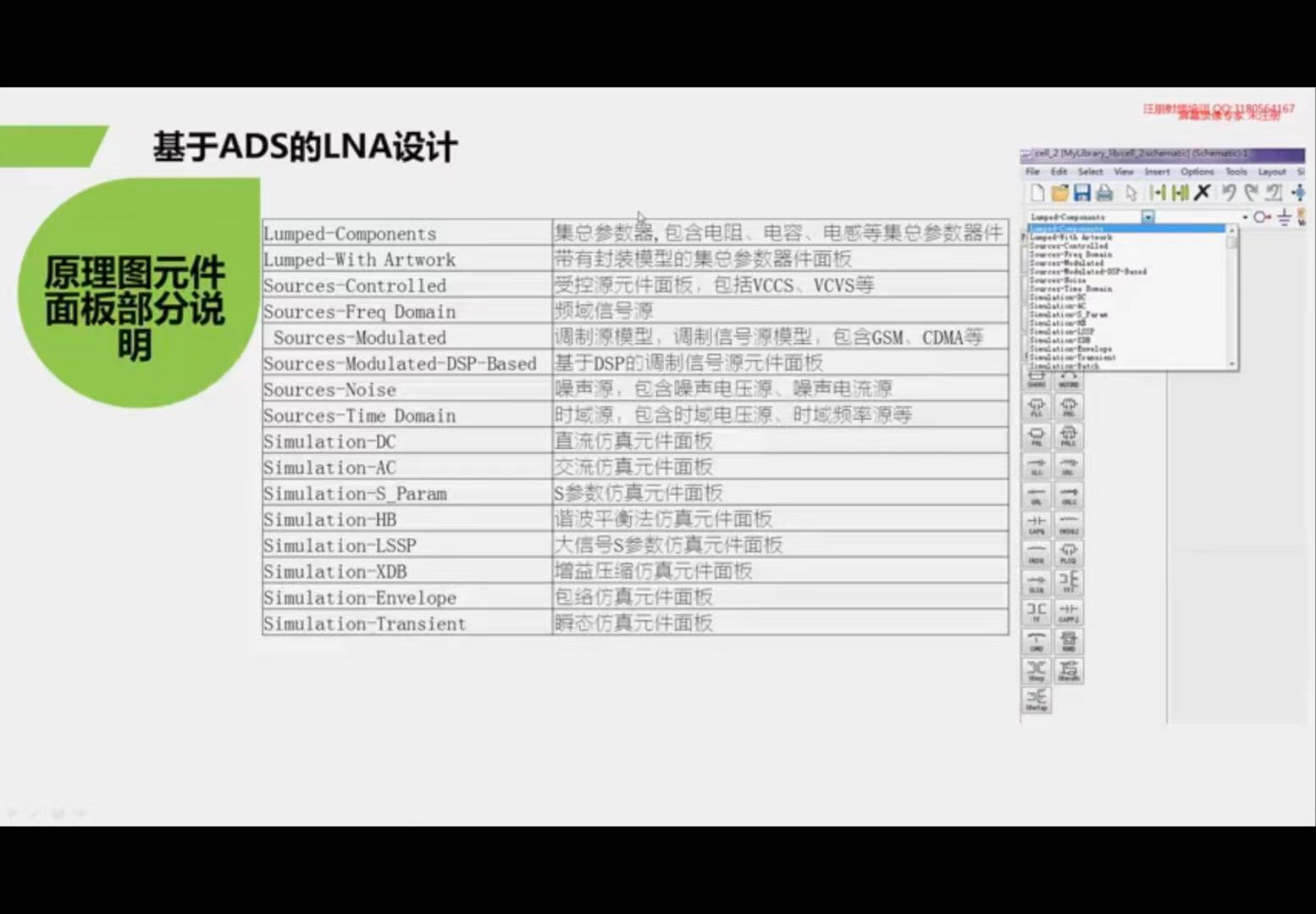

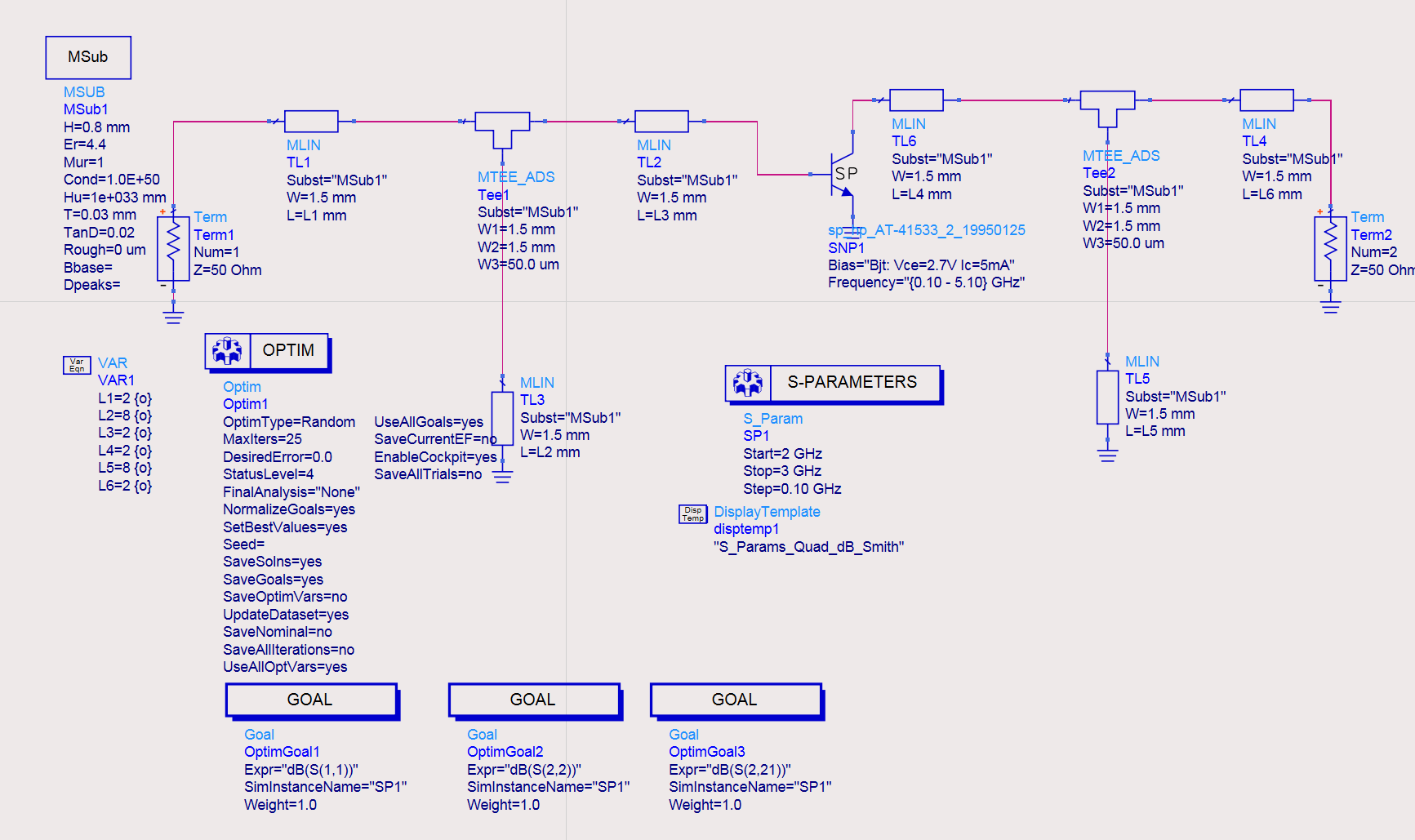

sp模型分為"pb_hb_"和"sp_hb_",其中第一個是封裝類模型(用于直流和偏置電路掃描設計),第二個是S參數模型,用于射頻性能仿真。

設計步驟:

SP模型制作安裝

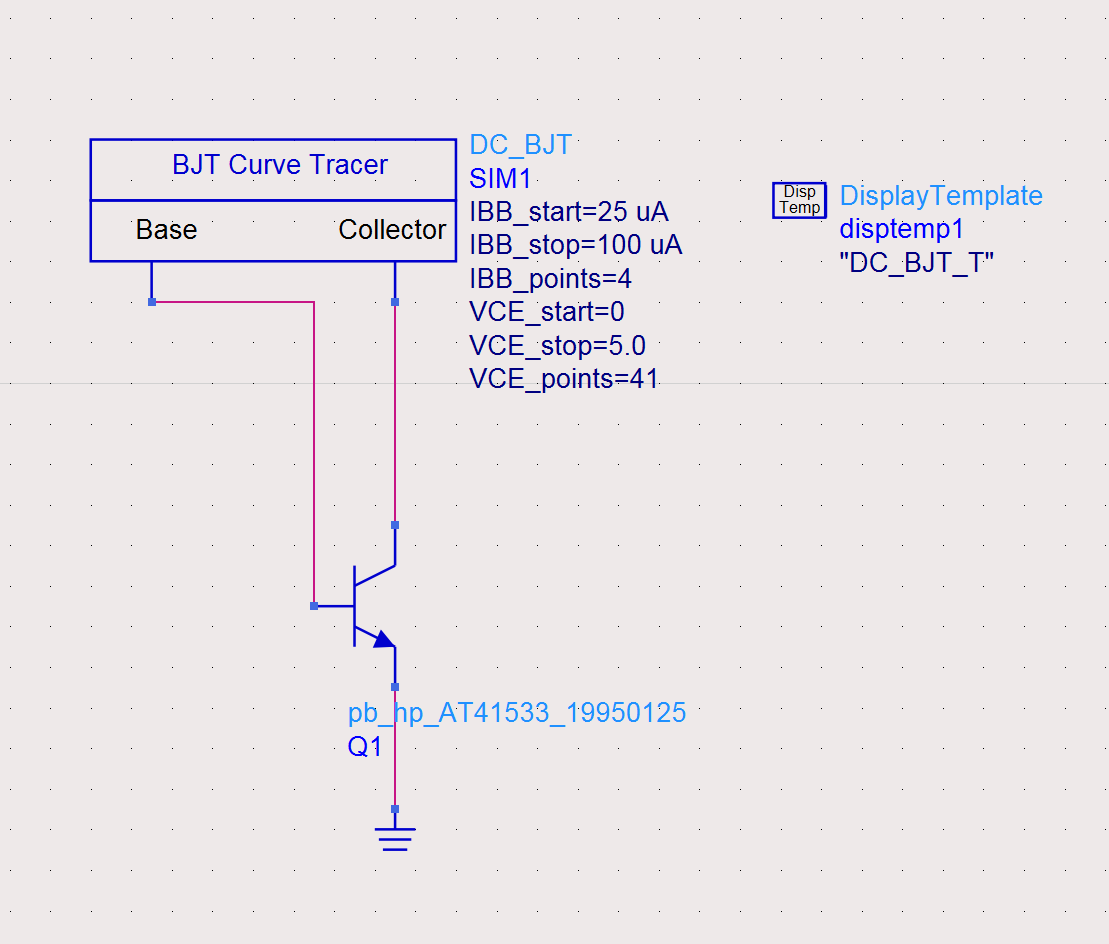

直流工作點掃描和選取

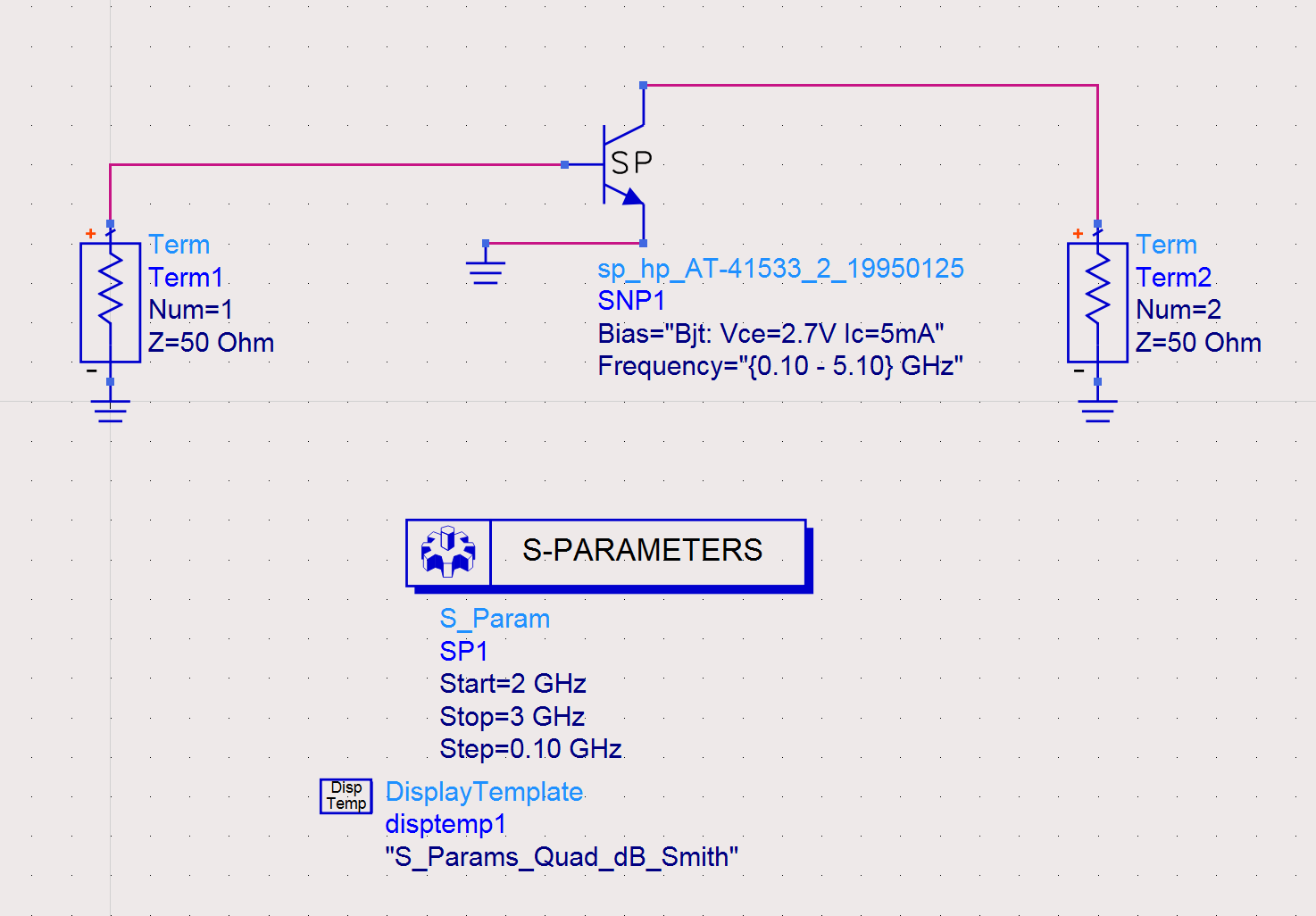

S參數特性仿真

阻抗匹配

穩定性、噪聲系數、增益的優化仿真

以AT41533設計:NF<2.5dB;Gain>8dB;VSWR<2;K>1

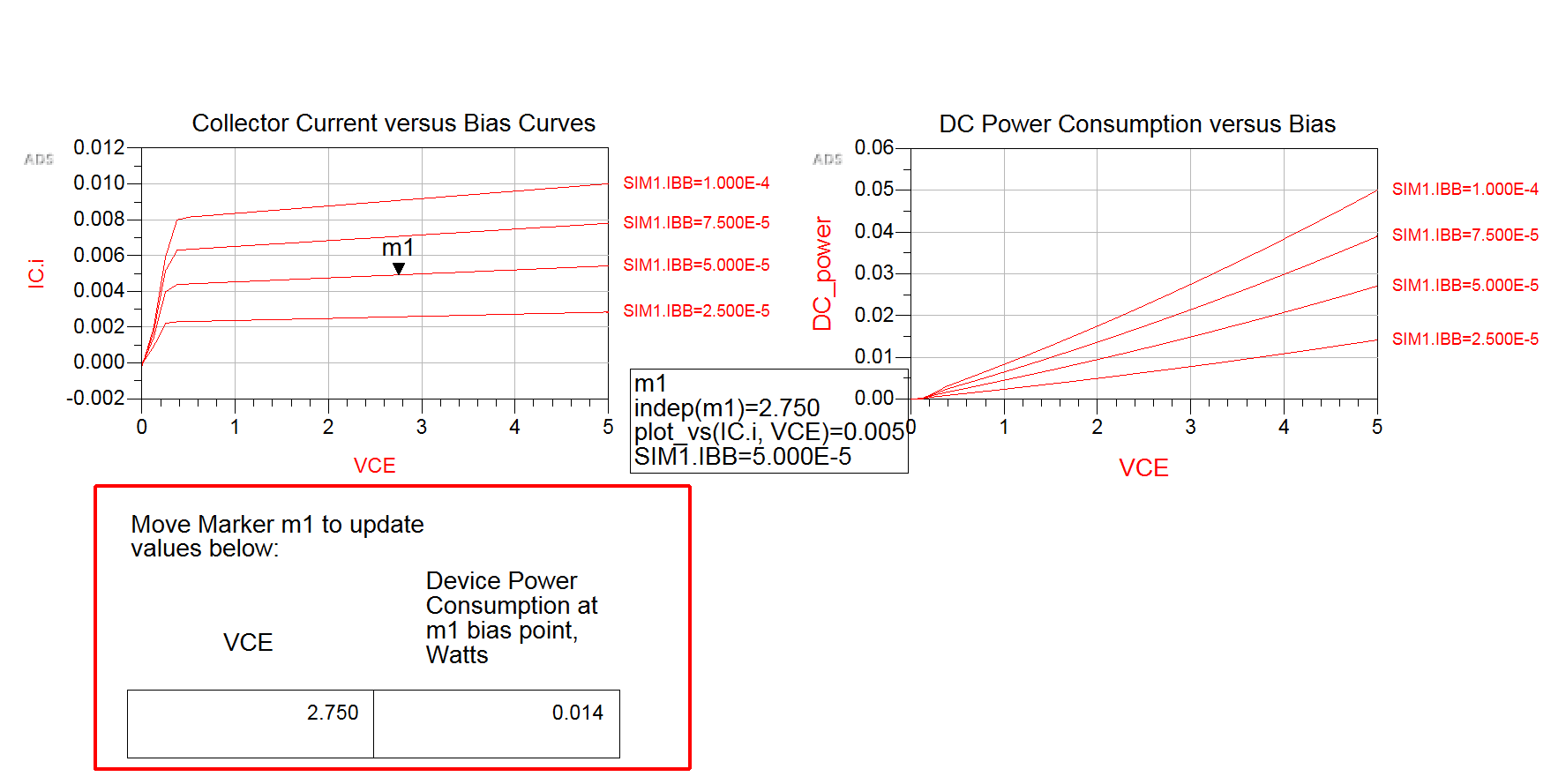

選擇工作點(Vce=2.7V,Ic=5mA)

BJT Curve Tracer:能測量 BJT 的各種特性曲線,如輸入特性曲線(基極電流\(I_B\)與基極 - 發射極電壓\(V_{BE}\)的關系)和輸出特性曲線(集電極電流\(I_C\)與集電極 - 發射極電壓\(V_{CE}\)的關系)。通過這些曲線,可以直觀地了解 BJT 在不同工作條件下的電氣性能。

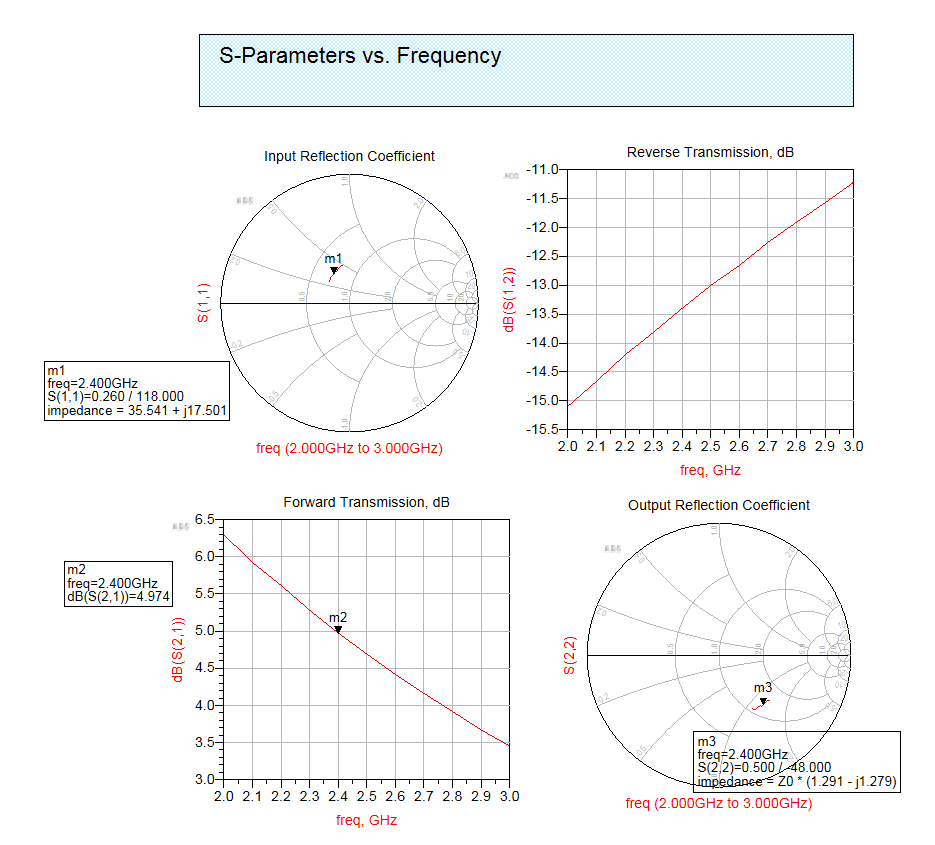

S參數分析:

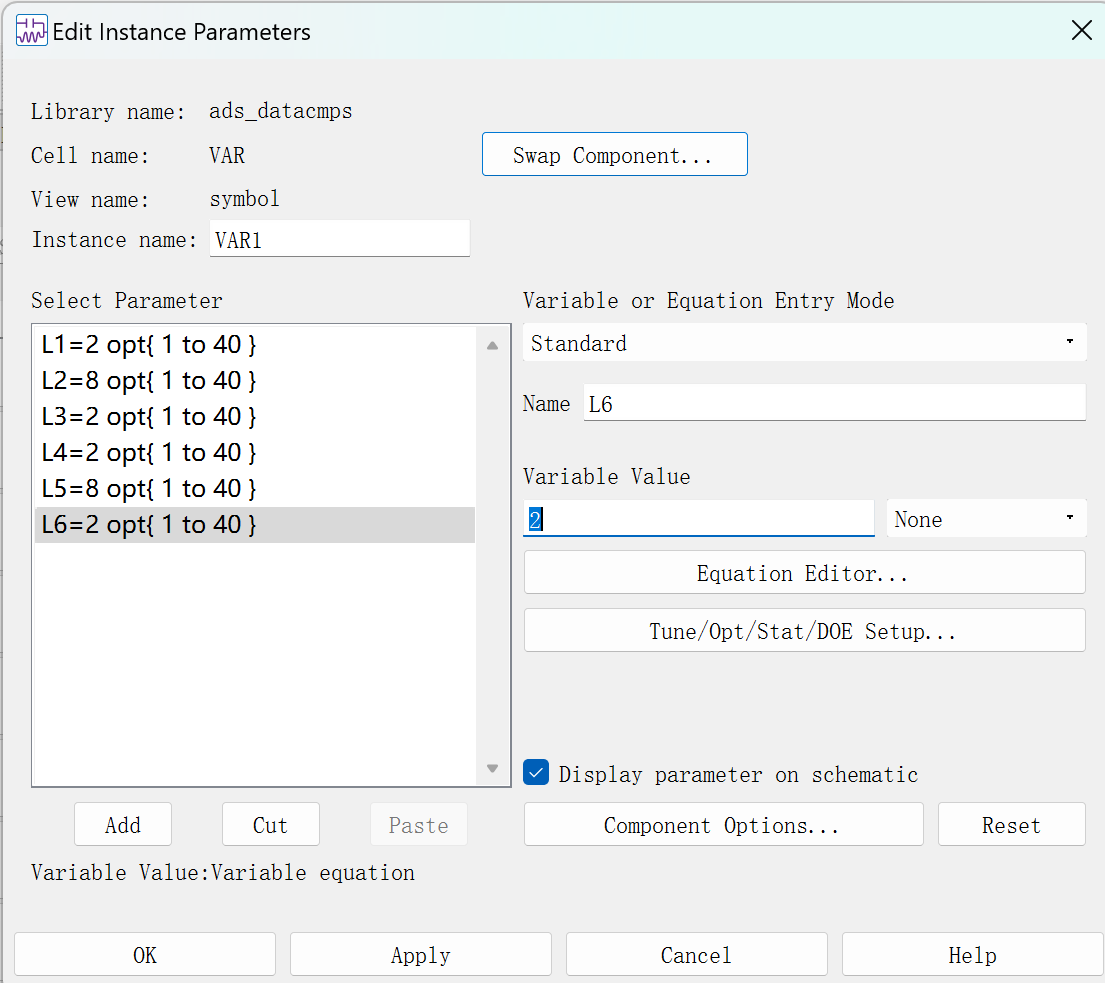

增益=4.97<8,用微帶線進行阻抗匹配:

?微帶線:寬度決定特性阻抗、長度決定電容電感特性。

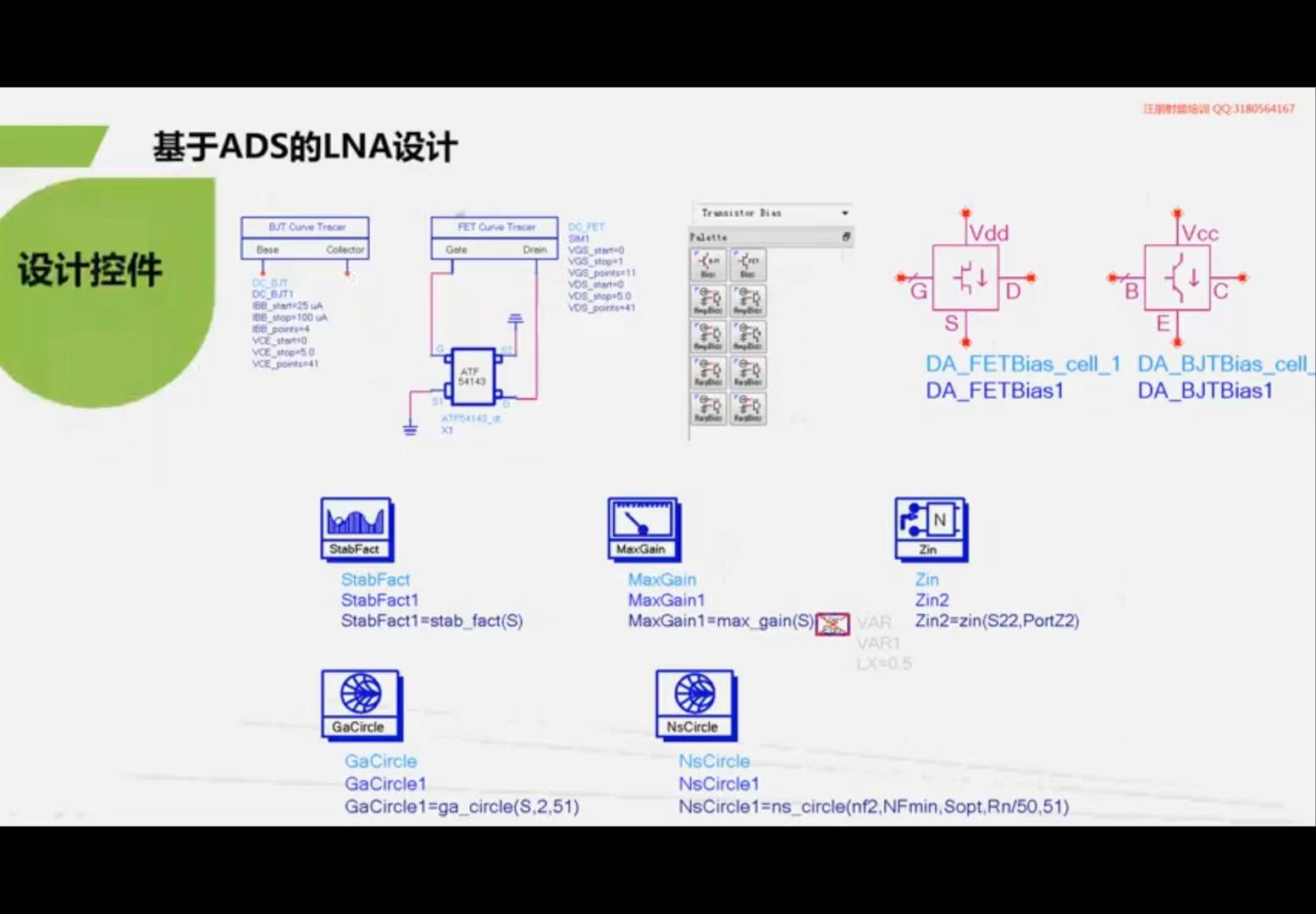

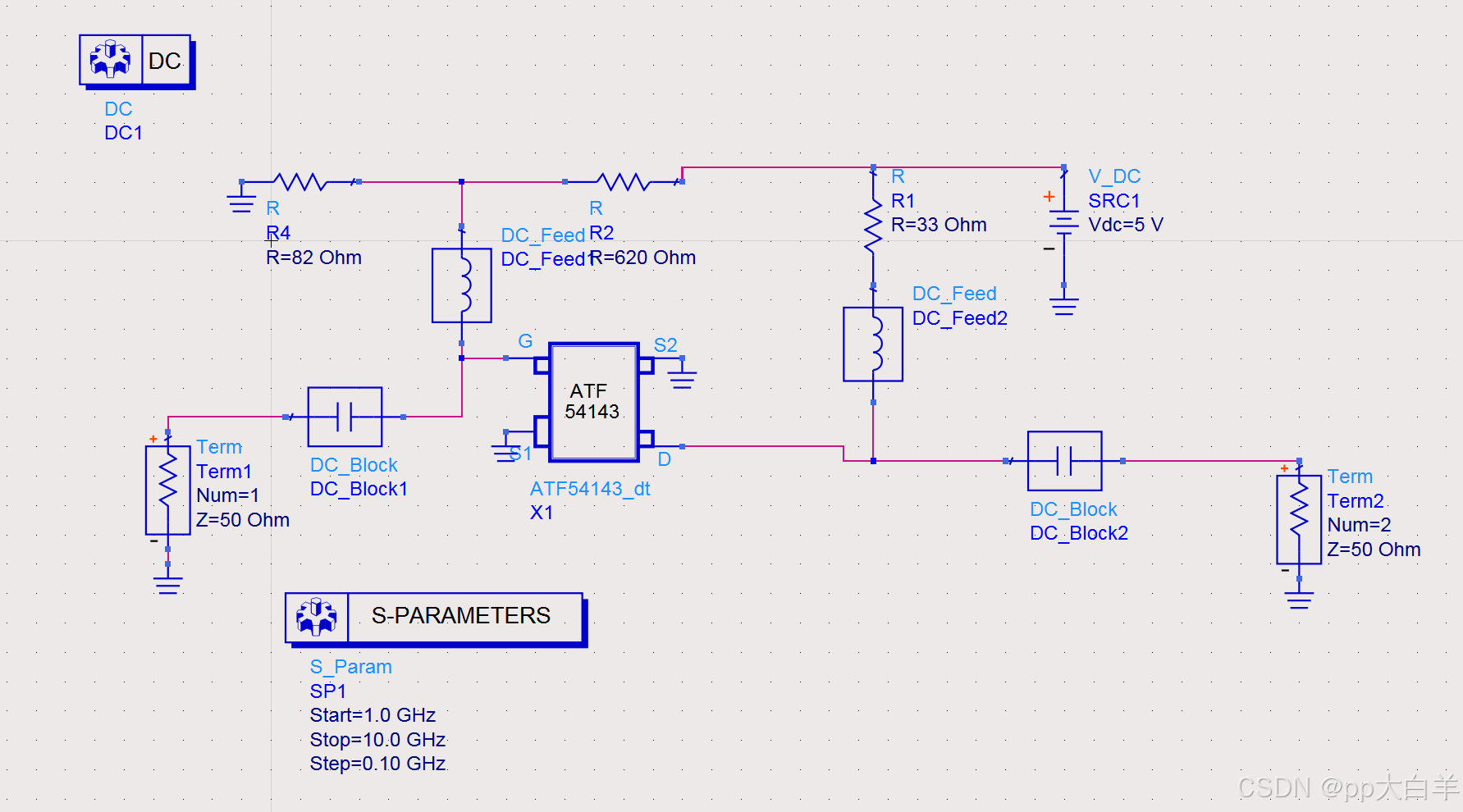

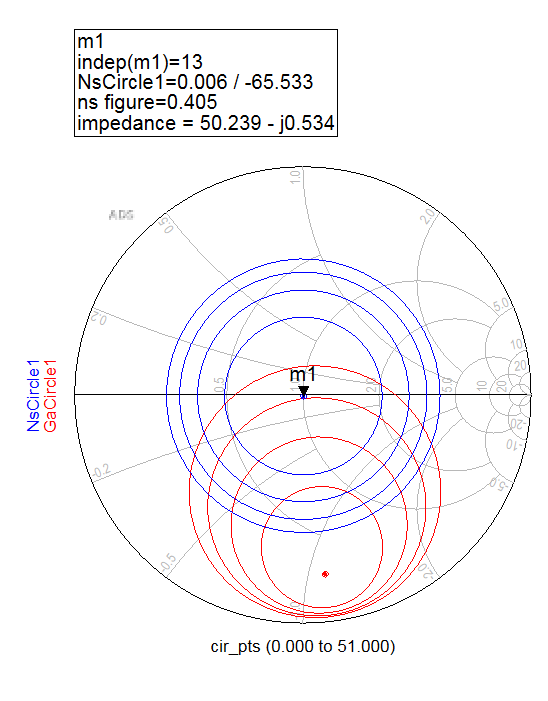

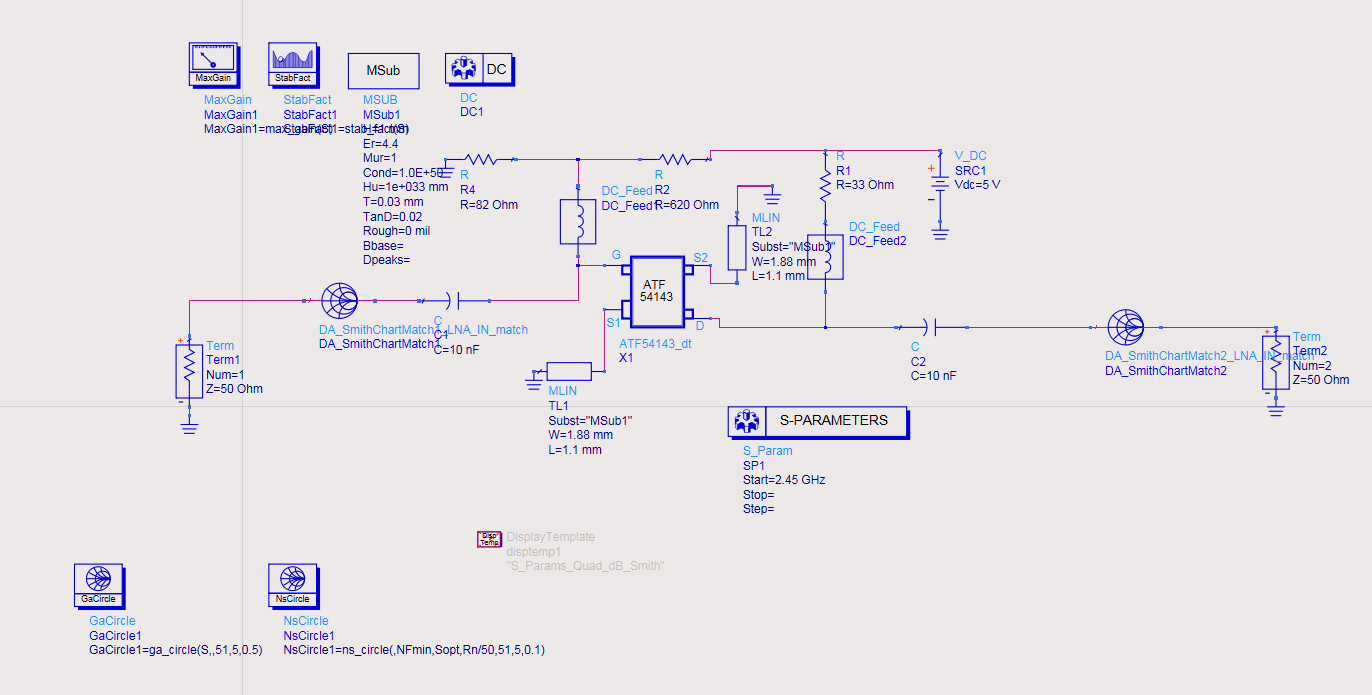

基于實際晶體管模型的LNA設計

控件:直流伏安特掃描控件、偏置電路掃描控件、

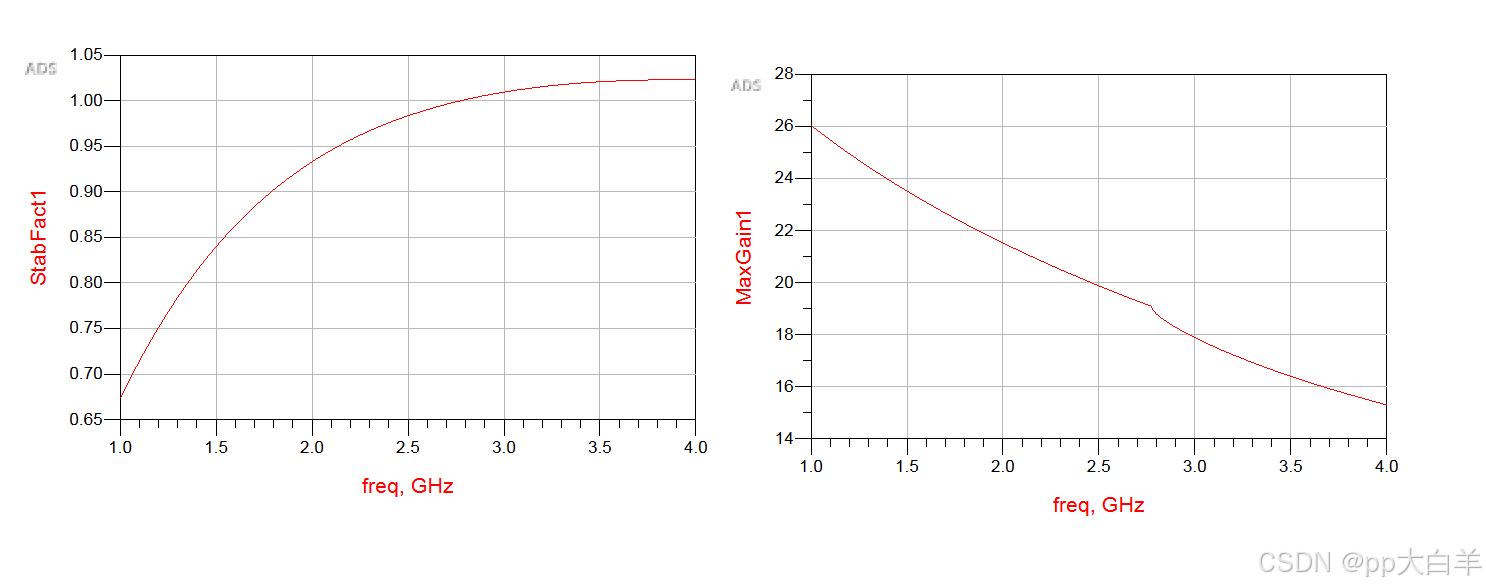

- 通過S參數分析晶體管絕對穩定特性和最大轉移增益是否滿足要求

- 根據數據手冊選取靜態直流工作點(根據噪聲系數、增益等要求)

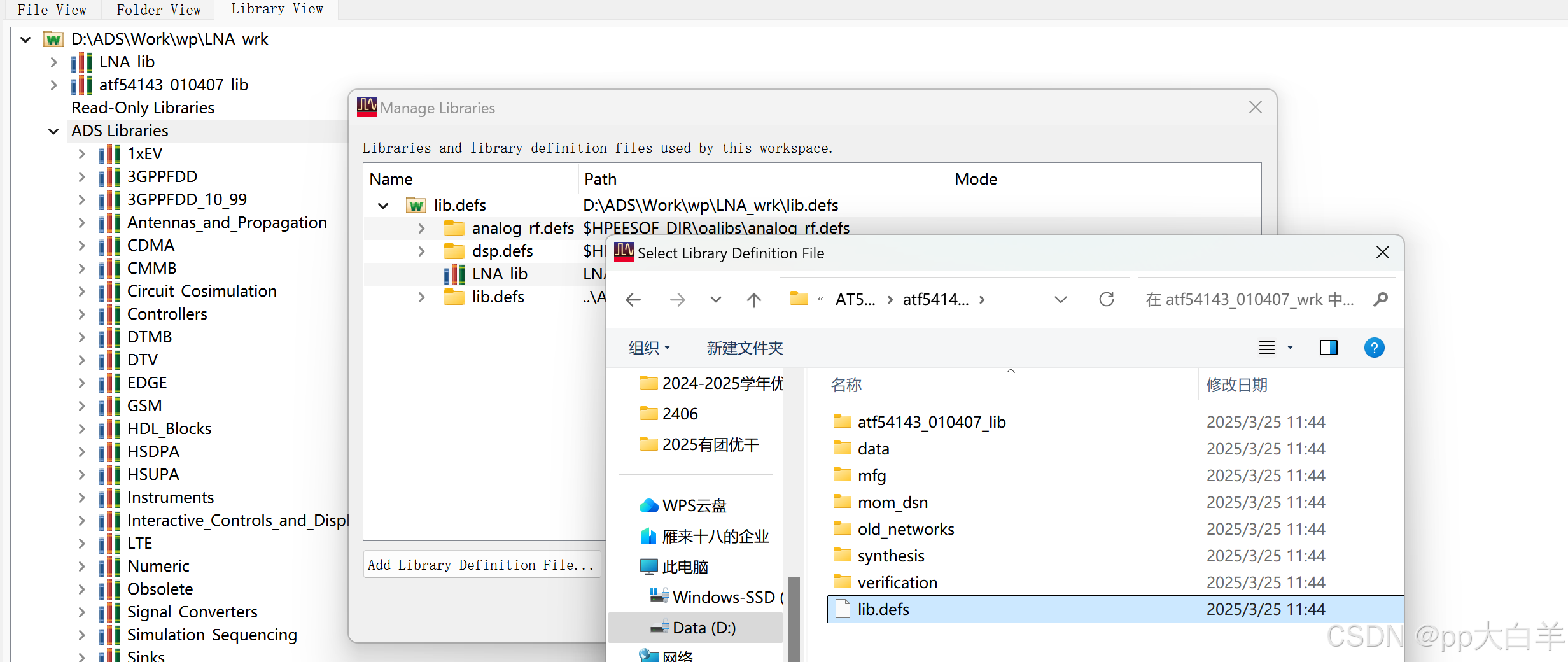

- 晶體管庫文件安裝

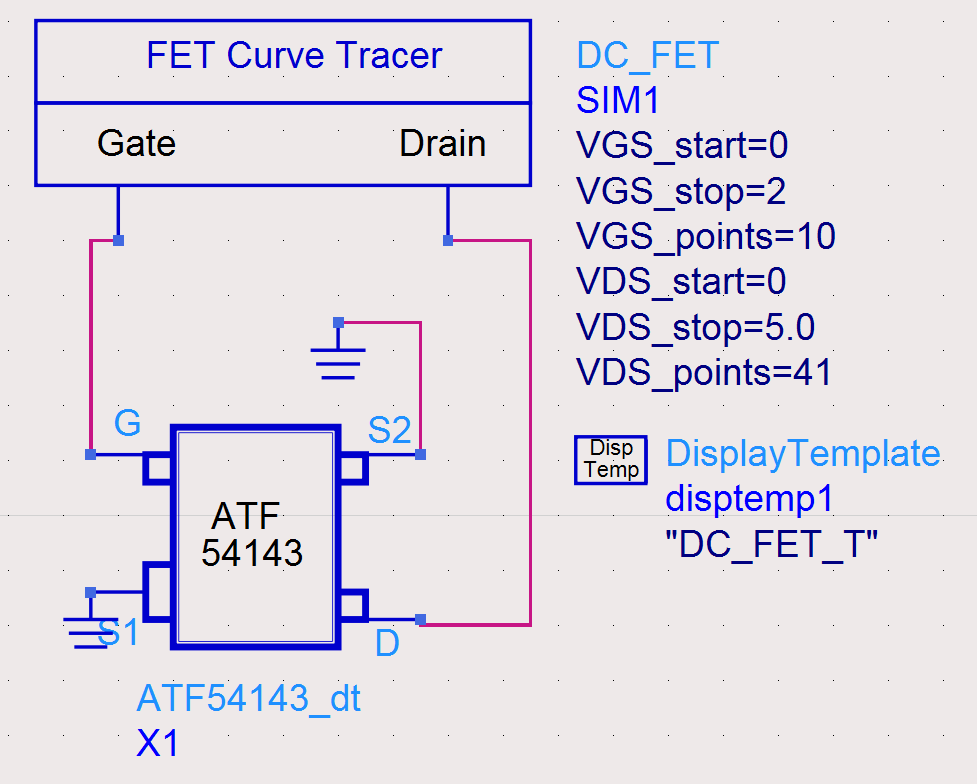

- 添加DC_BJT或DC_FET控件進行晶體管直流特性分析

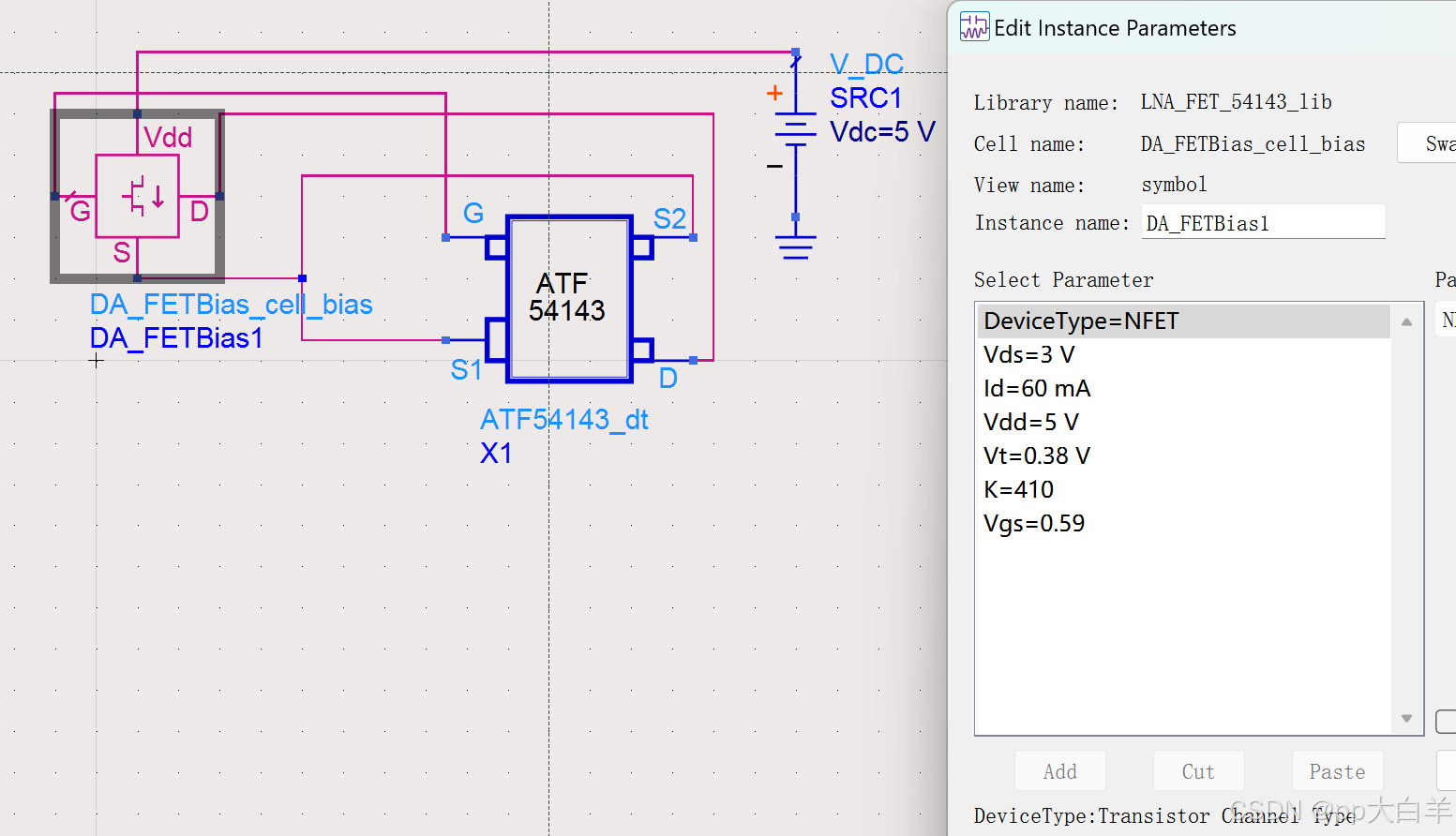

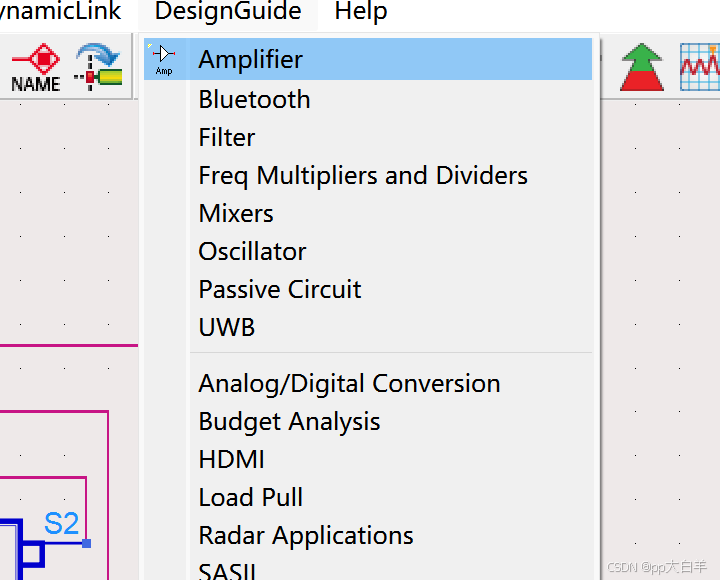

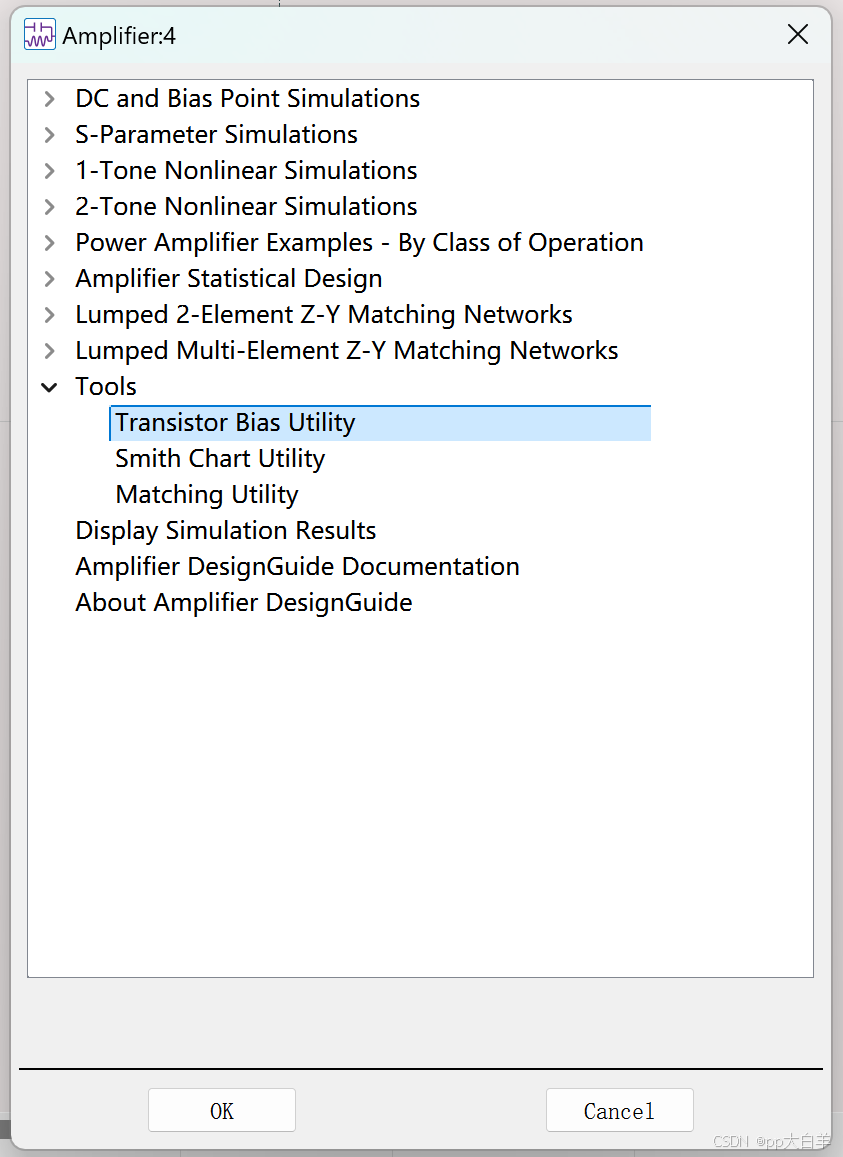

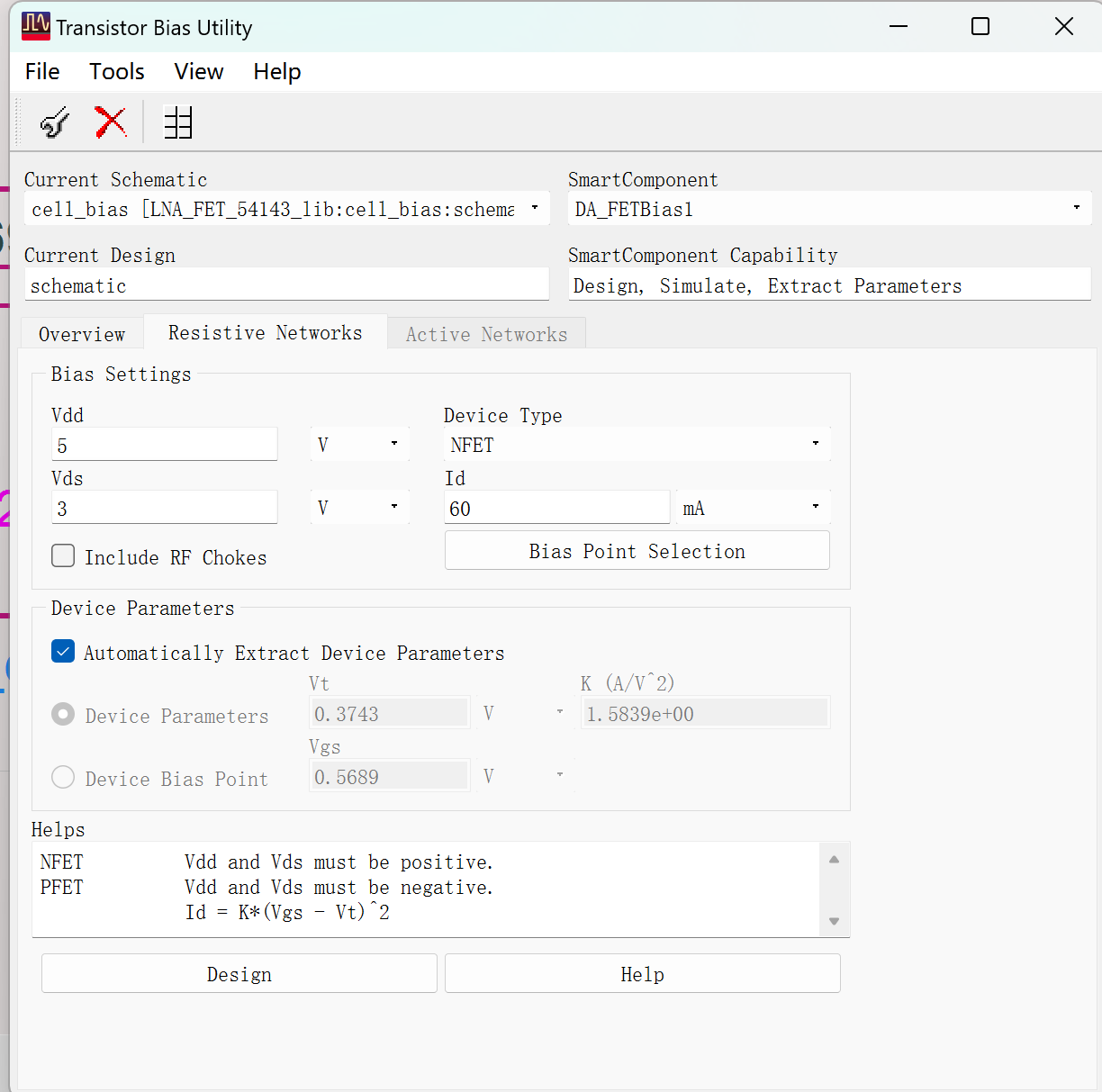

- 在TransistorBias面板選擇偏置電路控件完成偏置電路設計

- 利用stabfact和Maxgain控件求解偏置電路下的穩定因子K曲線和最大增益曲線

- 若K或Gain不滿足要求,修改電路或更換晶體管

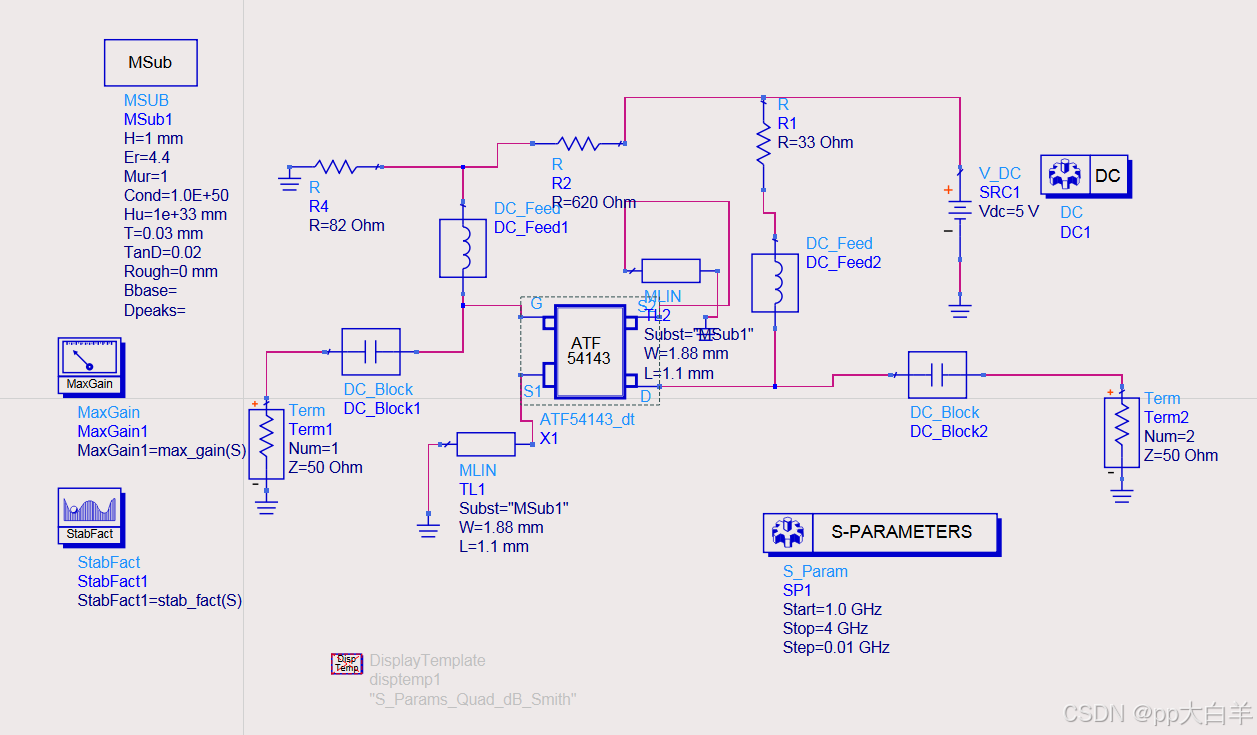

- 如果電路中電感為非標準值,則需要將電感值轉換為微帶線

(經驗公式)

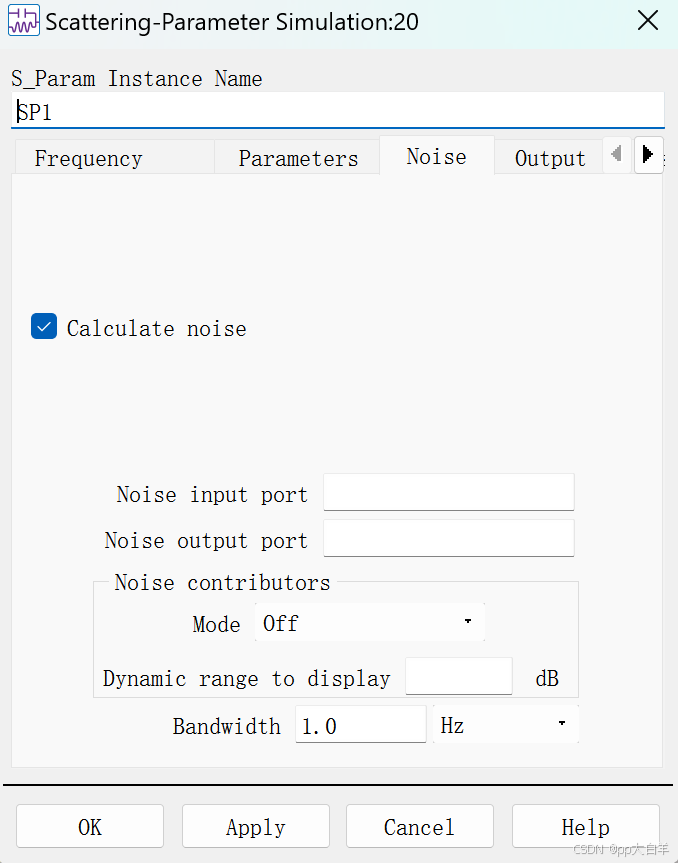

- 仿真已選偏置電路下的噪聲系數,通過開啟S參數仿真控件“Calculate noise”

- 輸入阻抗求解

- 輸入阻抗匹配

- 輸出阻抗求解

- 輸出阻抗匹配

本質就是一個真實的、接近事實應用環境的晶體管模型,可以直接應用于實際電路設計,其封裝的內部電路結構與實際完全一致。

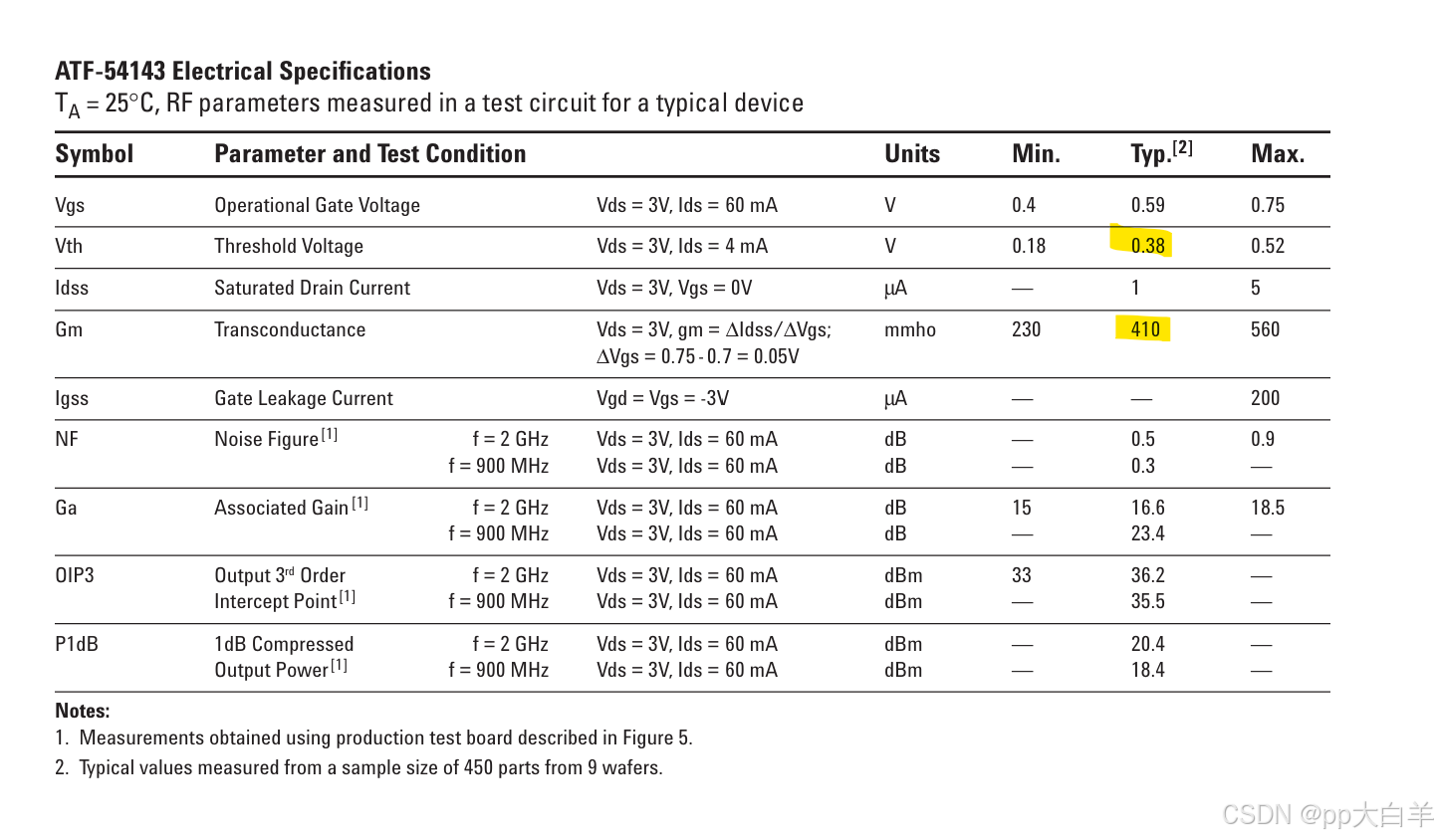

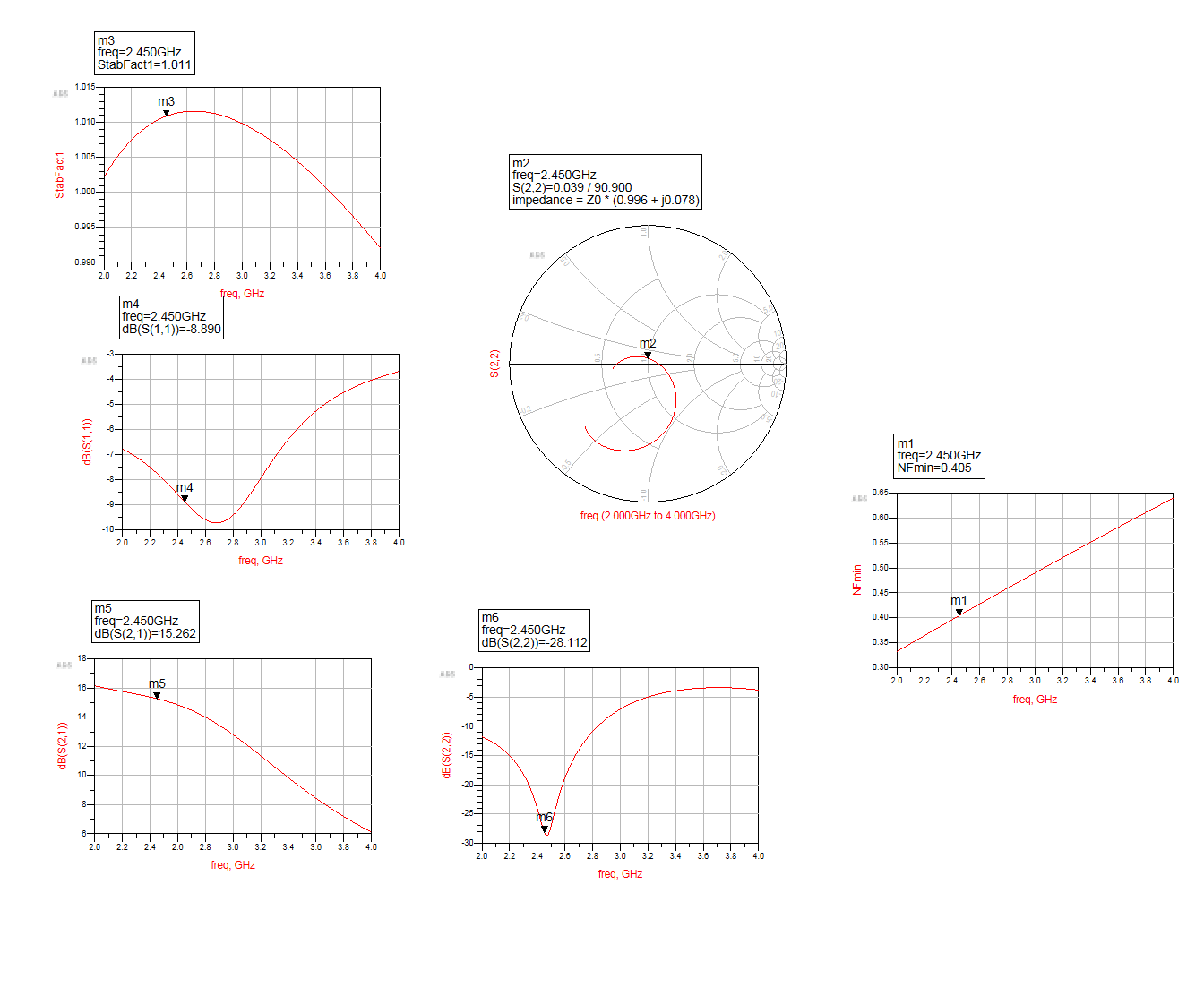

設計指標:NF<0.6dB;Gain>15dB;K>1

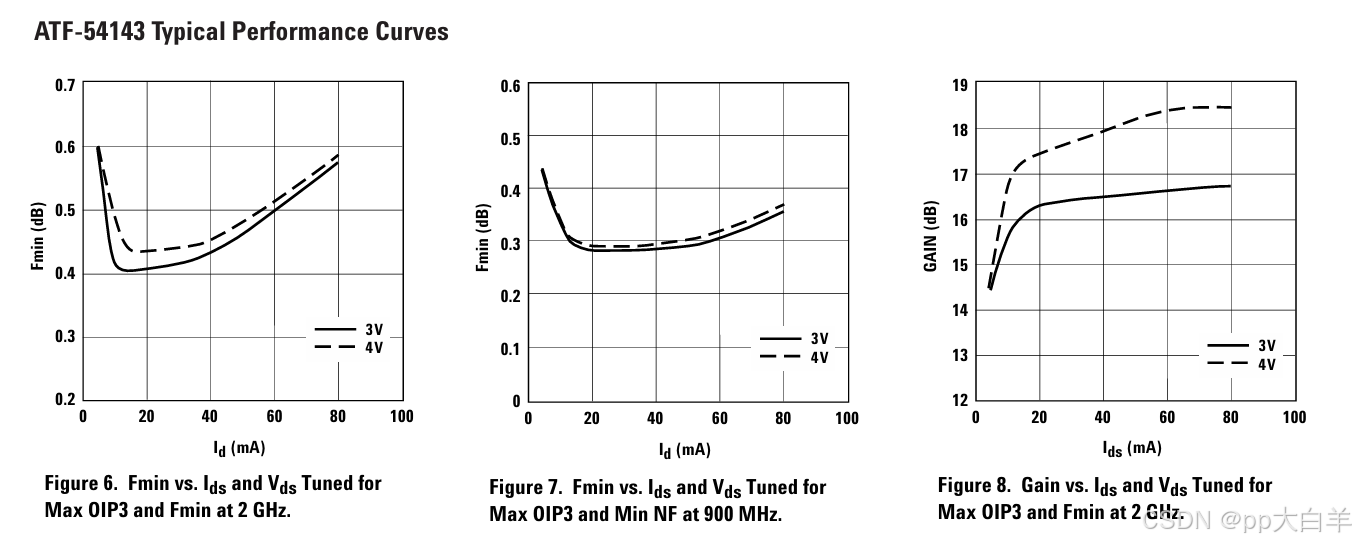

由圖1、3可知:當vds(vce)=3V、Ids(Ic)在10mA~60mA時滿足NF<0.5,且Ids>10mA時,Gain>15dB.

因此可以在Vds=3V,Ids在10mA~60mA時任選一點作為靜態工作點滿足設計指標。

比如我們選擇Vds=3V,Ids=20mA,選好靜態工作點后就可以設計偏置電路(ADS自動設計)

導入庫 ?

?

靜態工作點選擇(分析福安特性曲線):

柵極連接Gate,漏極連接Drain,源極接地

VGS_start:柵極起始電壓;VGS_stop:柵極終止電壓;VGS_point:柵極電壓采樣點

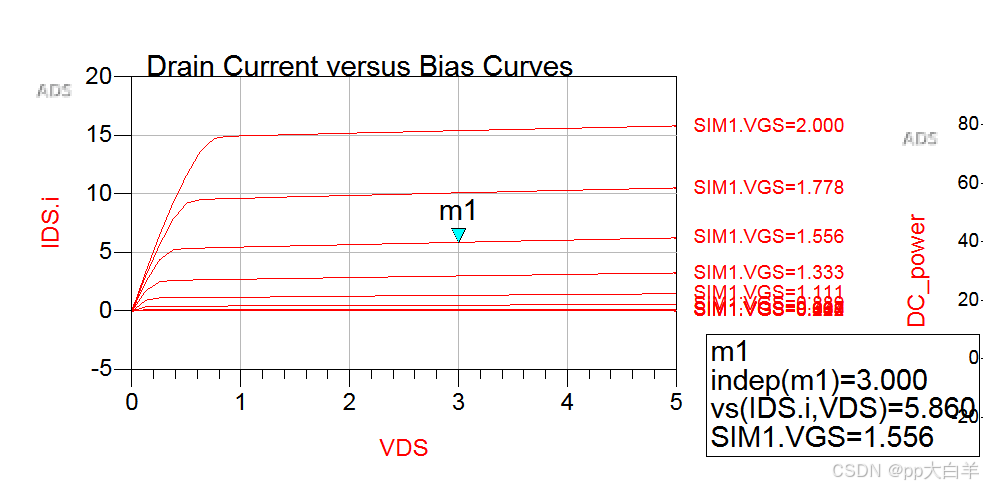

結果(m1:3V,60mA)

偏置電路設計

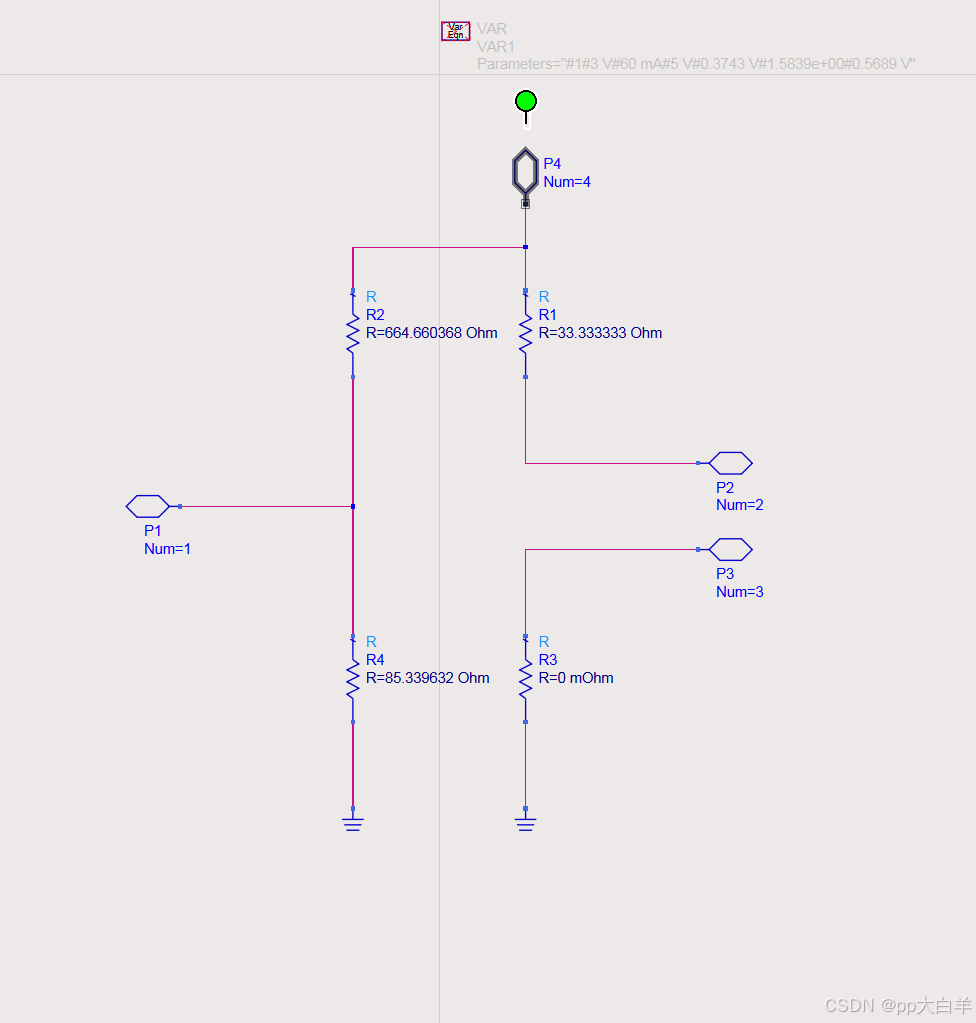

自動設計好的偏置電路:?

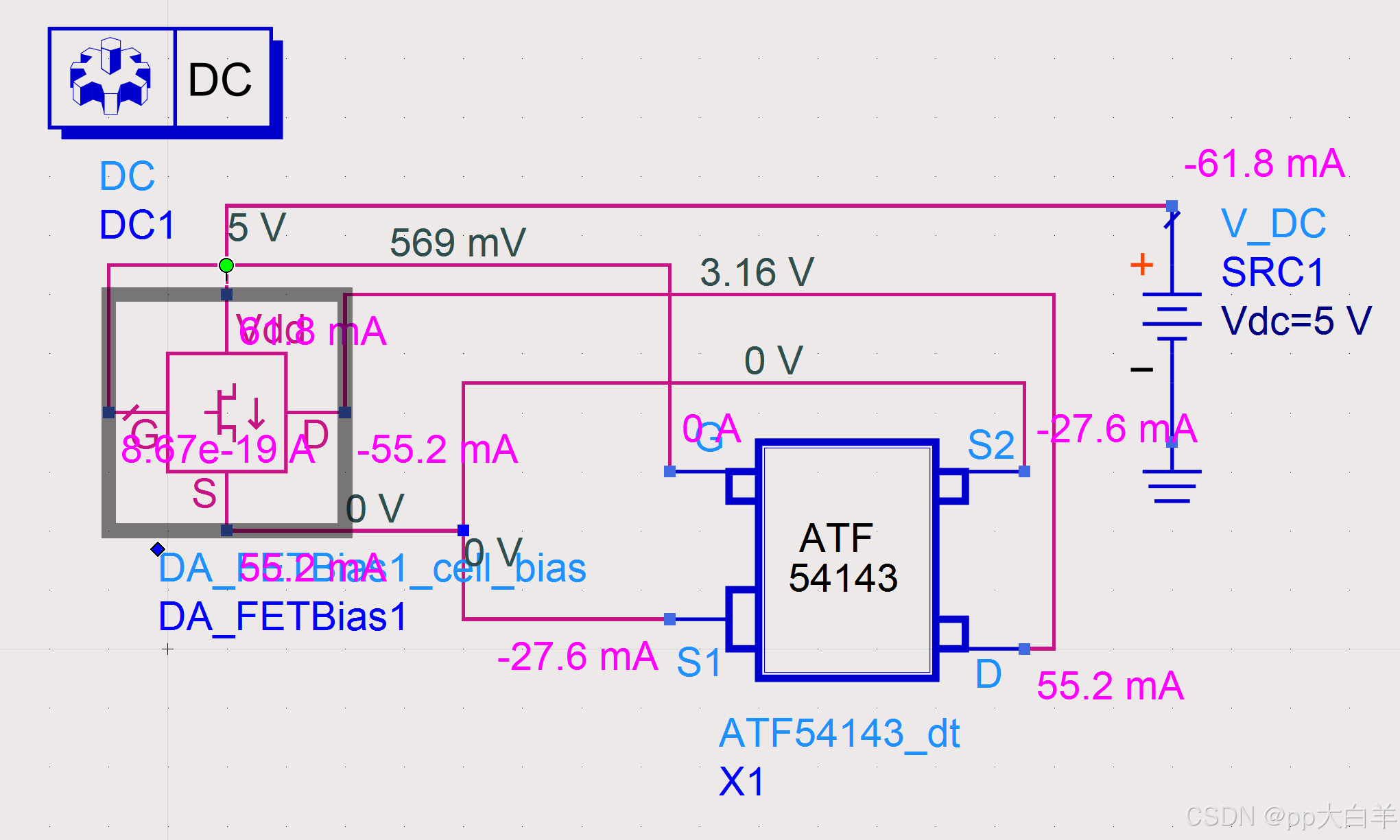

?查看結果并調整

?查看結果并調整

Vds不足60mA,調整偏置電路

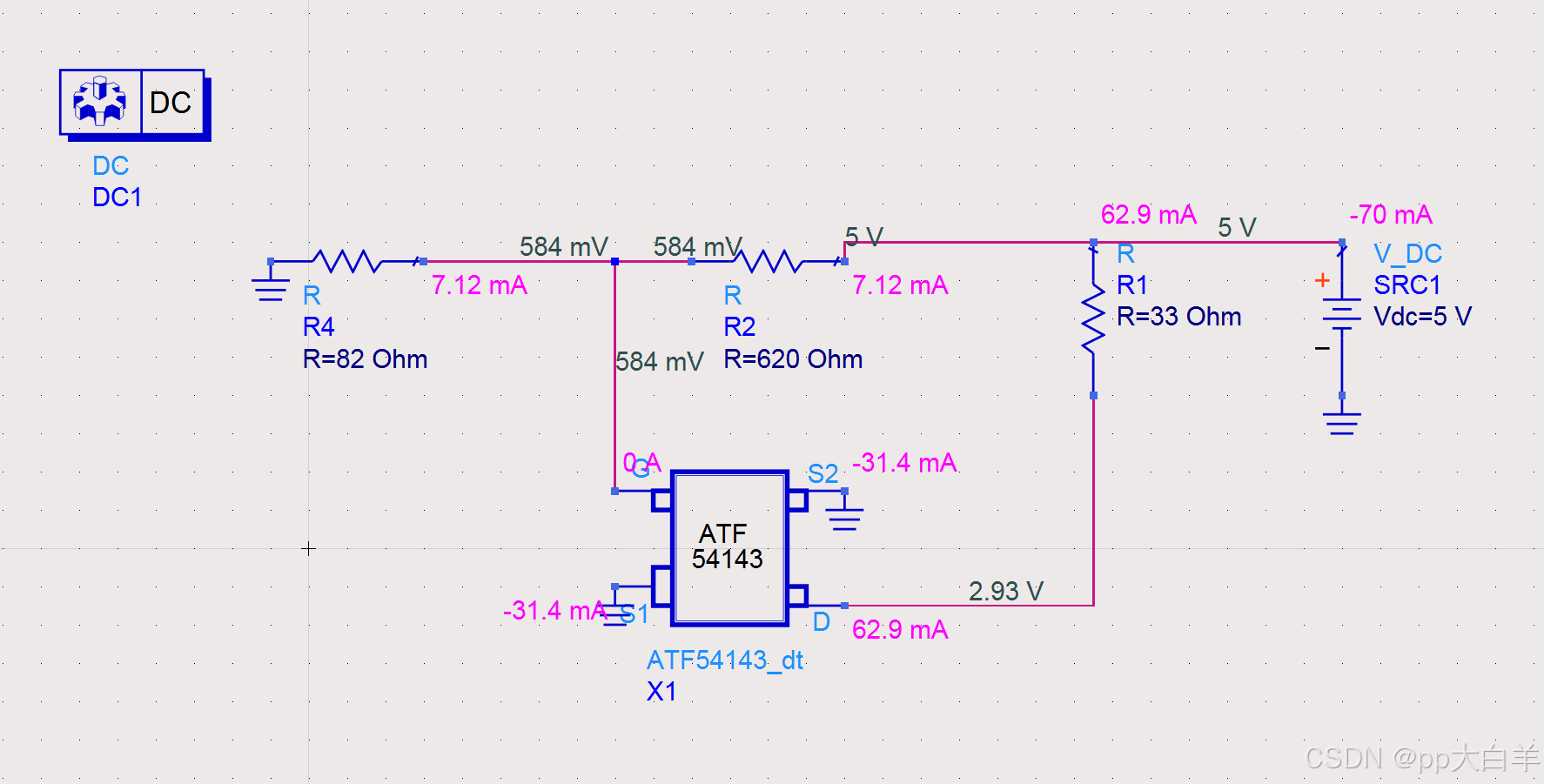

新建原理圖改成實際電路?

求解最大資用增益和K?

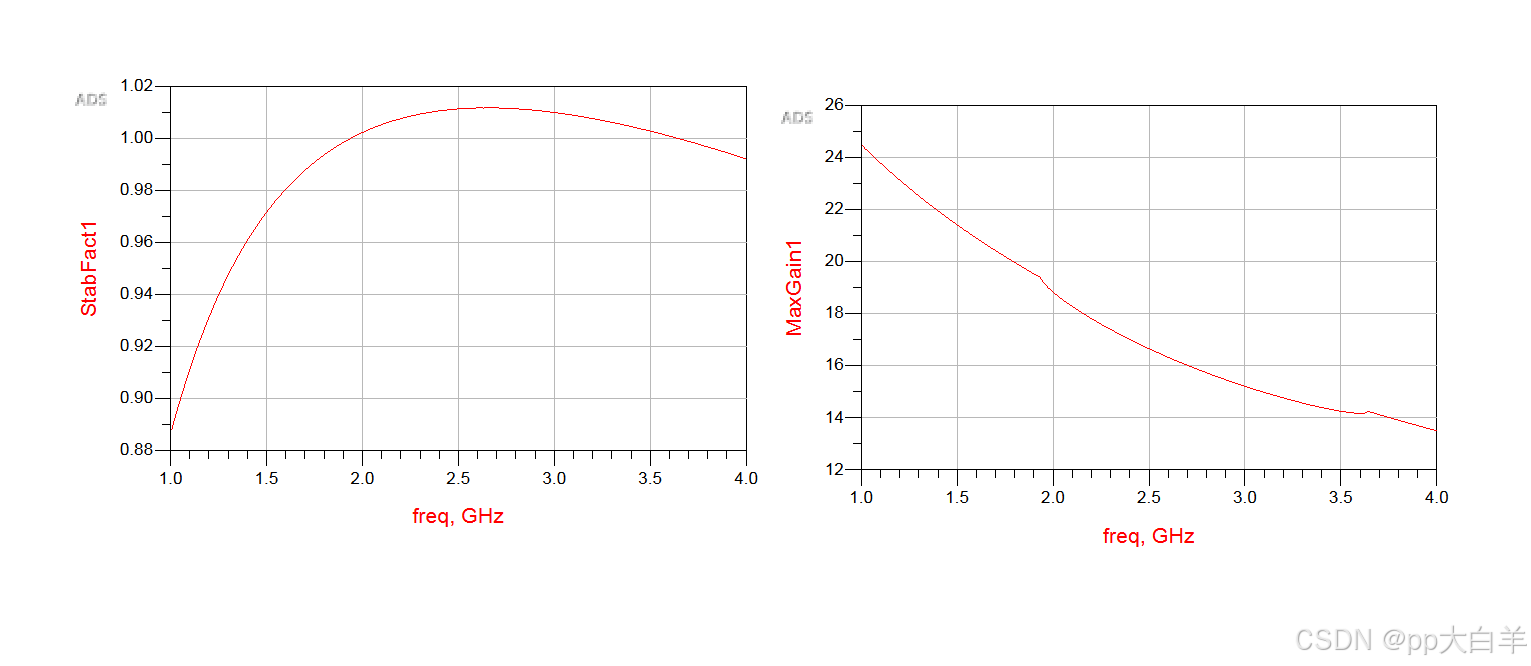

是否滿足Gain>15dB、K>1

隔交流電感:避免交流信號影響直流偏置

隔直流電容:避免交流信號影響直流信號?

K不滿足,要么修改電路增加負反饋,要么修改晶體管

?在源極串聯電感(微帶線電感)改善K值

?在源極串聯電感(微帶線電感)改善K值

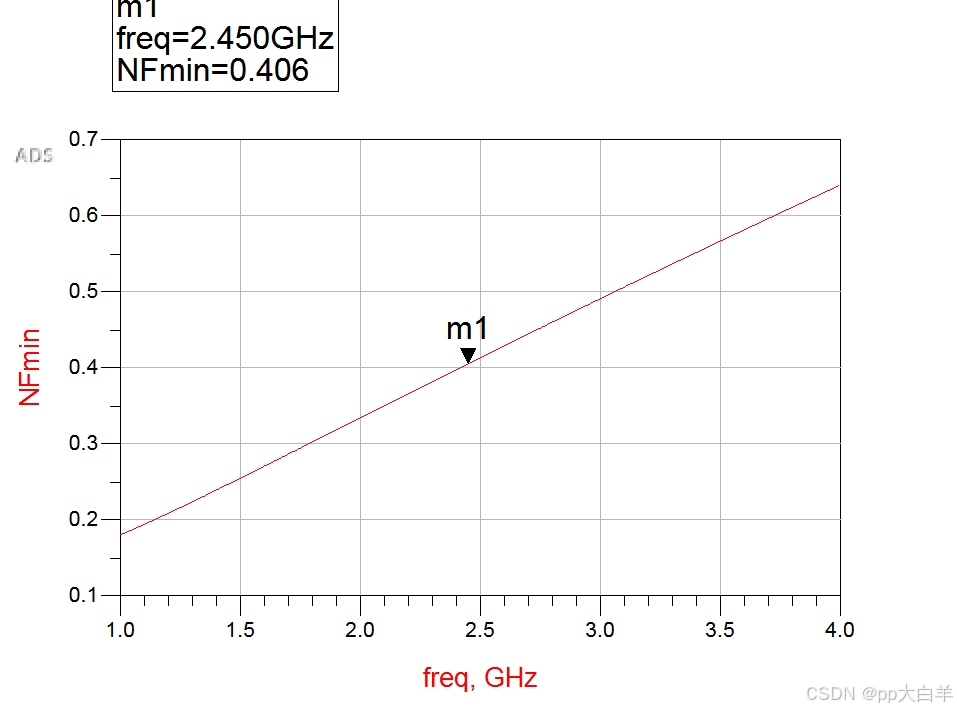

?求解噪聲系數(理想噪聲)

?求解噪聲系數(理想噪聲)

通過做匹配使實際噪聲無限靠近理想噪聲

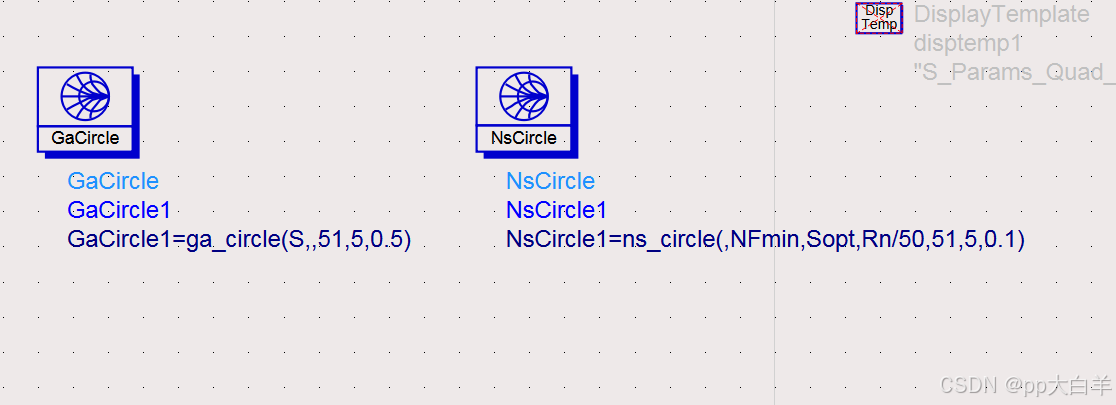

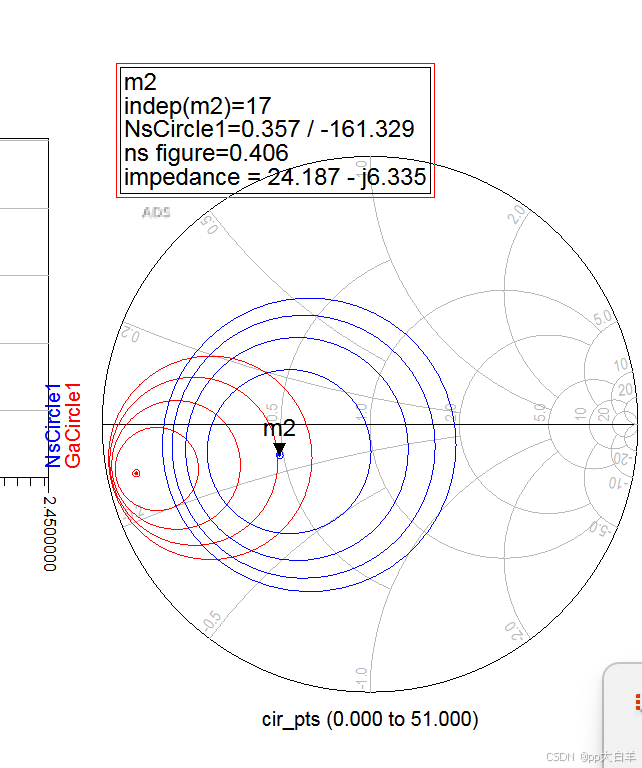

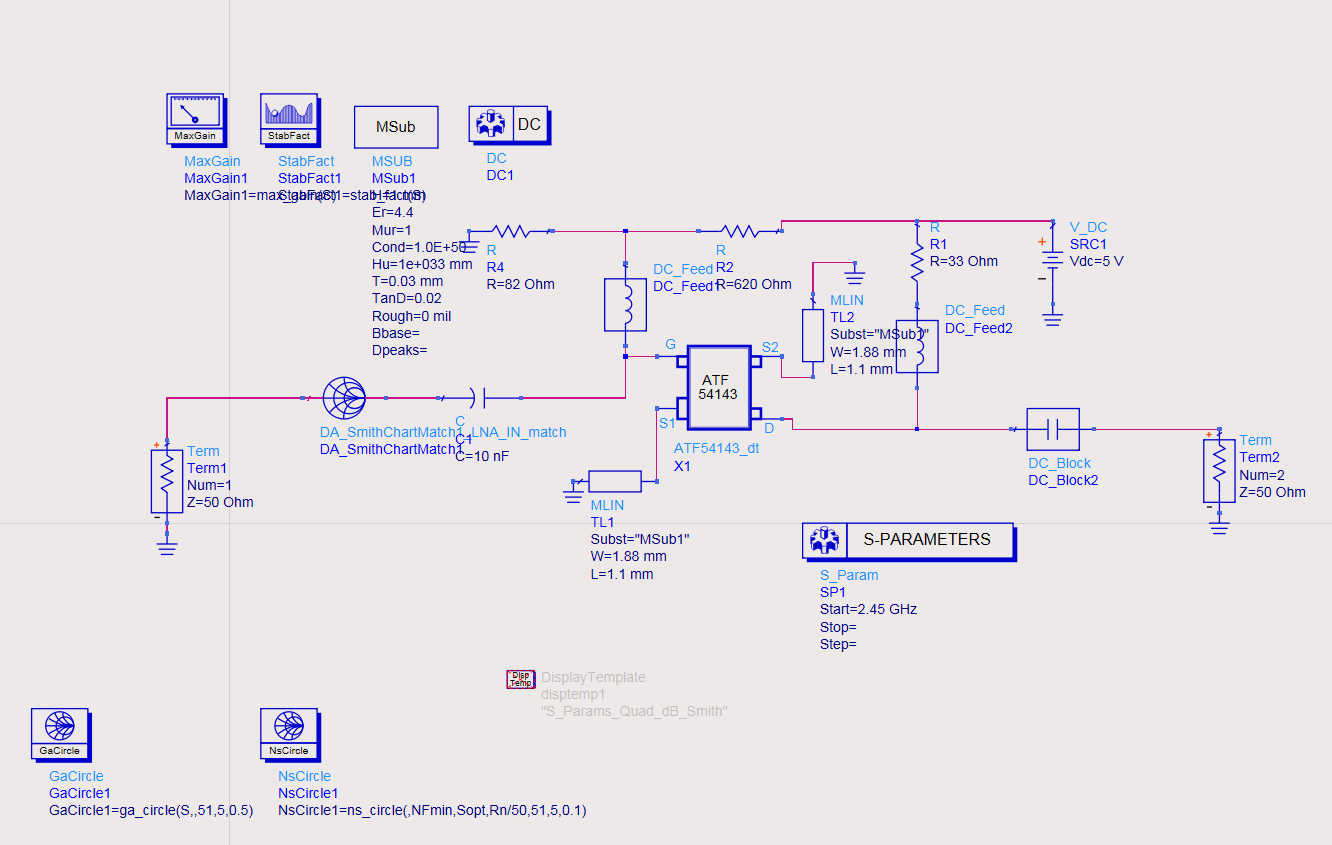

繪制等增益圓和等噪聲系數圓?

選擇M2作為匹配點?

需要把 24.187-j6.335匹配到50Ω(直接用smith工具匹配)

?

?

輸出端也要匹配?

結果:

?

)

RNNoise 基于遞歸神經網絡的噪聲抑制庫)