加法器

框架,首先介紹原理,然后引入一位加法器最后再引入多位加法器最后引入帶符號的加法器

這一節涉及到的硬件電路的知識理解就好,實在看不懂就跳過,但是封裝以后的功能必須看懂。

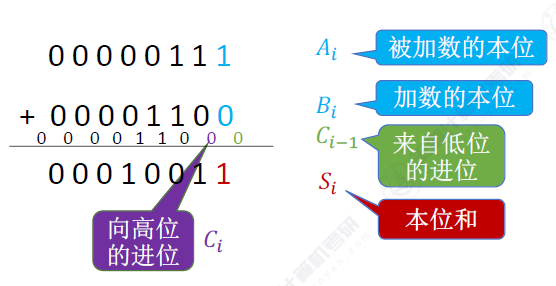

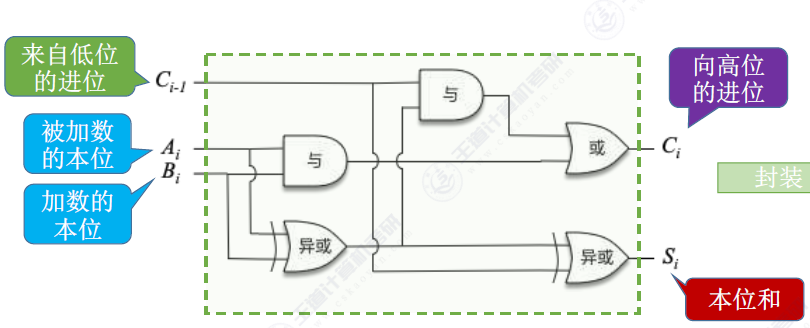

這是一個一般的加法過程涉及到的必要元素圖中已經給出,加數與被加數的本位以及相加以后的本為和,低位的進位和高位的進位

主要就是上面這五部分,首先對于加數與被加數的本位以及低位的進位是輸入的內容我們不需要管

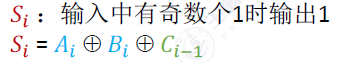

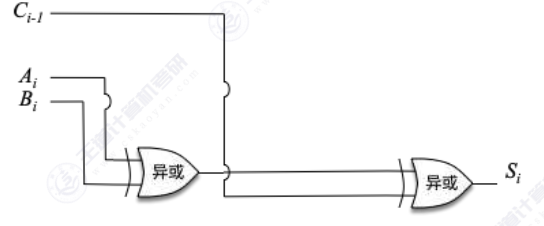

接下來我們看本為和,因為二進制加法滿二進一的特性使得我們可以采用異或來算本位和。 。可以采用 下面的電路來實現

。可以采用 下面的電路來實現

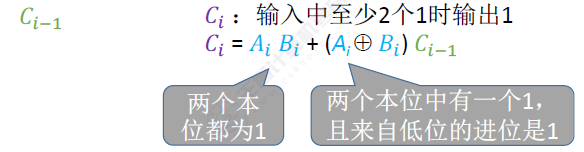

對于向高位的進位來說需要考慮的元素就比較多了。需要考慮加數被加數低位的進位這三個因素,同時結合二進制數的加法規則來看。

高位的進位有以下圖片的情形,圖片中采用了或運算來求值,或運算的法則全0為0

第一部分采用與運算當兩個都為1時才為1

第二部分先用AB異或(同0異1)再與地位進位相與

滿足任意一部分進位為1

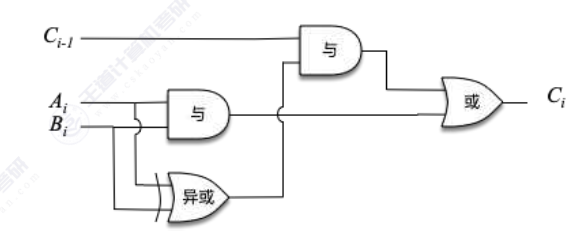

電路表示如下圖

最后結合一下電路圖

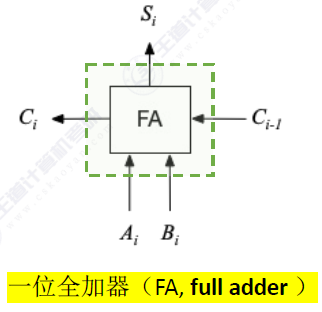

再封裝一下

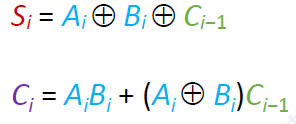

需要記住一下邏輯表達式

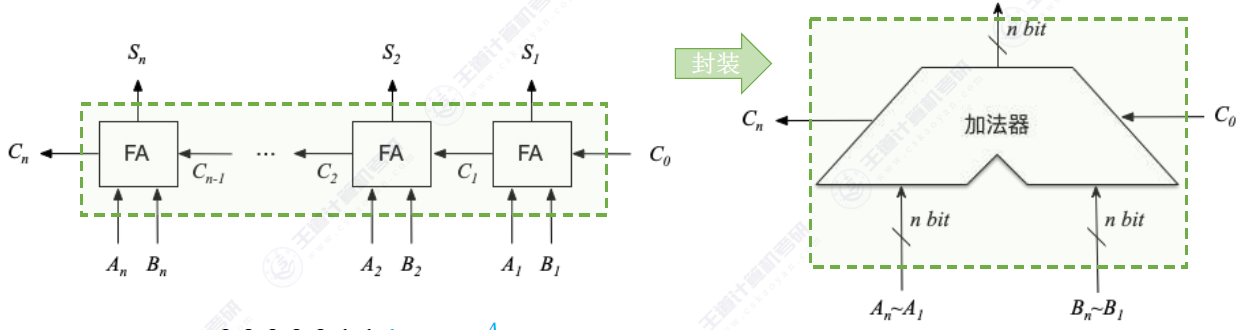

把n 個一位全加器串接起來,就可進行兩個n bit數的相加。

但是由于 可知每一位的高位進位都依賴于低位的信號產出這就使得需要等待低位的運算結束才能進行高位的運算,這樣的操作我們理解為串行操作,與之對應的時并行操作(需要CLA部件)。并行的加法器稍后講解。

可知每一位的高位進位都依賴于低位的信號產出這就使得需要等待低位的運算結束才能進行高位的運算,這樣的操作我們理解為串行操作,與之對應的時并行操作(需要CLA部件)。并行的加法器稍后講解。

這里需要知道串行的加法器速率較慢

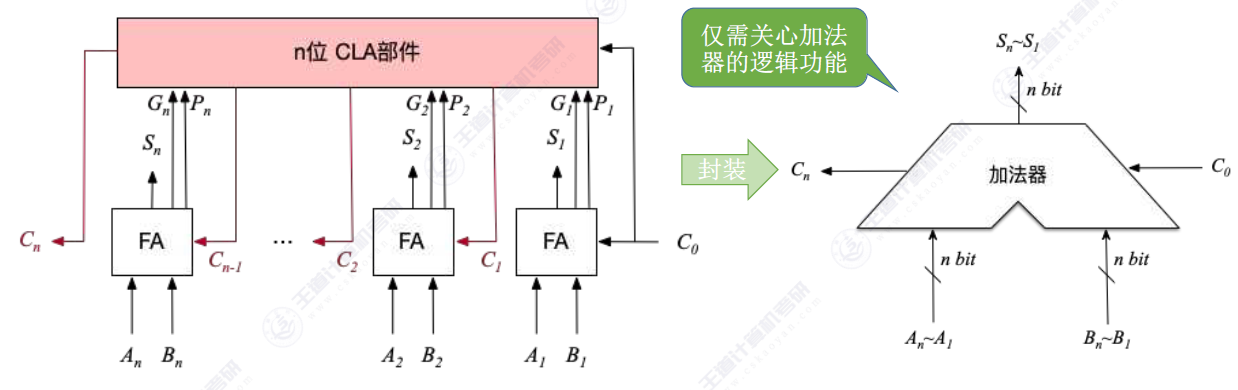

下圖是并行進位的加法器

多出的CLA部件可以并行的計算出高位的進位但是電路較為復雜。一般就擴展到4位。

接下來我們的目光放到帶標志位的加法器

為什么要帶標志位?一般帶哪些標志位?

首先解釋為什么要帶標志位?帶標志位可以很快的得出此次加法的相關信息例如是否溢出是否借位運算結果的正負性。

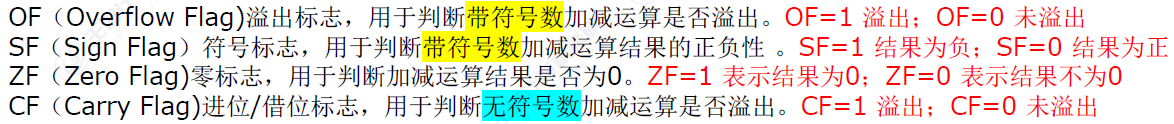

一般帶下面四個標志位

of溢出? ? 1溢出0未溢出

sf符號標志? ?1負0正

zf零標志位? 1為零 0不為零

cf無符號溢出? 1溢出 0 未溢出

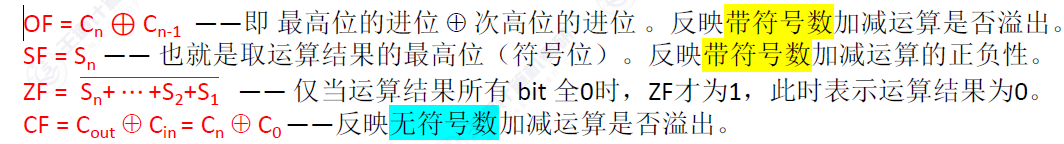

接下來介紹一下這幾個常見標志位的運算邏輯表達式

有關于OF CF后面會詳細講解,這里解釋一下sf它只需要取計算的最高位即可 zf需要采用或非電路,當全部為都為0時或電路輸出0然后再非就輸出1此時zf=1表示運算結果為0.

接下來介紹一下并位加法器

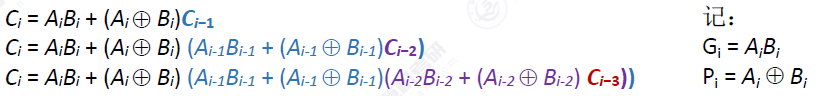

前面介紹過本為和采用異或來計算![]()

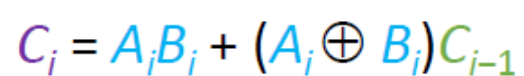

而高位的進位![]() 采用AB先與,或上AB異或與上低位進位,這里包括了進位的兩種情況,本位都為1相加后需要進位,以及AB其中一個為1但是低位進位為1相加后也要進位。或者當AB都為0時不進位。

采用AB先與,或上AB異或與上低位進位,這里包括了進位的兩種情況,本位都為1相加后需要進位,以及AB其中一個為1但是低位進位為1相加后也要進位。或者當AB都為0時不進位。

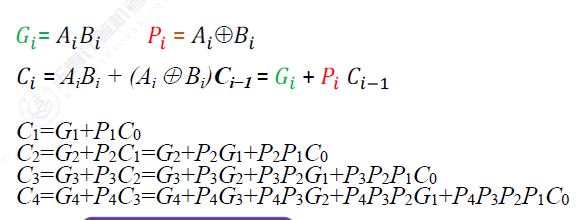

這里時串行進位加法器,我們可以采用一個電器電路CLA一下得出所有的進位然后直接就可以進行并行的加法計算

具體的邏輯推導如下

注意這里的每一個算術表達式都需要一個電路來實現,所以說就不太方便進行更深層次的套娃因為這樣會非常耗費硬件。對應計算機成本也更高。

一般最多采取4為的CLA加法器。

算術邏輯單元ALU

主要了解其功能,

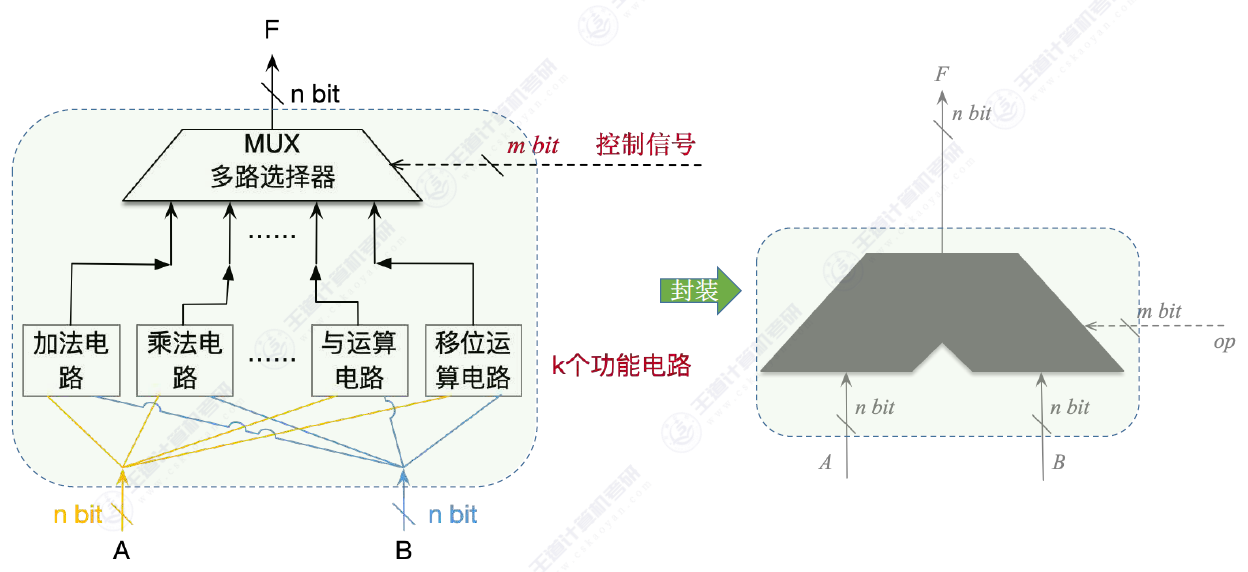

其實ALU更像是一個集合體加一個多路選擇器

他這里里面所包含的操作一般都有其對印的電路或者代替電路,就比如前面所說的加法器

就如圖所示它封裝了好多功能在里面對外只暴露出少量的引腳。

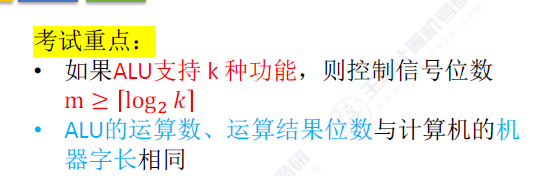

其中最重要的一個考點就是多路選擇器的位數,他需要曼滿足對應的操作類型。

再有就是前面提到的幾個常見的標志位

OF有符號溢出位? 1表示溢出?

SF正負標志位 1表示負

ZF零標志位 1表示結果為0? 采用了或非門

CF 無符號溢出位 1表示溢出

)

)

:雪崩防護+分布式事務)