目錄

- 1、前言

- 工程概述

- 免責聲明

- 2、相關方案推薦

- 我已有的所有工程源碼總目錄----方便你快速找到自己喜歡的項目

- 我這里已有的 MIPI 編解碼方案

- 3、設計思路框架

- 工程設計原理框圖

- FPGA內部彩條

- RGB數據位寬轉換

- RGB數據緩存

- MIPI-DSI協議層編碼

- MIPI-DPHY物理層串化

- MIPI-LVDS顯示屏

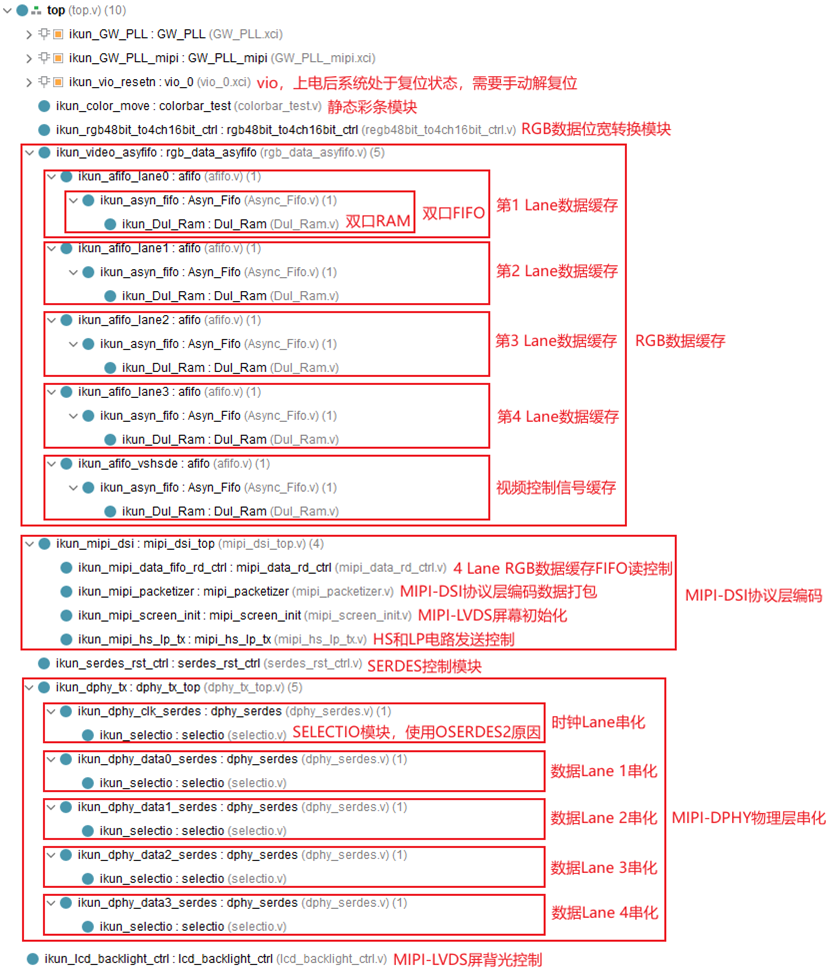

- 工程源碼架構

- 4、工程源碼1詳解:Kintex7-325T版本

- 5、工程移植說明

- vivado版本不一致處理

- FPGA型號不一致處理

- 其他注意事項

- 6、上板調試驗證并演示

- 準備工作

- VIO解復位

- MIPI-DSI視頻編碼輸出演示

- 7、工程源碼獲取

FPGA純verilog實現MIPI-DSI視頻編碼輸出,提供工程源碼和技術支持

1、前言

FPGA實現MIPI視頻編碼現狀:

MIPI視頻編碼分為DSI和D-PHY兩大部分,其中D-PHY屬于物理層,依托硬件,靈活性不高,方案不多;DSI屬于協議層,依托代碼,靈活性很高,方案很多;所以只要實現了D-PHY,MIPI-DSI解碼其實就很靈活了;第一種D-PHY方案是使用FPGA內部資源實現,該方案優點是設計簡單,缺點是硬件成本較高;第二種是使用專用的D-PHY芯片,比如MC20901,該方案優點是設計簡單,缺點是硬件成本較高;本設計使用Xilinx系列FPGA純verilog代碼實現MIPI-DSI視頻編碼輸出;

工程概述

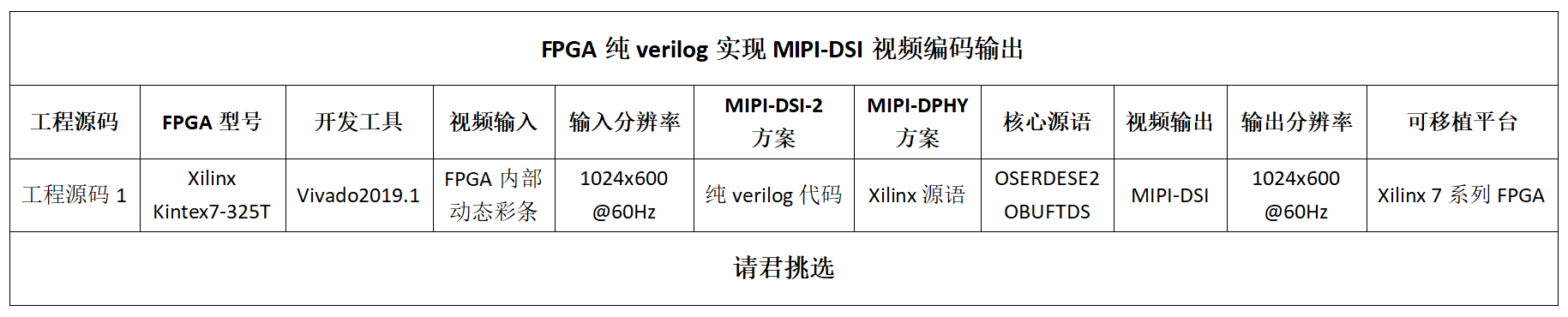

本設計使用Xilinx 7系列FPGA純verilog代碼實現MIPI-DSI視頻編碼輸出;首先FPGA內部生成1個1024x600的靜態彩條視頻作為輸入源,彩條視頻為Native接口;然后彩條視頻送入視頻位寬轉換模塊實現位寬轉換功能,將輸入的24bit像素數據轉換為4路16bit像素數據,以便于后續模塊生成4 Lane MIPI數據;然后4 Lane視頻送入異步FIFO緩存模塊,以實現數據跨時鐘域轉換;然后4 Lane視頻送入MIPI-DSI協議層編碼模塊,按照DSI協議將輸入的RGB視頻進行編碼處理,然后輸出HS電路數據和LP電路數據;然后MIPI-DSI數據送入MIPI-DPHY物理層串化模塊,將輸入的4 Lane并行MIPI-DSI數據串化為4 Lane高速串行的差分信號,模塊依托Xilinx官方的OSERDESE2和OBUFTDS實現串化和單端轉差分處理;中途還要對MIPI-LVDS顯示屏做初始化操作;最后MIPI-DSI編碼視頻直接送MIPI-LVDS顯示屏顯示即可;針對市場主流需求,本設計提供1套vivado工程源碼,具體如下:

現對上述1套工程源碼做如下解釋,方便讀者理解:

工程源碼1

開發板FPGA型號為高云Kintex7-325T-xc7k325tffg900-2;首先FPGA內部生成1個1024x600的靜態彩條視頻作為輸入源,彩條視頻為Native接口;然后彩條視頻送入視頻位寬轉換模塊實現位寬轉換功能,將輸入的24bit像素數據轉換為4路16bit像素數據,以便于后續模塊生成4 Lane MIPI數據;然后4 Lane視頻送入異步FIFO緩存模塊,以實現數據跨時鐘域轉換;然后4 Lane視頻送入MIPI-DSI協議層編碼模塊,按照DSI協議將輸入的RGB視頻進行編碼處理,然后輸出HS電路數據和LP電路數據;然后MIPI-DSI數據送入MIPI-DPHY物理層串化模塊,將輸入的4 Lane并行MIPI-DSI數據串化為4 Lane高速串行的差分信號,模塊依托Xilinx官方的OSERDESE2和OBUFTDS實現串化和單端轉差分處理;中途還要對MIPI-LVDS顯示屏做初始化操作;最后MIPI-DSI編碼視頻直接送MIPI-LVDS顯示屏顯示即可,輸出分辨率為1024x600@60Hz,MIPI-4 Lane;本工程適用于Xilinx 7系列FPGA實現MIPI-DSI視頻編碼輸出應用;

本文詳細描述了FPGA純verilog實現MIPI-DSI視頻編碼輸出的設計方案,工程代碼可綜合編譯上板調試,可直接項目移植,適用于在校學生、研究生項目開發,也適用于在職工程師做學習提升,可應用于醫療、軍工等行業的高速接口或圖像處理領域;

提供完整的、跑通的工程源碼和技術支持;

工程源碼和技術支持的獲取方式放在了文章末尾,請耐心看到最后;

免責聲明

本工程及其源碼即有自己寫的一部分,也有網絡公開渠道獲取的一部分(包括CSDN、Xilinx官網、Altera官網以及其他開源免費獲取渠道等等),若大佬們覺得有所冒犯,請私信批評教育;部分模塊源碼轉載自上述網絡,版權歸原作者所有,如有侵權請聯系我們刪除;基于此,本工程及其源碼僅限于讀者或粉絲個人學習和研究,禁止用于商業用途,若由于讀者或粉絲自身原因用于商業用途所導致的法律問題,與本博客及博主無關,請謹慎使用。。。

2、相關方案推薦

我已有的所有工程源碼總目錄----方便你快速找到自己喜歡的項目

其實一直有朋友反饋,說我的博客文章太多了,亂花漸欲迷人,自己看得一頭霧水,不方便快速定位找到自己想要的項目,所以本博文置頂,列出我目前已有的所有項目,并給出總目錄,每個項目的文章鏈接,當然,本博文實時更新。。。以下是博客地址:

點擊直接前往

我這里已有的 MIPI 編解碼方案

我這里目前已有豐富的基于FPGA的MIPI編解碼方案,主要是MIPI解碼的,既有純vhdl實現的MIPI解碼,也有調用Xilinx官方IP實現的MIPI解碼,既有2line的MIPI解碼,也有4line的MIPI解碼,既有4K分辨率的MIPI解碼,也有小到720P分辨率的MIPI解碼,既有基于Xilinx平臺FPGA的MIPI解碼也有基于Altera平臺FPGA的MIPI解碼,還有基于Lattice平臺FPGA的MIPI解碼,后續還將繼續推出更過國產FPGA的MIPI解碼方案,畢竟目前國產化方案才是未來主流,后續也將推出更多MIPI編碼的DSI方案,努力將FPGA的MIPI編解碼方案做成白菜價。。。

基于此,我專門建了一個MIPI編解碼的專欄,并將MIPI編解碼的博客都放到了專欄里整理,對FPGA編解碼MIPI有項目需求或學習興趣的兄弟可以去我的專欄看看,專欄地址如下:

點擊直接前往專欄

3、設計思路框架

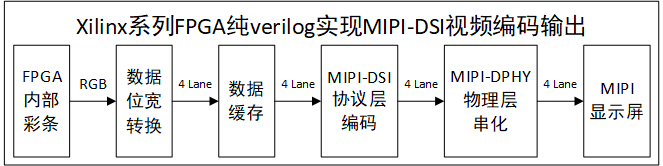

工程設計原理框圖

工程設計原理框圖如下:

FPGA內部彩條

首先FPGA內部生成1個1024x600@60Hz的靜態彩條視頻作為輸入源,彩條視頻為Native接口,即常規的行同步信號、場同步信號、數據有效信號、像素數據等;FPGA內部彩條設計為4階白、藍、綠、紅色彩條,如下:

FPGA內部彩條代碼架構如下:

RGB數據位寬轉換

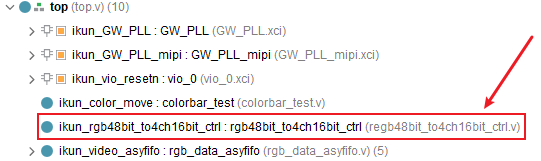

然后彩條視頻送入視頻位寬轉換模塊實現位寬轉換功能,將輸入的24bit像素數據轉換為4路16bit像素數據,以便于后續模塊生成4 Lane MIPI數據;需要注意的是,24bit的彩條視頻需要拓展至48bit,直接將單路的24bit RGB數據復制為2路即可;RGB數據位寬轉換代碼架構如下:

RGB數據緩存

然后4 Lane視頻送入異步FIFO緩存模塊,以實現數據跨時鐘域轉換;數據緩存使用純verilog代碼實現的異步FIFO實現;RGB數據緩存代碼架構如下:

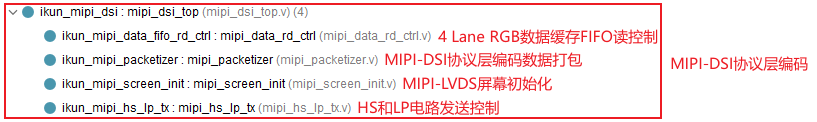

MIPI-DSI協議層編碼

然后4 Lane視頻送入異步FIFO緩存模塊,以實現數據跨時鐘域轉換;然后4 Lane視頻送入MIPI-DSI協議層編碼模塊,按照DSI協議將輸入的RGB視頻進行編碼處理,然后輸出HS電路數據和LP電路數據;MIPI-DSI協議層編碼代碼架構如下:

MIPI-DPHY物理層串化

然后MIPI-DSI數據送入MIPI-DPHY物理層串化模塊,將輸入的4 Lane并行MIPI-DSI數據串化為4 Lane高速串行的差分信號,模塊依托Xilinx官方的OSERDESE2和OBUFTDS實現串化和單端轉差分處理;MIPI-DPHY物理層串化代碼架構如下:

MIPI-LVDS顯示屏

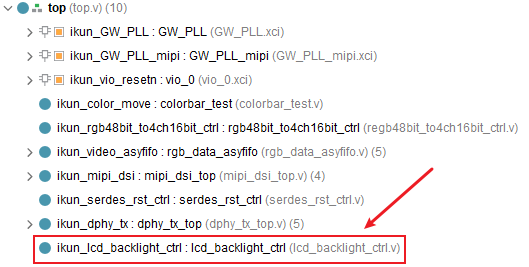

MIPI-LVDS顯示屏分辨率為1024x600@60Hz;需要對MIPI-LVDS顯示屏做初始化操作和背光控制,背光控制代碼例化如下:

最后MIPI-DSI編碼視頻直接送MIPI-LVDS顯示屏顯示即可;MIPI-LVDS顯示屏實物如下:

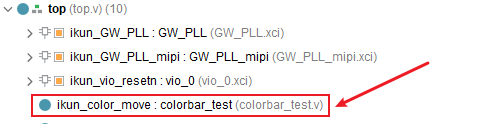

工程源碼架構

工程源碼架構如下:

4、工程源碼1詳解:Kintex7-325T版本

開發板FPGA型號:Kintex7-325T-xc7k325tffg900-2;

FPGA開發環境:Vivado2019.1;

輸入:FPGA內部彩條,分辨率1024x600@60Hz;

輸出:MIPI,分辨率1024x600@60Hz,4 Lane模式;

MIPI-DSI2-TX方案:純verilog代碼方案;

MIPI-D-PHY方案:純verilog代碼方案,OSERDESE2原語;

工程源碼架構請參考前面第3章節中的《工程源碼架構》小節;

工程作用:此工程目的是讓讀者掌握Xilinx系列FPGA純verilog實現MIPI-DSI視頻編碼輸出的設計能力,以便能夠移植和設計自己的項目;

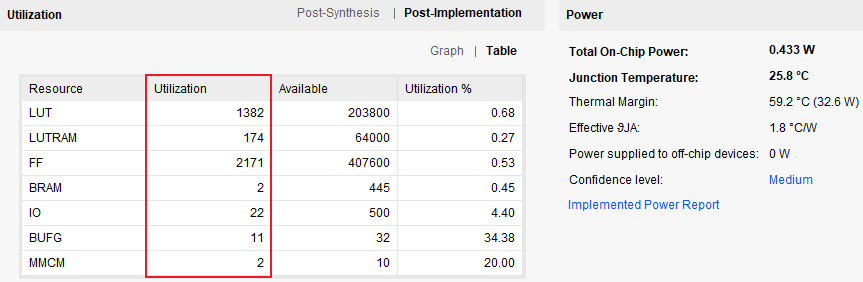

工程的資源消耗和功耗如下:

5、工程移植說明

vivado版本不一致處理

1:如果你的vivado版本與本工程vivado版本一致,則直接打開工程;

2:如果你的vivado版本低于本工程vivado版本,則需要打開工程后,點擊文件–>另存為;但此方法并不保險,最保險的方法是將你的vivado版本升級到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解決如下:

打開工程后會發現IP都被鎖住了,如下:

此時需要升級IP,操作如下:

FPGA型號不一致處理

如果你的FPGA型號與我的不一致,則需要更改FPGA型號,操作如下:

更改FPGA型號后還需要升級IP,升級IP的方法前面已經講述了;

其他注意事項

1:由于每個板子的DDR不一定完全一樣,所以MIG IP需要根據你自己的原理圖進行配置,甚至可以直接刪掉我這里原工程的MIG并重新添加IP,重新配置;

2:根據你自己的原理圖修改引腳約束,在xdc文件中修改即可;

3:純FPGA移植到Zynq需要在工程中添加zynq軟核;

6、上板調試驗證并演示

準備工作

FPGA開發板,推薦使用本博的開發板;

MIPI-LVDS顯示屏;

開發板連接如下:

開發板上電后下載bit即可測試;

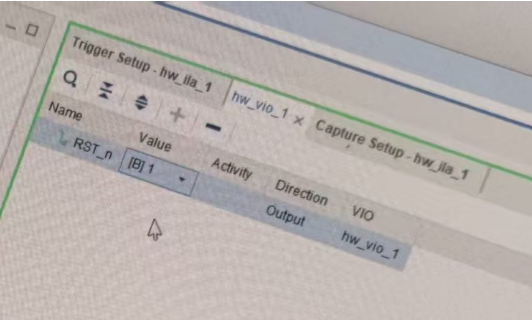

VIO解復位

由于上電后系統由VIO控制處于復位狀態下,所以需要操作VIO進行解復位,如下:

即需要手動將RST_n設置為1;

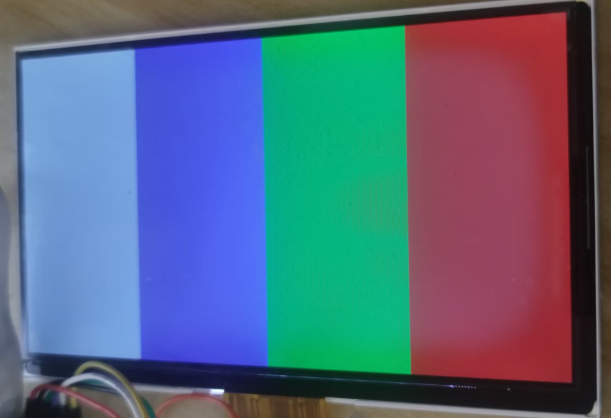

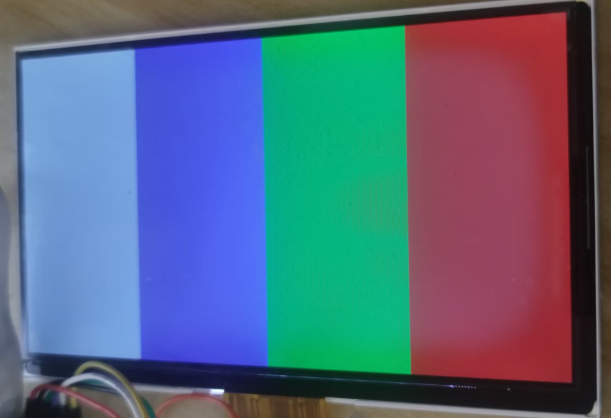

MIPI-DSI視頻編碼輸出演示

MIPI-DSI視頻編碼輸出如下:

MIPI-TX原始

7、工程源碼獲取

代碼太大,無法郵箱發送,以某度網盤鏈接方式發送,

資料獲取方式:私,或者文章末尾的V名片。

網盤資料如下:

此外,有很多朋友給本博主提了很多意見和建議,希望能豐富服務內容和選項,因為不同朋友的需求不一樣,所以本博主還提供以下服務:

)

:STUN服務和TURN服務的作用)

)