?

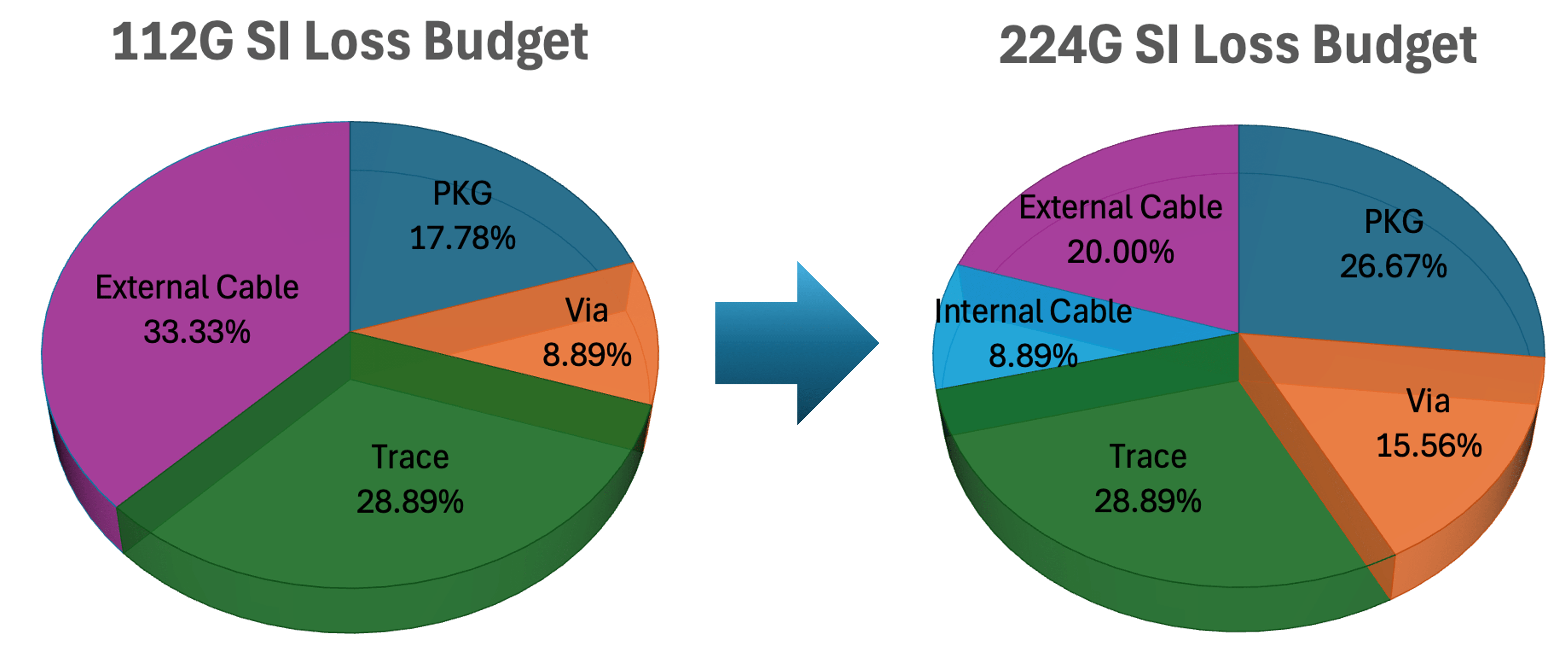

在AI驅動的時代,系統設計已經從單一PCB的視角,逐步轉向以整個rack為單位來考量。 對于信號完整性而言,焦點以不再局限于單一PCB上的損耗,而是擴展到芯片與芯片之間的端到端互連損耗(end-to-end interconnect loss)。 這種轉變反映了現代高性能系統設計的新需求與挑戰,也讓互連損耗成為設計者無法忽視的核心課題。

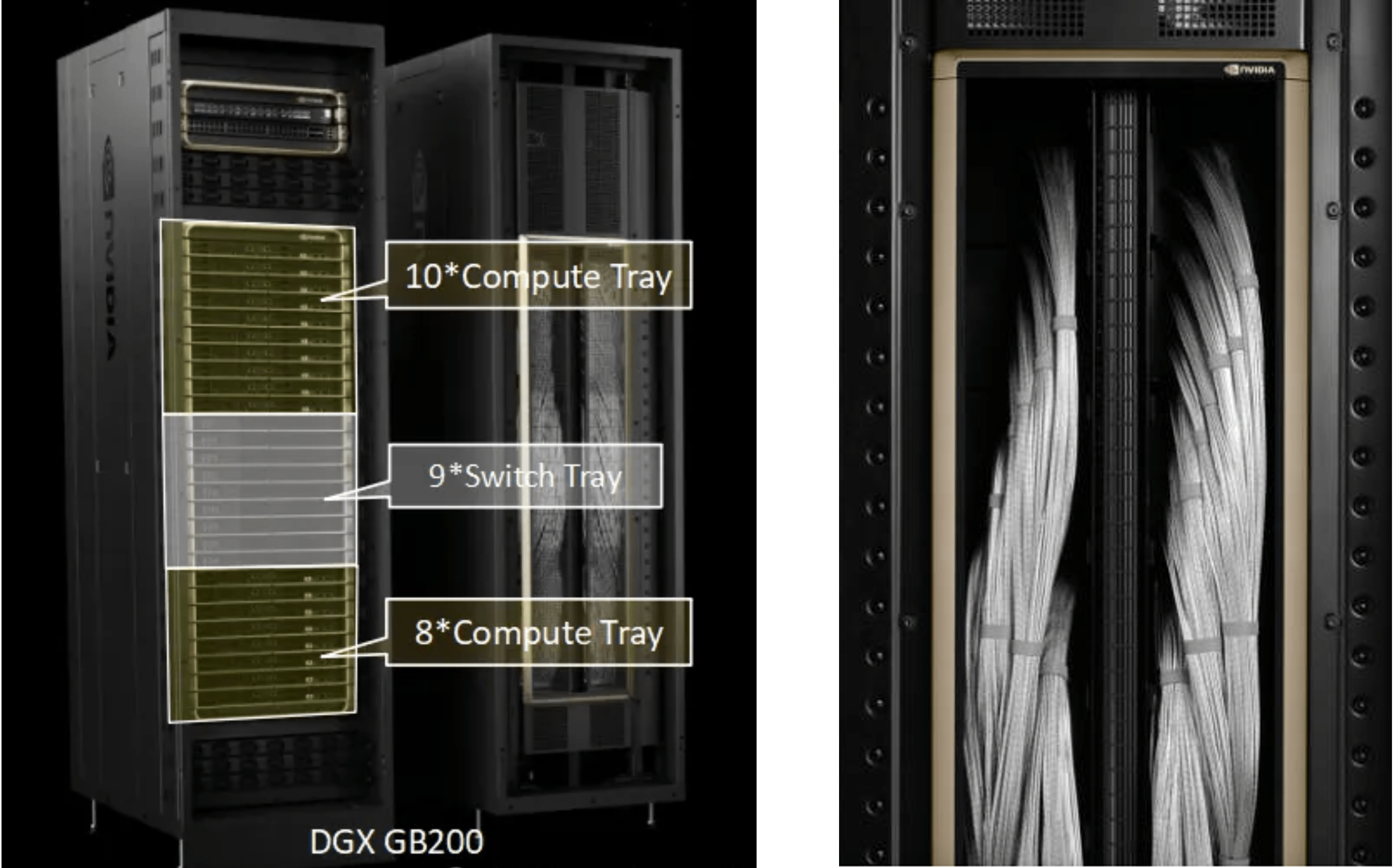

比如最近大家一直在關注的GB200,Compute Tray即透過Cable Cartridge與Switch Tray高速連通,這種End-End loss(Blackwell to NVswitch)大概落在40~45dB,也是目前SerDes做Equalization的上限。

?

晶片到芯片的互連損耗可以細分為以下三個主要部分,每一部分都對整體系統性能產生重要影響:

1. 封裝載板與PCB損耗

載板與PCB損耗這部分是整體訊號互連損耗的重要組成,主要包括以下幾個方面:

金屬損耗

金屬損耗主要分成金屬(通常是銅)本身的電阻效應以及表面粗糙度!

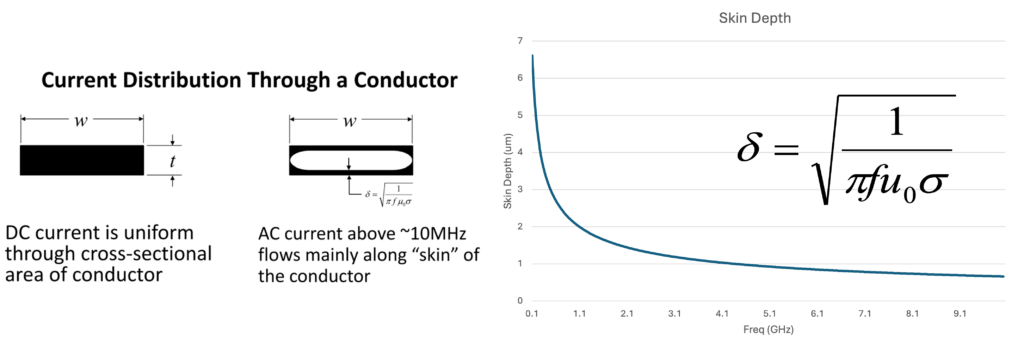

銅箔電阻損耗

PCB上絕大多數的金屬是銅,本身就帶有些許電阻,低頻時電流較為平均分布在銅箔內部,損耗較小; 高頻時會有集膚效應,電流會分布在銅箔表面,電流截面積下降,導致高頻電阻升高的情況下高頻時損耗會上升。

?

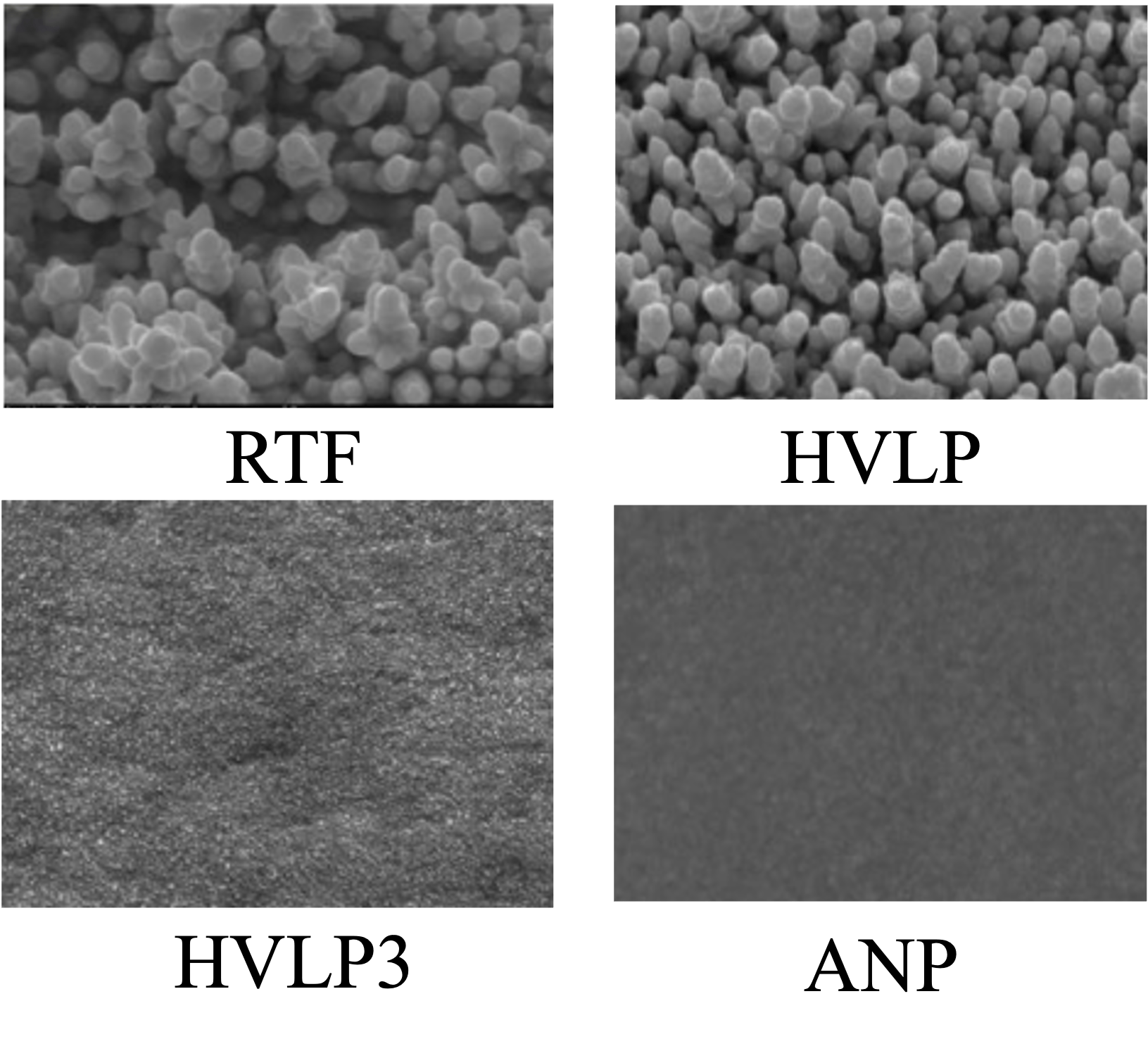

表面粗糙度

再加上PCB銅箔的表面不會是一個完整的平面,微觀來講可以看到些許的顆粒,銅箔的這些顆粒會增加其與樹脂的表面接觸面積,使其結合強度變高,銅皮會較不易脫落,不過在高頻時的損耗會急劇增加!

?

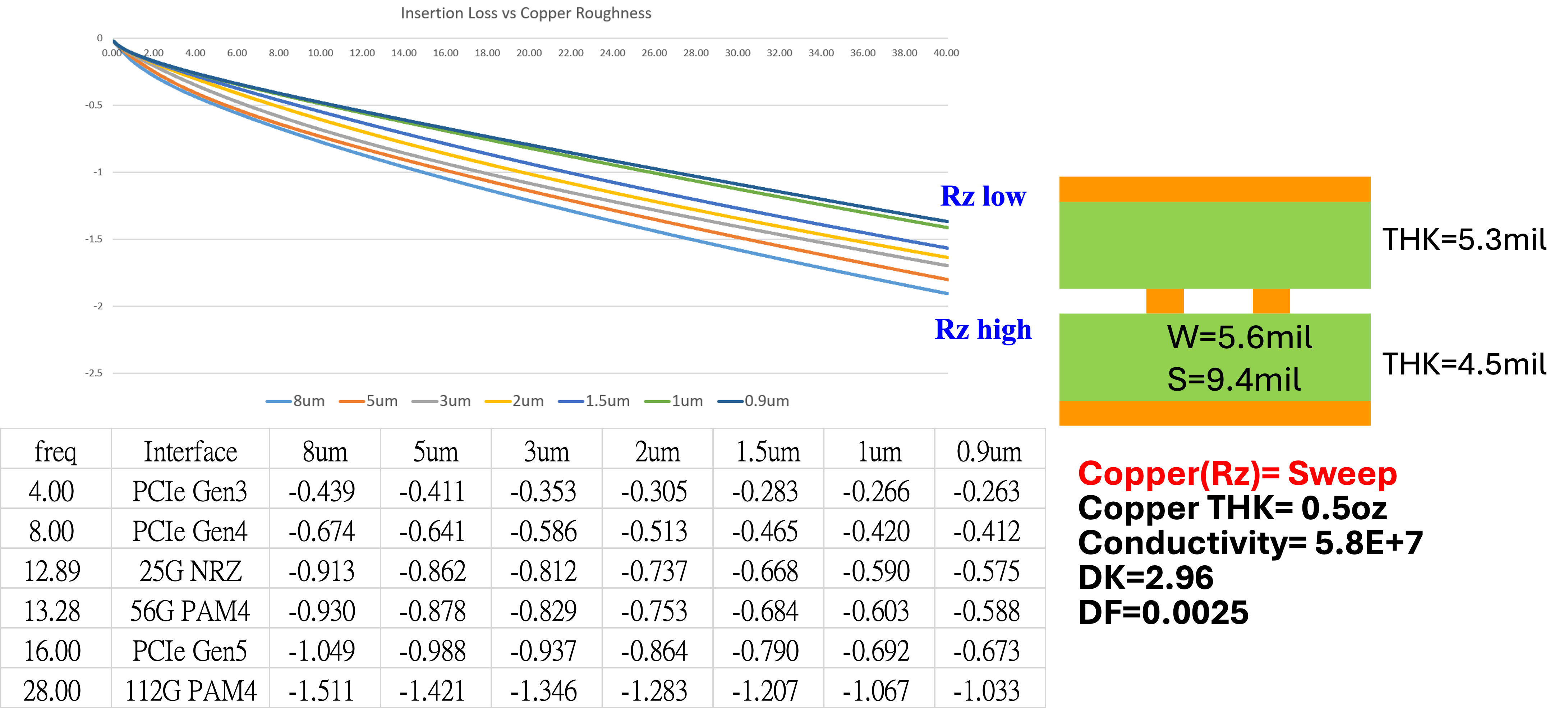

透過改善銅皮的表面粗糙的行為,可以改善表面粗糙度,通常以Ra或是Rz呈現,對SI工程師而言,我們較常關心的是Rz。 而依不同銅皮的表現又分成不同等級,其中有RTF(Reverse Treated Foil)、VLP(Very Low-Profile)、HVLP(Highly Very Low-Profile)、ANP(Any No-Profile)等等。

目前產業界最高檔的銅箔是HVLP5,幾乎已經是沒有任何的Rz,可以將表面粗糙度降低許多! 不過CCL與PCB廠還在努力克服沒有顆粒的銅箔對于材料拉力(Peeling)的影響,預計今年(Y2025)會有好消息。

?

?

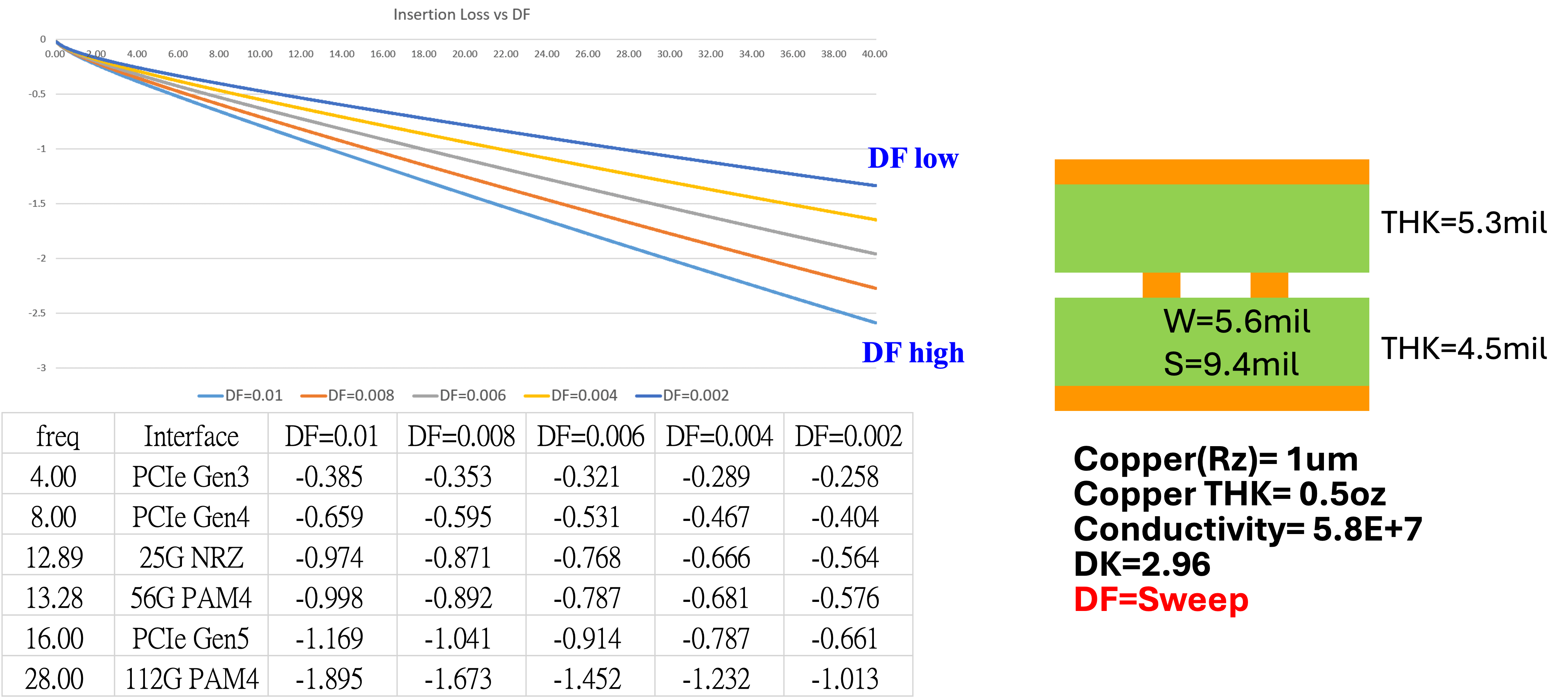

介質損耗

PCB介質有所謂的損耗正切參數(Loss Tangent)或是所謂DF(Dissipation Factor),這兩者指的是同一件事,代表材料在高頻信號通過時,會有多少能量損耗(消耗成熱能等)。

從電磁學的角度,介電材料會有「實部 \( \mathrm{Re}(\varepsilon) \)」與「虛部 \( \mathrm{Im}(\varepsilon) \)」的介電常數:

??實部代表電場儲存能量的能力;

??虛部代表材料吸收并轉換這些能量的損耗能力。

而 DF可以寫成:

tan(δ)≈Im(ε)Re(ε)

這里 \( \delta \) 是介電損耗角。 數值越大,表示「虛部」在整個介電常數所占比重越高,也就是介質損耗越顯著。

來個比喻:我們可以將介質損耗則可以比擬為水流過程中管壁吸收能量、造成水流衰減的效果。 若管壁很粗糙、吸水量大(損耗大),水流一路過去就會衰減得很厲害; 反之,若管壁光滑且不吸水(損耗小),水能保有更多原本的流量與壓力。

?

輻射損耗

將輸出信號電壓扣除信號的反射與系統內的損耗后,剩余的能量可以視為輻射信號。 輻射訊號實際上是一種損耗,因為這些能量會直接散布到環境中。 然而,從系統SI的角度來看,我們通常不特別關注這部分損耗。 原因在于,只要系統的阻抗設計得當,輻射能量通常會被控制在非常小的范圍內,對整體性能的影響可以忽略不計。

\( \text{Radiation Loss} \; =\; 1 \; -\; |S_{11}|^2 \; -\; |S_{21}|^2 \)

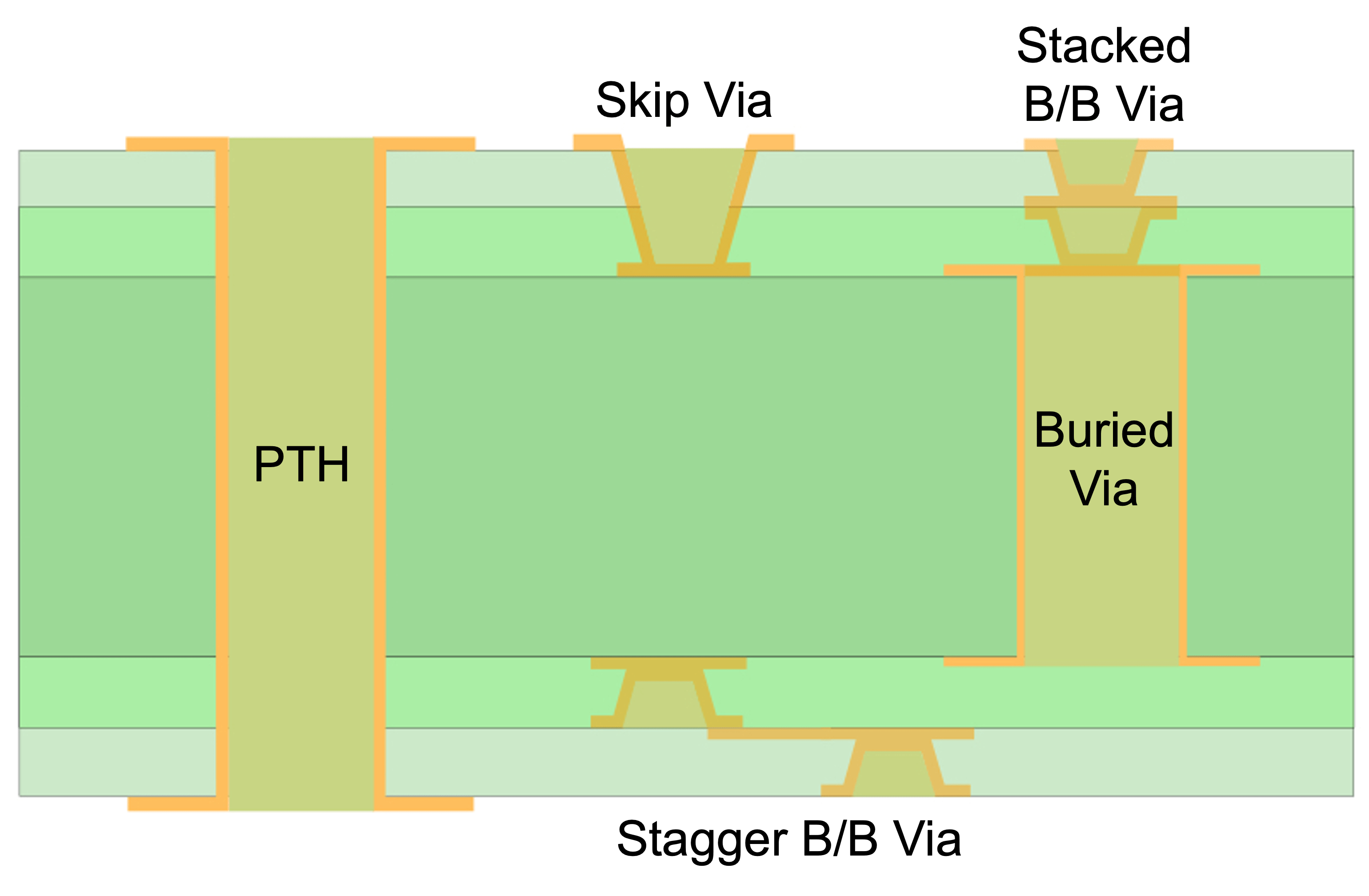

鍍穿孔與雷射孔

在PCB設計中,我們習慣將互連(Interconnect)分為2D與3D走線兩類。?2D走線通常指的是傳輸線,這些線路可以使用2D軟件進行高效的模型化,例如 Keysight ADS 的 CILD 模塊或常見的 Polar 軟件,都能很好地處理這類結構。 而3D結構則包括鍍穿孔(Plating Through Hole, PTH)與激光孔(Laser Via),這些結構需要借助3D電磁場模擬軟件來建模,如 Cadence 的 Clarity 或 Ansys 的 HFSS。 相較于2D軟件,3D模擬的分析時間更長,對技術要求也更高,并且需要較長的學習與建模周期,才能確保模型與軟件設定的準確性。

?

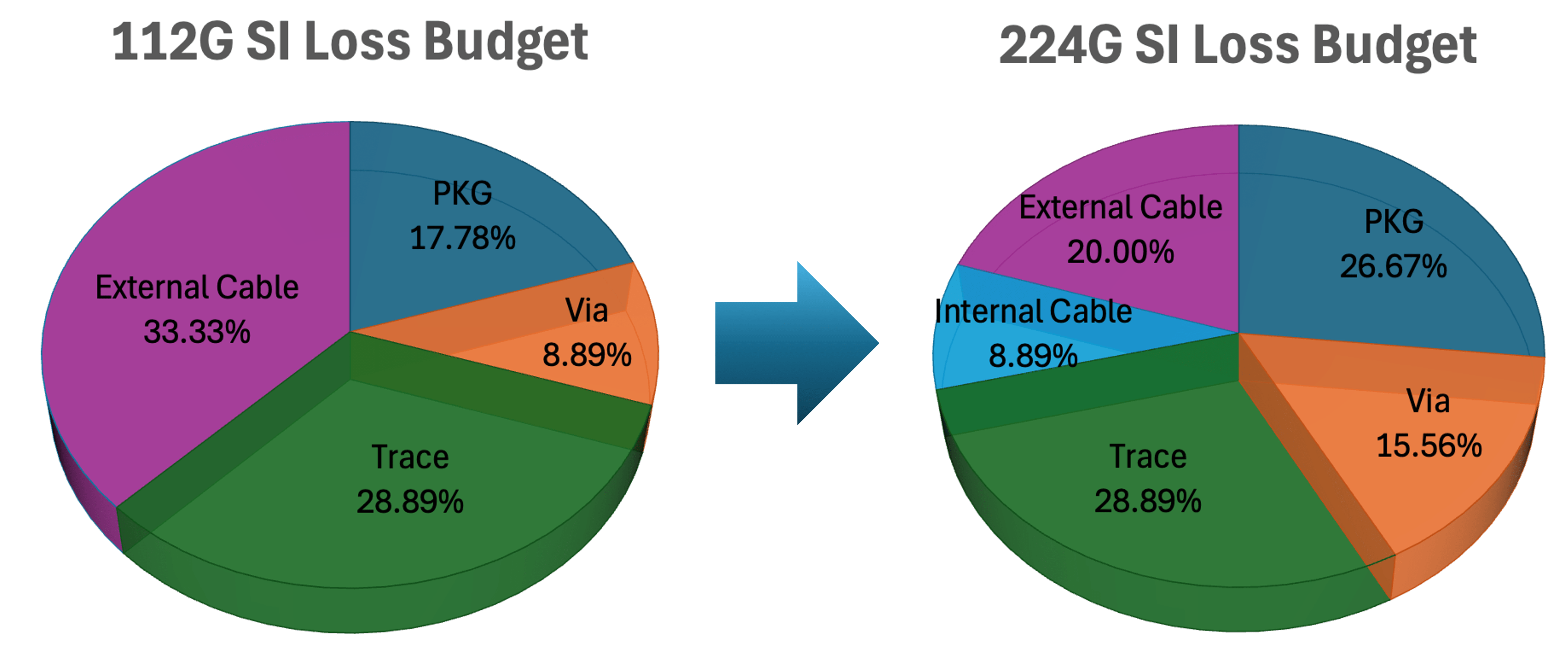

隨著產業邁向?224G-PAM4?的時代,Via 已成為設計中無法忽略的關鍵因素。 由于服務器或交換機主板的厚度不斷增加(目前厚度即將超過6mm),Via的長度也隨之變長。 同時,頻率已攀升至53GHz,在這樣的條件下,單一Via的損耗可能高達1.5dB至2dB,所有Via的損耗就占掉了整個通道損耗的15%左右。 更為關鍵的是,在目前PCB材料升級受限的情況下,Via所帶來的損耗顯得格外突出,對整體通道性能的影響不容忽視。 (P.S. 所有Cable損耗均包含與其連接的Connector損耗)

?

2. 連接器損耗

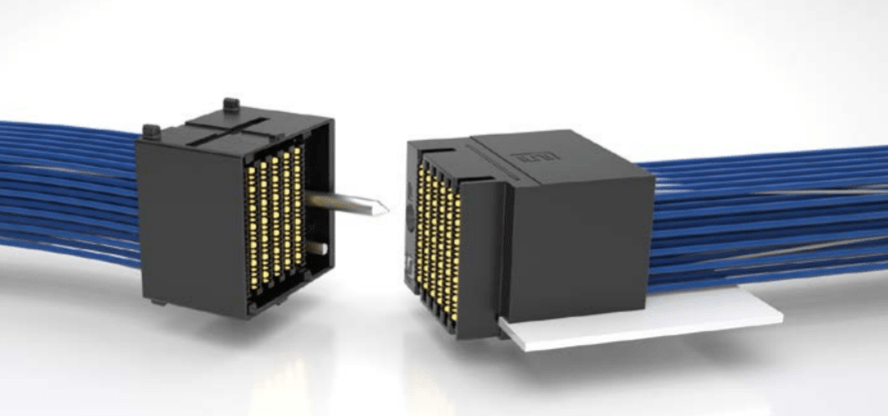

開頭已經提到,現今的AI system是不同機柜間的連結,訊號路徑上會有許多的連接器,例如GB200的Compute Tray對外就有一個Backplane連接器跟Cable cartridge對接,再利用銅纜線接到Switch Tray。 (圖為Samtec的Backplane連接器,或稱BP Connector)

?

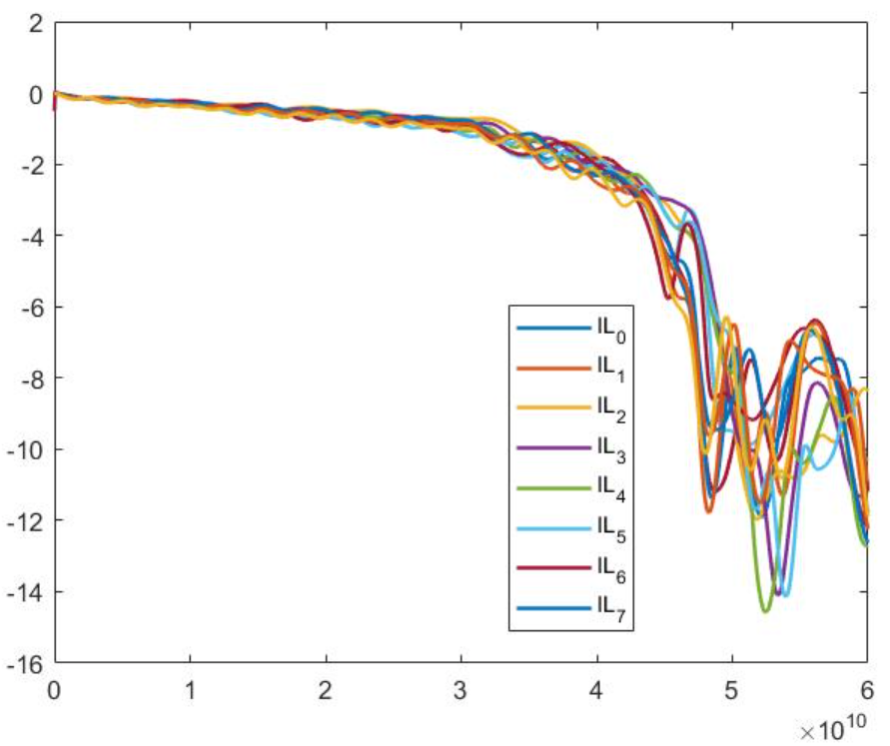

這些連接器是3D的架構,設計上很仰賴3D建模的技術,且與PCB via類似,缺乏完整的reference plane,因此連接器的高頻特性不容易控制,從圖可以看到高頻損耗抖動的非常嚴重! 最好的做法就是做的精小,可是會遇到機械結構較為薄弱,焊接或是組裝不良的議題,相當不好搞!

?

3. 銅纜損耗

以現在的AI system來說,這部分又分成兩種

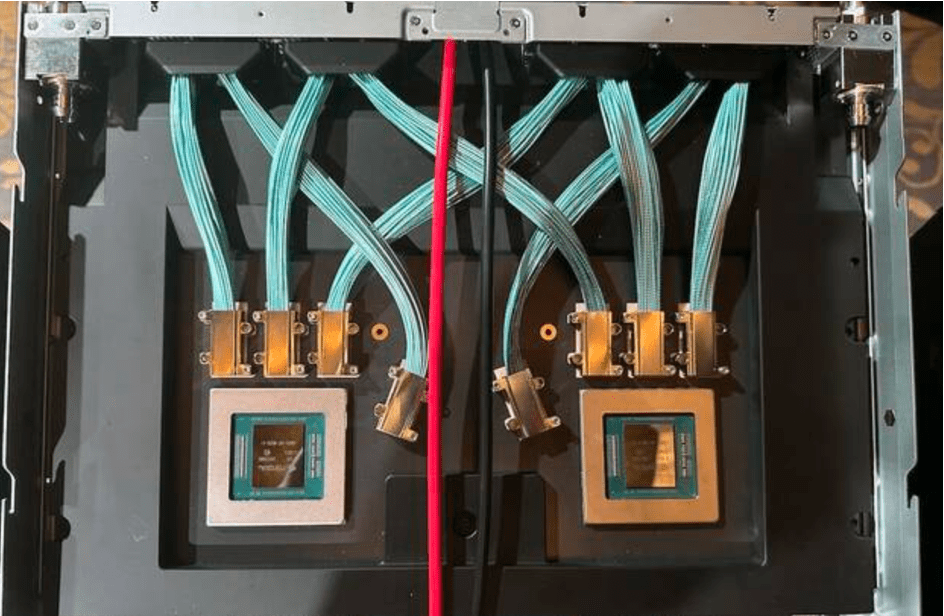

- 內部飛線(Internal Flyover Cable):例如GB200的Switch Tray內部即是用這種Amphenol的飛線。

?

- 外部系統間連接(External Cable):例如交換機網絡對連需要用到的DAC cable(Direct-Access Cable)或是類似GB200 Compute Tray與Switch Tray外部的Cable,都是屬于這類型的外部連接媒介。

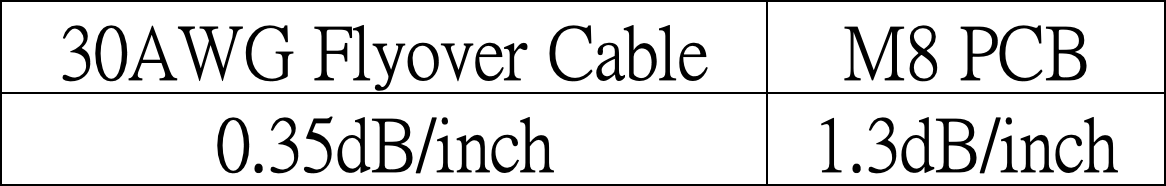

因為Cable具有穩定的阻抗特性、良好的reference path以及較低的材料DF,所以比PCB CCL材料的損耗還來的小很多。 對比M8等級的材料來看(例如臺光電的EM892K+HVLP4銅箔),在224G-PAM4的應用上,30AWG的Cable的損耗大約是0.35dB/inch而PCB的損耗大約是1.3dB/inch,兩者差別極大!

?

然而沒有這么美好的事情,有好就有壞,用Cable會有幾個Trade-off:

- 成本較高:Cable本身就已經很貴了,還需要加上連接Cable的連接器的成本,所以使用內部 Cable的機臺成本都較高。

- 散熱問題:因為需要內部連接器組裝Cable,這些連接器會有一定的高度(通常20mm),這會影響內部的風流,使得ASIC或是GPU的散熱效果變差。 當然如果走水冷(Liquid Cooling),可能是比較沒差?

?

- 組裝與維修:多了內部連接器,對于系統組裝一定會有所影響,畢竟多了一道工序。 且這種連接器為了做在內部,會比較精小,所以機械強度比較弱,很容易掉件,且維修時整臺機臺都需要開蓋檢查,較為麻煩!

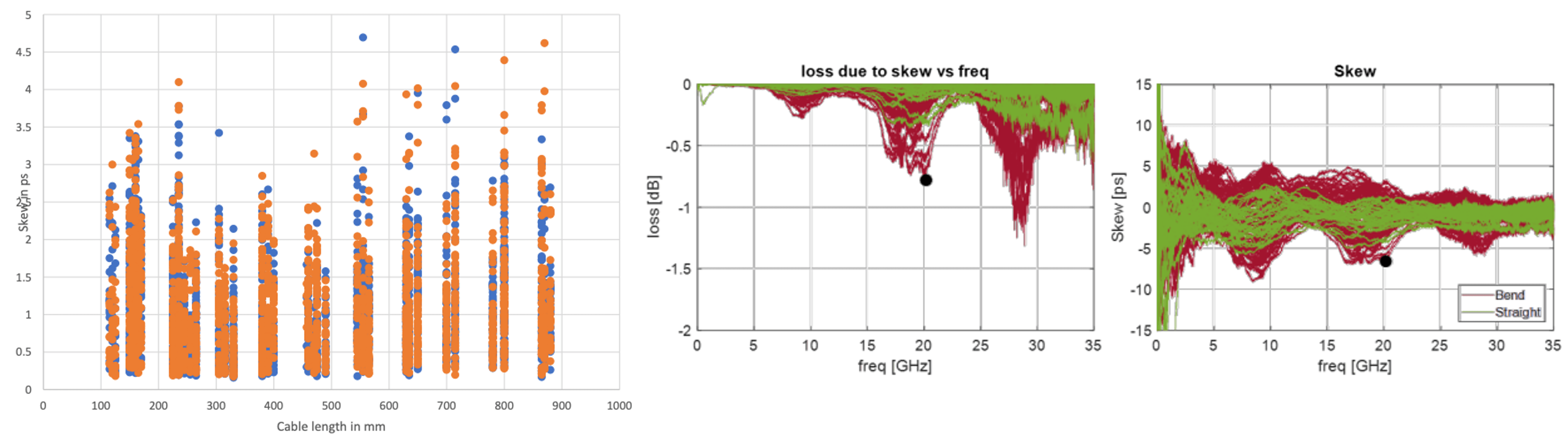

- 模態轉換損耗:Cable結構的不均勻性(P/N Skew)會引發額外的模態轉換損耗(Mode Conversion Loss),這個損耗隨著數據傳輸速度越來越快而越難被忽視,這不只牽扯到Cable本身制造上的穩定度,還得分析當Cable轉折時是否會影響到差動對兩條線的均勻性, 抑或是Cable與Connector在焊接過程中的不匹配性,相當地復雜!

?

總結

隨著數據傳輸速度不斷提升,對損耗的要求也越來越嚴苛,訊號完整性的重要性日益凸顯! 這不僅僅是對SI工程師的專業要求,從業人士也需要具備基礎的理解能力。 無論是如何解讀供應商提供的損耗規格,還是熟悉零組件的技術迭代,這些都成為不可或缺的能力。 此外,能夠憑借專業知識提出針對性問題,例如詢問Cable的P/N Skew等被設計「包裝」的細節,也是未來工作的核心能力之一。

未來,我們將有機會逐一剖析如何有效控制與設計這些損耗,敬請期待!

?

題解)

)

![[吾愛出品] 網文提取精靈_4.0](http://pic.xiahunao.cn/[吾愛出品] 網文提取精靈_4.0)

![[面試]SoC驗證工程師面試常見問題(三)](http://pic.xiahunao.cn/[面試]SoC驗證工程師面試常見問題(三))