ACM9238 高速雙通道ADC模塊自助服務手冊AD9238

一、實驗目的

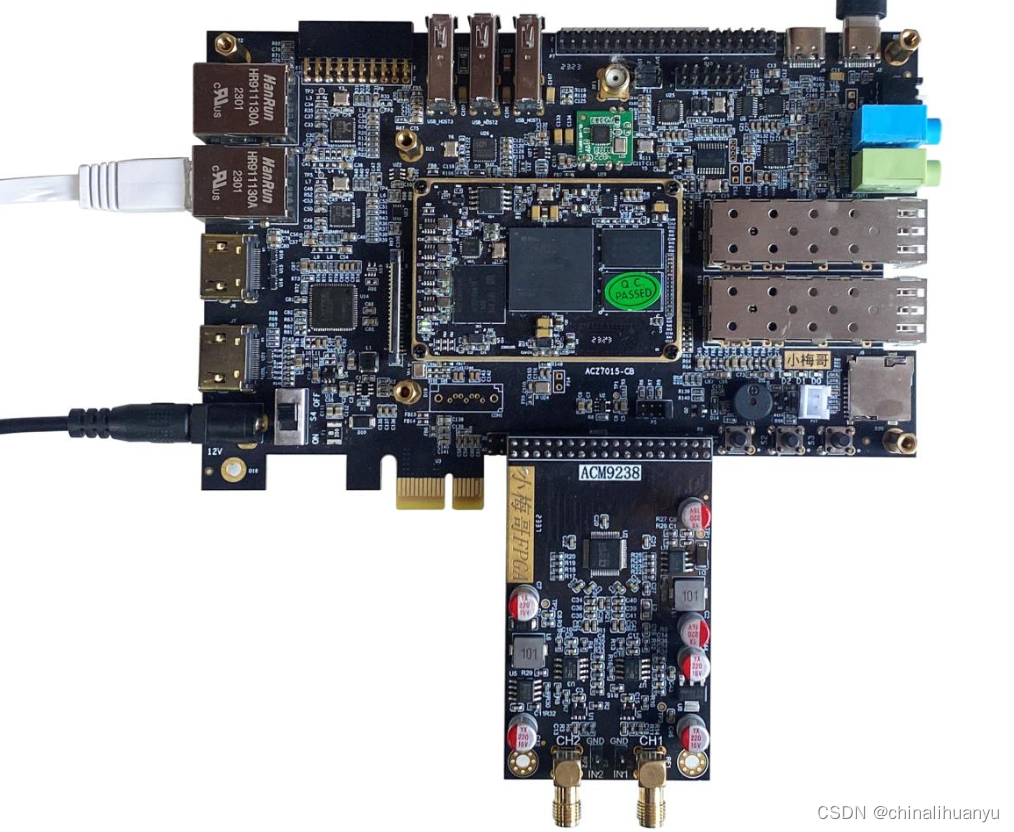

本次實驗通過電腦上的網絡調試助手,將命令幀進行發送,然后通過ACZ7015開發板上的以太網芯片接收,隨后將接收到的數據轉換成命令,從而實現對ACM9238模塊采樣頻率、數據采樣個數以及采樣通道的配置。配置完成之后,ACM9238模塊開始采集數據,將采集的數據存儲至ddr中,然后通過網口以UDP協議傳輸到電腦。用戶可以在電腦上通過網口調試工具進行指令的下發,并以文件的形式保存接收到的數據,然后使用MATLAB軟件進行進一步的數據處理分析。

二、AD9238

模塊在各方面參數性能上與AD9226保持一致。但是在設計上優化了信號調理電路,將單端信號先轉成差分信號,再送入ADC轉換,已獲得更小的采樣誤差。

功能參數

1、±5V電壓輸入范圍

2、每通道65Msps最高采樣速率

3、每通道12位輸出

三、DDR3(大容量存儲器件)

DDR=Double Data Rate雙倍速率,DDR SDRAM=雙倍速率同步動態隨機存儲器,人們習慣稱為DDR,其中,SDRAM 是Synchronous Dynamic Random Access Memory的縮寫,即同步動態隨機存取存儲器。而DDR SDRAM是Double Data Rate SDRAM的縮寫,是雙倍速率同步動態隨機存儲器。(摘錄:ddr(雙倍數據速率)_百度百科 (baidu.com))

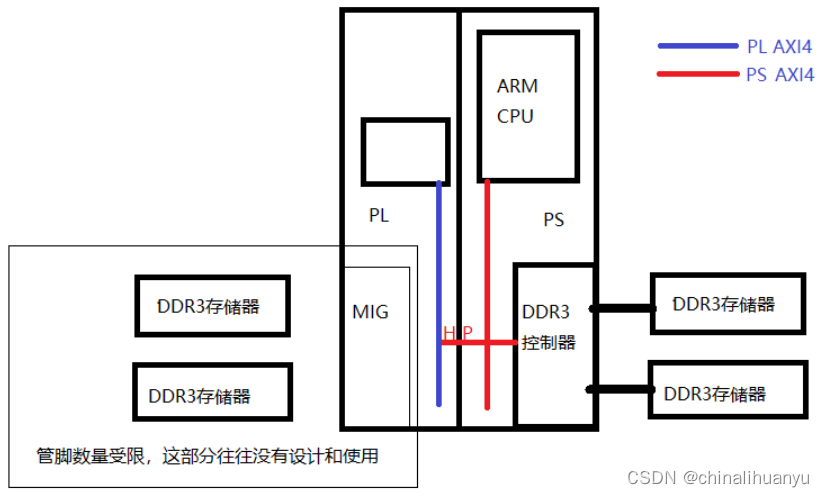

1.相關知識

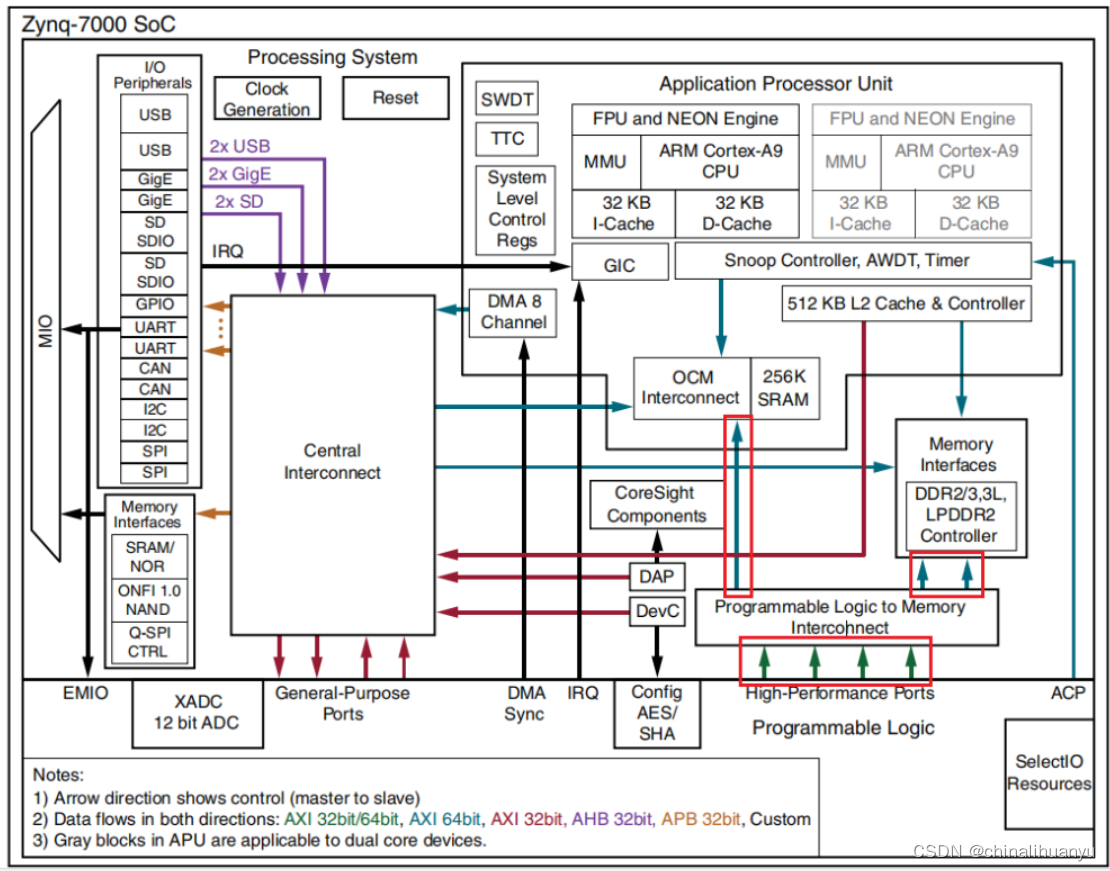

PL:通用可編程邏輯FPGA。

PS:兩個 Cortex-A9 核、 IO 外設、各類硬核控制器等資源在內的 SOC 處理系統。

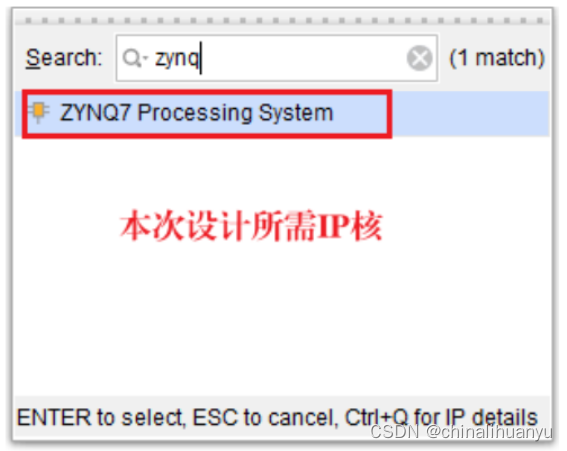

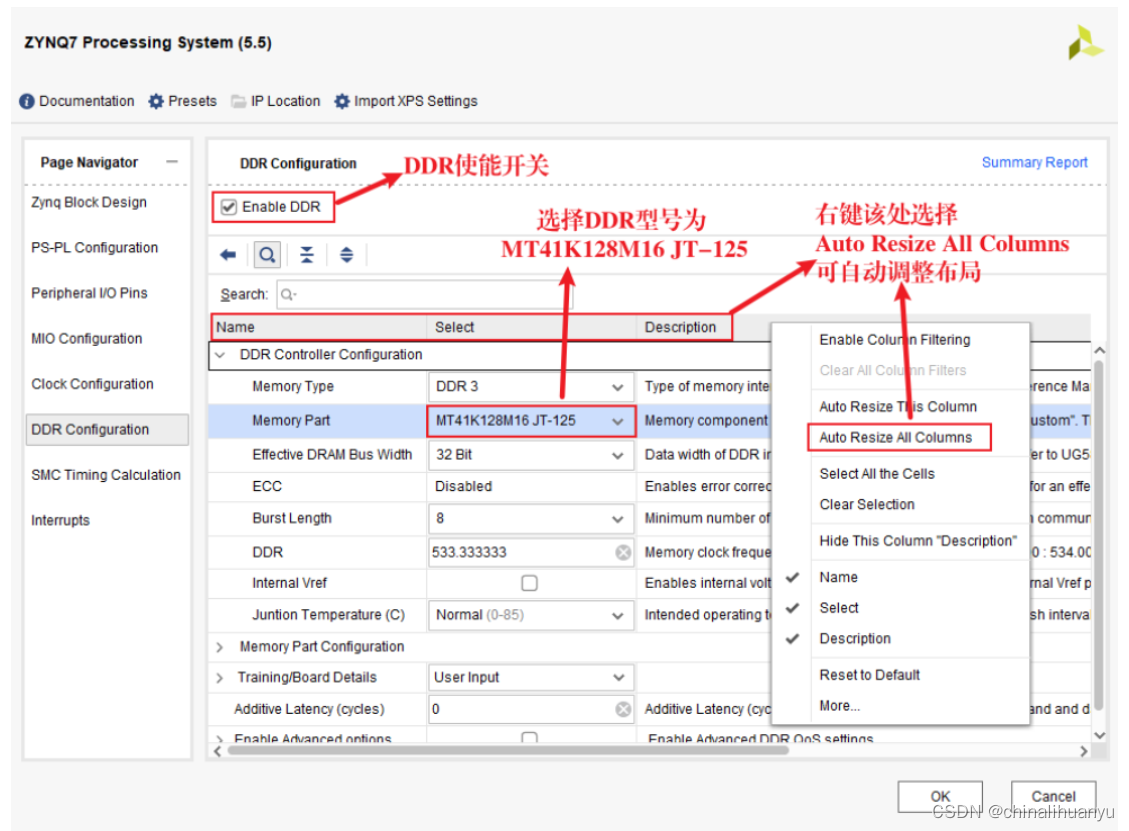

PS部分的DDR3主要用作ARM CPU的內存系統,ARM CPU的程序可以在該DDR3中運行,PS部分的DDR3存儲器使用,不需要,也不能調用MIG IP來控制,只需要在設計中添加ZYNQ7 Processing System 組件,并配置好DDR相關的參數,即可使用。ACZ7015開發板的DDR型號為MT41K256M16 RE-125。

?

PL部分如果要使用DDR3存儲器:

第一種:首先在PL部分要設計DDR3部分電路,并且需要通過在IP Catlog中調用MIG IP來創建DDR3控制器。

第二種:PL通過AXI4(4個高性能數據交互端口,High-Performance Ports)接口使用PS的DDR3存儲器空間。

2.架構優勢

PL通過HP端口寫入到PS側DDR3中的數據,不僅PL可以再讀回來,同時PS側的ARM CPU也可以讀寫這些數據。相同的道理,PS側在某些區域寫入的數據,PL側也可以從該區域讀出來使用。

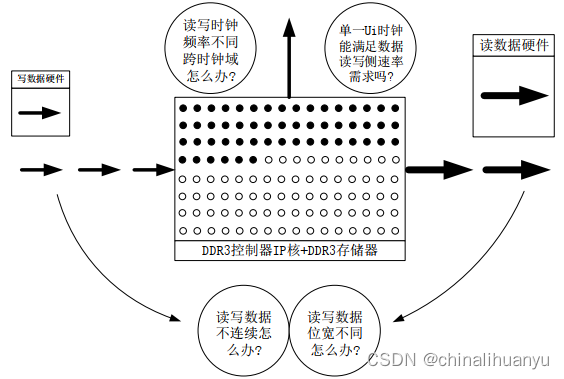

3.直接使用DDR控制器可能會遇到的實際問題

如何確保讀寫DDR時數據的有效性以及讀寫傳輸的高效性?

3.1讀寫時鐘頻率不同跨時鐘域怎么辦?單一Ui時鐘能滿足數據讀寫側速率需求嗎?

DDR控制器的時鐘頻率恒定,但是大部分硬件(讀寫)有自身的固定工作頻率、數據讀寫頻率,并且有可能與DDR時鐘頻率不一致。有可能導致DDR控制器無法滿足讀寫硬件的速率需求,進而數據交互存在跨時鐘域,還會導致DDR讀寫錯誤。

3.2讀寫數據不連續怎么辦?

在速率滿足的情況下,還可能存在外設發送接收數據并不連續的問題。

3.3讀寫數據位寬不同怎么辦?

DDR典型數據位寬128位,但外設一般為8位或16位。

以上問題通過在讀寫段各添加一個FIFO解決,進而引出AXI轉化模塊。

和Object.defineProperty使用詳細,Vue2和vue3中雙向數據綁定的原理)

變基與揀取 —— 變基操作的概念、適用場景及其實現方式,揀取操作的實現 ~)

)

)

:Docker環境的搭建)

-InnoDB的備份與還原策略)