LVDS低電壓差分信號簡介

1. 名詞解釋

1.1. 背景

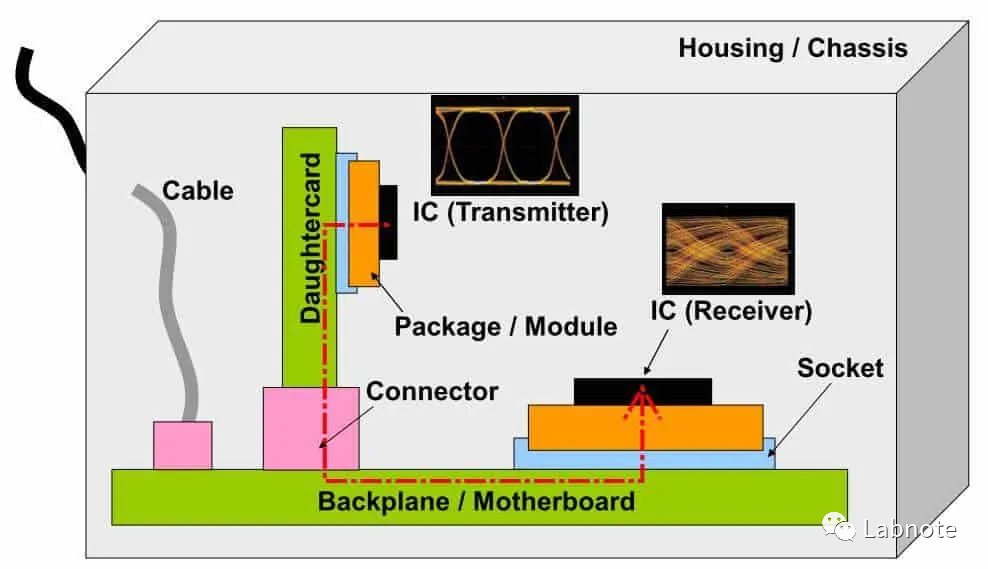

隨著數據傳輸速率越來越高,現在計算機系統中的數據傳輸接口基本上都串行化了,像USB、PCIe、SATA、DP等等外部總線將并行總線擠壓到只剩下內存總線這個最后的堡壘。當然,就算是并行傳輸總線最后的倔強DDR也在不斷吸收SERDES上的技術來提升自己,尤其是均衡器(Equalization,EQ)技術,在DDR5標準中,DRAM將被指定涵蓋DFE(判決反饋均衡)能力。

隨著信號速率的提高,在系統同步接口方式中,有幾個因素限制了有效數據窗口寬度的繼續增加。

時鐘到達兩個芯片的傳播延時不相等(clock skew)

并行數據各個bit 的傳播延時不相等(data skew)

時鐘的傳播延時和數據的傳播延時不一致(skew between data and clock)

要提高接口的傳輸帶寬有兩種方式,一種是提高時鐘頻率,一種是加大數據位寬。那么是不是可以無限制的增加數據的位寬呢?這就要牽涉到另外一個非常重要的問題–同步開關噪聲(SSN),數據位寬的增加,SSN成為提高傳輸帶寬的主要瓶頸。

由于信道的非理想特性,信號從Tx通過FR4 PCB板傳輸到Rx,這中間會有信號插損、回損、近/遠端串擾,再繼續提高頻率,信號會嚴重失真,這就需要采用均衡和數據時鐘相位檢測等技術,這也就是SerDes所采用的技術。

1.2. 歷史

LVDS(Low-Voltage Differential Signaling,低電壓差分信號)是美國國家半導體(National Semiconductor, NS,現TI)于1994年提出的一種信號傳輸的電平標準,它采用極低的電壓擺幅高速差動傳輸數據,可以實現點對點或一點對多點的連接,具有低功耗、低誤碼率、低串擾和低輻射等優點,已經被廣泛應用于串行高速數據通訊場合,如高速背板、電纜和板到板數據傳輸與時鐘分配,以及單個PCB內的通信鏈路。

2. 技術標準

低電壓差分信號(LVDS)是一種高速點到點應用通信標準。多點LVDS (M-LVDS)則是一種面向多點應用的類似標準。LVDS和M-LVDS均使用差分信號,通過這種雙線式通信方法,接收器將根據兩個互補電信號之間的電壓差檢測數據。這樣能夠極大地改善噪聲抗擾度,并將噪聲輻射降至最低。相對于LVDS,M-LVDS指定了更高的差分輸出電壓,以便允許來自多點總線的更高負載。

兩種協議都是面向高速通信設計的。典型應用環境下會采用PCB走線或較短的有線/背板鏈路。LVDS的共模范圍就是針對這些應用而設計。相對于LVDS,M-LVDS擴展了其共模范圍,允許多點拓撲結構中具有額外噪聲。

LVDS是一種用于替代發射極耦合邏輯(ECL)或正發射極耦合邏輯(PECL)的低功耗邏輯 。LVDS的主要標準有兩個:即TIA(電訊工業聯盟)/EIA(電子工業聯盟)的ANSI/TIA/EIA-644標準(LVDS接口也因此稱為RS-644接口)與IEEE 1596.3—SCI(可擴展一致性接口)。LVDS廣泛用于高速背板、電纜和板到板數據傳輸與時鐘分配,以及單個PCB內的通信鏈路。

LVDS/M-LVDS應用考慮

總線類型和拓撲結構

時鐘分配應用

LVDS/M-LVDS信號的特性

端接和PCB布局

抖動和偏斜

數據編碼和同步

隔離

3. 技術原理

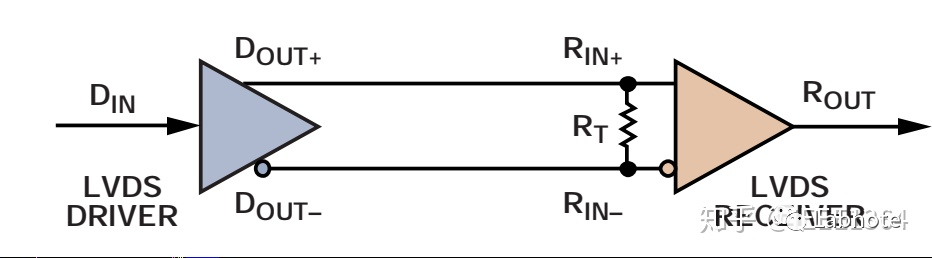

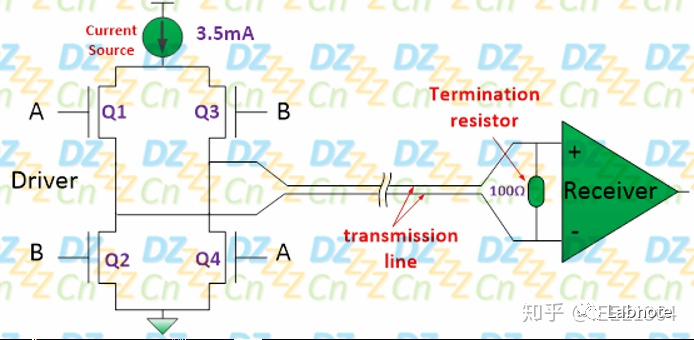

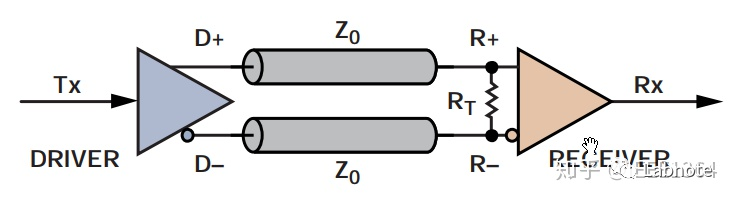

通常一個簡單的點到點(point to point )LVDS的電路結構如下圖所示:

LVDS點對點通訊

LVDS點對點通訊

其基本優勢是結構簡單,功耗低,速度快,抗干擾能力強,能夠傳輸5-10m。但是這一切又都是如何實現的呢?接下來就簡要介紹一下技術上的細節。

3.1. 硬件構造

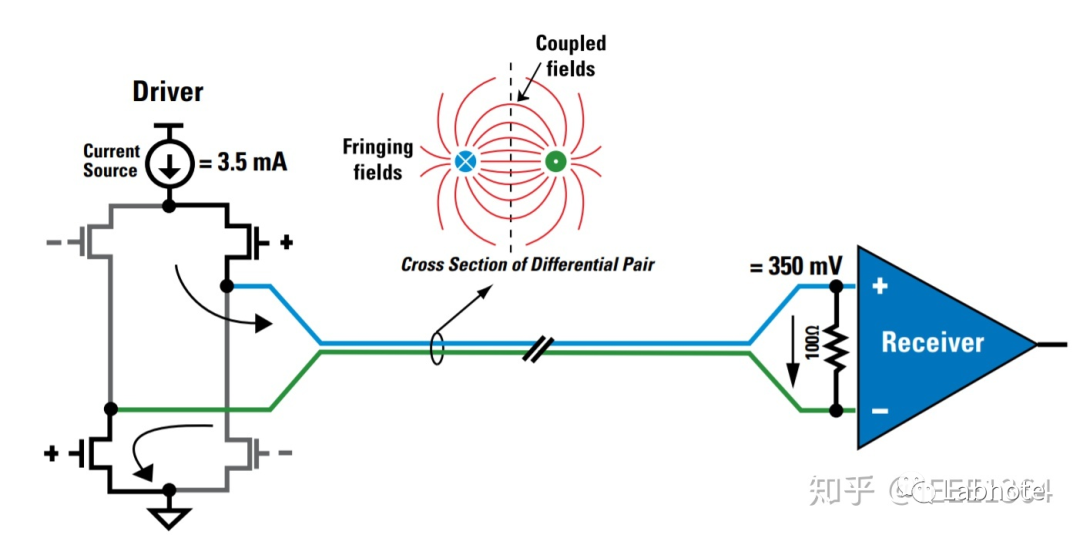

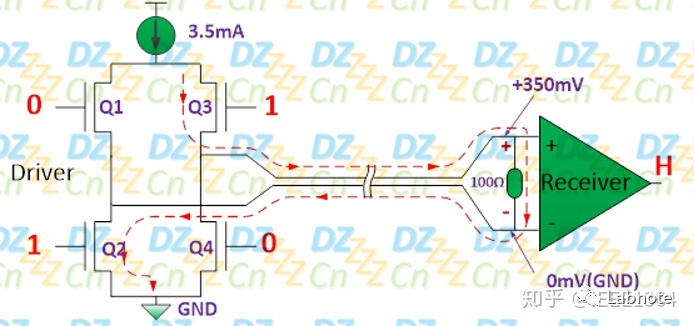

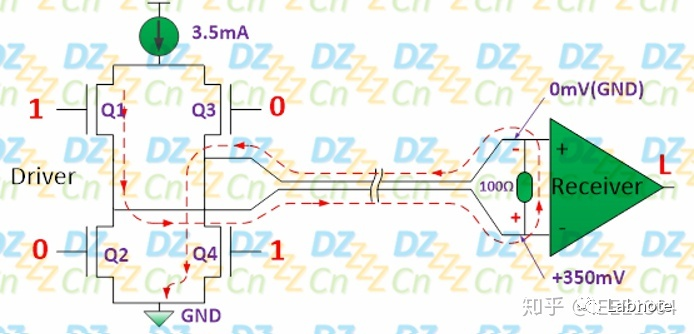

LVDS電平標準采用一對(兩根)差分信號線傳輸數據。通過驅動3.5mA的穩定電流源,可在100Ω終端電阻時,以350mV這樣非常低振幅的差動信號來高速傳送數據。其數據傳輸速度在規格內限定最大為655Mbit/s。但這并不是極限值。通過各半導體廠商獨有的加工,可以完成3Gbit/s左右的高速傳輸速度。

LVDS硬件構造

LVDS硬件構造

LVDS 信號傳輸一般由三部分組成:?差分信號發送器,差分信號互聯器,差分信號接收器。

差分信號發送器:將非平衡傳輸的TTL 信號轉換成平衡傳輸的LVDS 信號

差分信號接收器:將平衡傳輸的LVDS 信號轉換成非平衡傳輸的TTL 信號

差分信號互聯器:包括聯接線(電纜或者PCB 走線),終端匹配電阻。按照IEEE 規定 ,電阻為100 歐,我們通常選擇為100 ,120 歐。

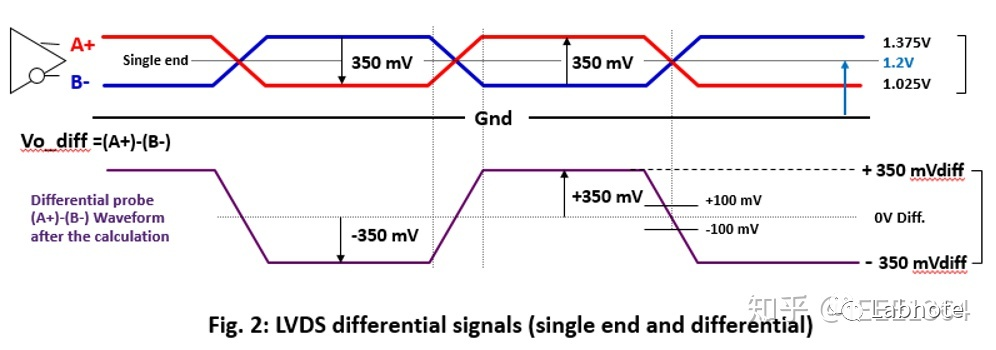

LVDS的差動信號波形的具體示例請見下圖:

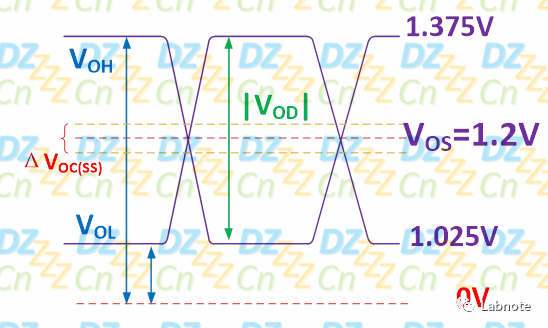

LVDS的差動信號波形

LVDS的差動信號波形

將兩根差動信號--正電極信號(A+)和負電極信號(B?),以1.2V的共同電壓(Voc)為中心,使2個信號間以350mV的電位差擺動。然后,用探針測定示波器的差動,會得到圖2這樣的信號波形。這就是兩個信號的振幅差((A+)?(B?))。以差動探針測定,就能得到振幅差的計算結果。但是這樣的信號波形并不是物理存在的。

3.2. LVDS收發器

概述:?電流驅動——電壓接收——共模電壓由0-2.4V直流偏置,典型為1.2V——差模電壓:350mV由驅動電流提供

LVDS的發送器與接收器的基本結構如下圖所示。它使用兩根線(即差分信號線)來傳輸一個信號,并且使用恒流源(Current Source)驅動,即電流驅動型(而TTL、CMOS之類電平標準為電壓驅動型)。

LVDS收發器基本結構

LVDS收發器基本結構

其中,驅動器(Driver)中的場效應管(不一定是場效應管,因為LVDS技術規范主要側重于LVDS接口的電氣、互連與線路端接,對于生產工藝、傳輸介質及供電電壓無明確要求,也就是說,可以采用CMOS、GaAs或其它工藝實現,能抓到老鼠的黑貓白貓都是好貓)組成一個全橋開關電路,用來控制3.5mA恒流源的電流流動方向,接收器(Receiver)的同相與反相端之間并聯了一個100歐姆的端接電阻,LVDS接收器具有很高的輸入阻抗,因此驅動器輸出的電流大部分都流過100Ω的匹配電阻,并在接收器的輸入端產生大約350mV 的電壓,再經過接收器判斷就形成了高低電平。電流源為恒流特性,終端電阻在100 ~120 歐姆之間,則電壓擺動幅度為:3.5mA * 100 = 350mV ;3.5mA * 120 = 420m V。

當Q2、Q3導通而Q1、Q4截止時,恒流源電流經Q3流向接收器,并向下穿過100歐姆端接電阻再返回至驅動端,最后經Q2到地(GND),3.5mA的電流在100歐姆電阻上產生350mV的壓降,此時同相端電壓高于反相端電壓,輸出為高電平“H”,如下圖所示:

而當Q2、Q3截止而Q1、Q4導通時,恒流源電流經Q1向右流向接收器,并向上穿過100歐姆端接電阻再返回至驅動端,最后經Q4到地(GND),3.5mA的電流在100歐姆電阻上也產生350mV的壓降,但此時同相端電壓低于反相端電壓,輸出為高電平“L”,如下圖所示:

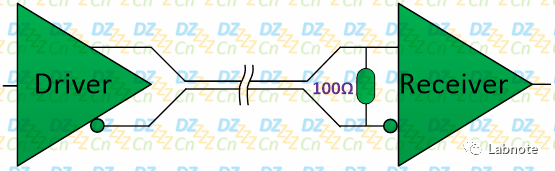

通常我們將LVDS接收器與發送器簡化成類似下圖所示:

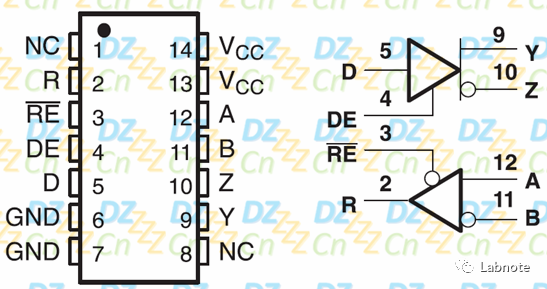

如下圖所示(來自TI公司LVDS收發芯片SN65LVDS180數據手冊)

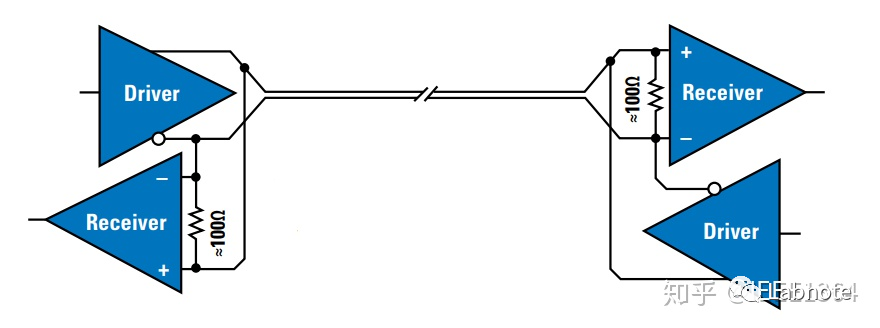

從LVDS結構原理可以看出,一對差分信號線只能夠進行一個方向的數據傳輸,即單工通信(也稱為點對點傳輸point-to-point),但是我們常見的USB接口也只是使用一對差分信號線,為什么卻可以雙向傳輸呢?原因很簡單,它是使用兩對驅動器與接收器組合而成的,如下圖所示:

USB接口結構

USB接口結構

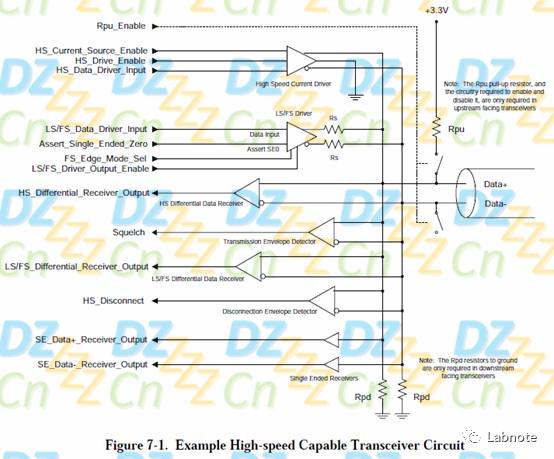

這是一種**半雙工(half duplex)**的配置結構,也就是說,在任意時刻差分信號線仍然只能是往一個方向傳輸數據,但可以分時進行雙向數據傳輸,當驅動器1向接收器1發送數據時,驅動器2與接收器2相當于無效的,反之亦然。當然,USB總線的實際結構要復雜得多,如下圖所示(來自USB2.0規范,扯遠了)

USB2.0

USB2.0

3.3. LVDS電氣參數

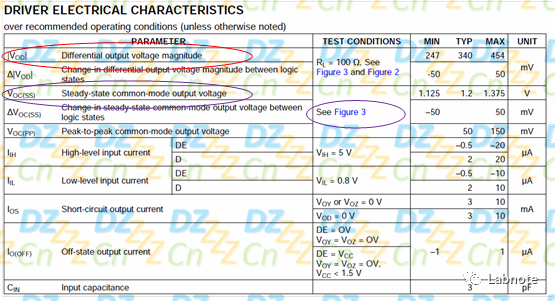

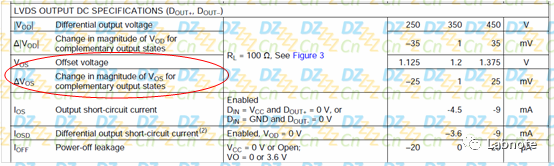

我們來看看如下圖所示的LVDS驅動器電氣參數(來自TI公司LVDS收發芯片SN65LVDS180數據手冊)

SN65LVDS180

SN65LVDS180

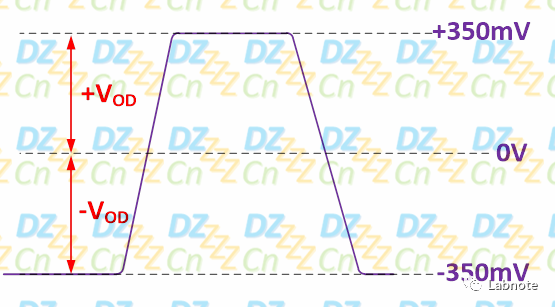

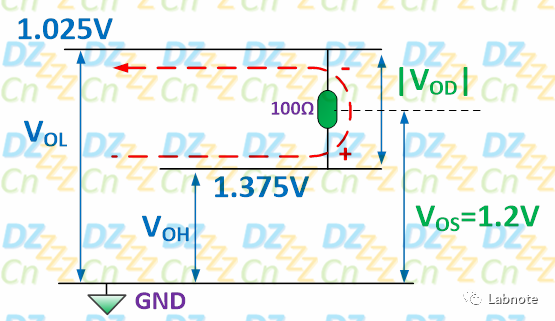

上表中的VOD(Differential output voltage magnitude)即驅動器的差分輸出電壓幅度,也就是前述在端接電阻上產生的350mV壓降,我們可以用下圖所示(注意:是差模信號):

VOD差分輸出電壓幅度

VOD差分輸出電壓幅度

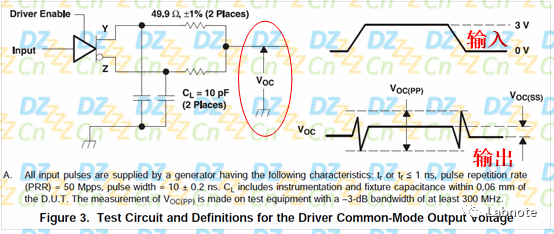

表中還有一個VOC(SS)(Steady-state common-mode output voltage)即穩態共模輸出電壓是個什么東西呢?我也不是很明白!咱們按圖索驥找到數據手冊中的Figure 3,如下圖所示:

VOC穩態共模輸出電壓

VOC穩態共模輸出電壓

哦,原來是當驅動器輸入數字信號(未轉換成LVDS信號前)時,轉換出來的LVDS信號電壓對公共地的平均值,也稱為VOS(Offset Voltage,),TI公司的其它數據手冊有使用VOS如下圖所示:(來自TI公司的LVDS收發芯片型號SN65LVDS049數據手冊)

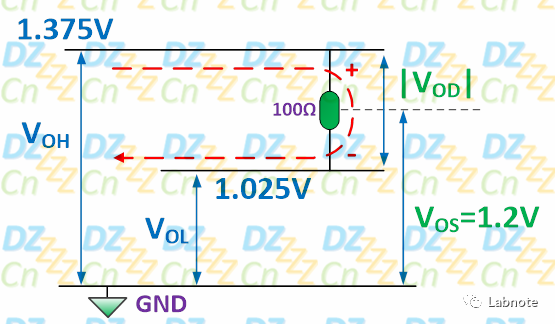

我們之前講過,當使用LVDS電平標準傳輸高低電平時,接收端收到了+350mV或-350mV的壓降只是差模信號,實際上還有一定的共模信號,它不影響接收器進行數據的判斷。

當驅動器向接收器發送高電平“H”時,其等效圖如下所示(注意:這個等效圖僅適合傳輸線非常短的條件下):

當驅動器向接收器發送低電平“L”時,其等效圖如下圖所示

綜合以上兩種等效電路,我們有如下圖所示的電平波形圖:

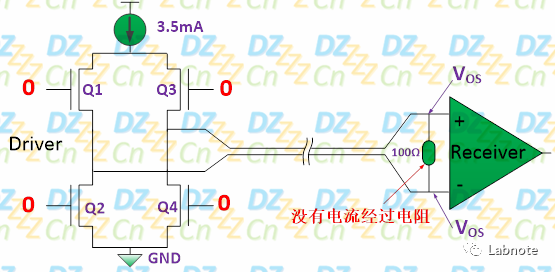

換言之,當LVDS進行高低電平切換時,電流源的電流在換向的瞬間,端接電阻流過的電流為零,因此端接電阻兩端的電壓就是VOS(電阻兩端電壓相同,因此沒有壓降,也沒有電流),如下圖所示:

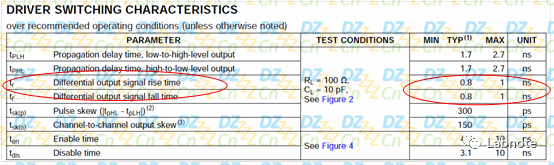

當然,這個電流換向轉換瞬間非常短,通常只有幾百皮秒,如下圖所示:

接收器的輸入電氣參數如下圖所示:

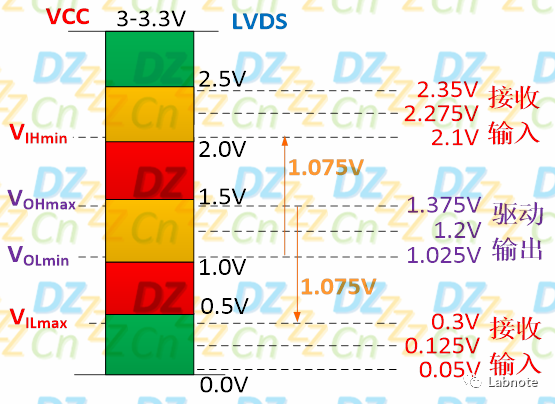

因此我們也可以用下圖表示LVDS電平標準的噪聲容限:

從圖中可以看到,LVDS電平標準的噪聲容限約為1.075V(一般認為其噪聲容限為 1V)這里我們只是根據TI數據手冊畫出電平標準圖,沒有做任何修改,不同廠家的信息可能略有不同。

3.4. 技術優勢分析

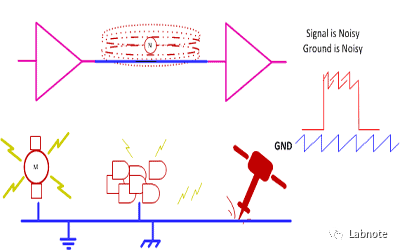

3.4.1. 單端信號和差分信號之間的差異

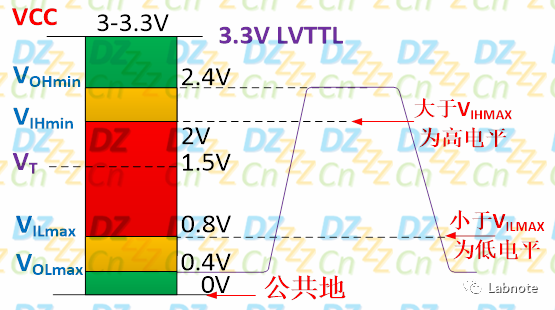

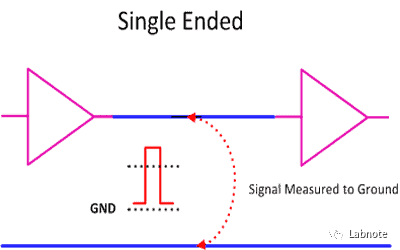

單端信號:?通常大多數低速數字邏輯電平(如TTL、CMOS)是用一根走線來傳輸信號,信號由相對于地參考平面(0V GND)的電平來確定邏輯“ L”和邏輯“ H”

隨著速率的提高,單端信號的上升/下級沿也變得陡峭,因此,輸出開關噪聲會導致信號產生過沖和下沖,并且當多位信號同時轉換時,還要考慮地彈(ground bounce)問題,同時單端信號以參考地平面作為信號回流路徑,這也為Layout帶來了挑戰,由傳輸線阻抗不匹配引起的反射效應會變得非常嚴重。

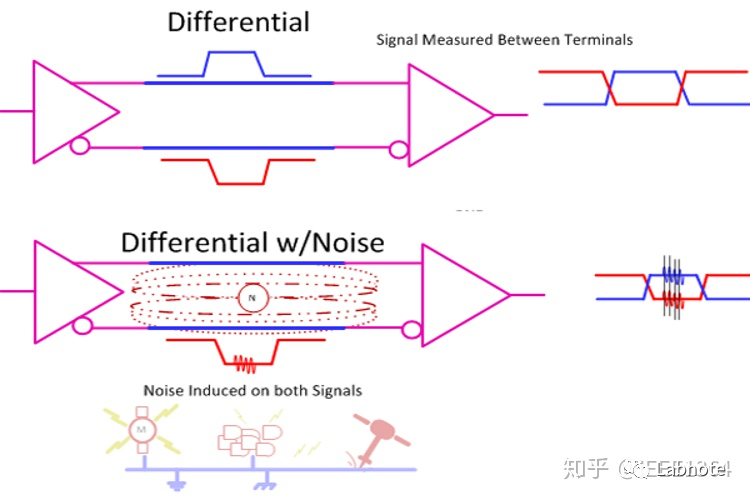

差分信號:?有別于單端信號一根信號線傳輸信號,GND作為高(H)、低(L)邏輯電平的參考并作為鏡像流量路徑的做法,差分傳輸在兩根傳輸線上都傳輸信號,這兩個信號的振幅相等,相位相差180度,極性相反,互為耦合。

3.4.2. 差分信號的優點

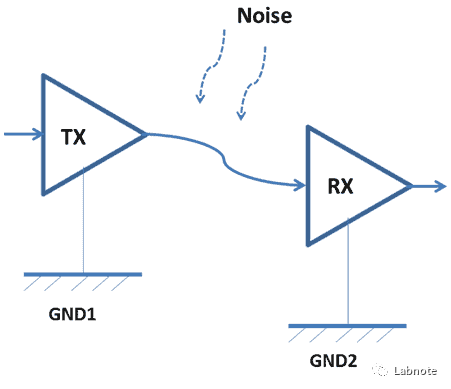

因為你在控制「基準」電壓,所以能夠很容易地識別小信號。在一個參考地(0 V)基準的單端信號傳輸系統里,測量信號的精確值依賴系統內(0 V)的一致性。信號源和信號接收器距離越遠,它們局部地的電壓值之間有差異的可能性就越大。而差分信號恢復的信號值在很大程度上與參考地(0 V)的精確值無關,在某一范圍內便可。

它對外部電磁干擾(EMI)是高度免疫的:一個干擾源幾乎相同程度地影響差分信號對的每一端。既然電壓差異決定信號值,這樣將忽視在兩個導體上出現的任何同樣干擾。除了對干擾不大靈敏外,差分信號比單端信號生成的EMI還要少。

在一個單電源系統,能夠從容精確地處理「雙極信號」。為了處理單端,單電源系統的雙極信號,我們必須在地和電源干線之間某任意電壓處(通常是中點)建立一個虛地。用高于虛地的電壓來表示正極信號,低于虛地的電壓來表示負極信號。接下來,必須把虛地正確地分布到整個系統里。而對于差分信號,不需要這樣一個虛地,這就使我們處理和傳播雙極信號有一個高真度,而無須依賴虛地的穩定性。

3.4.3. 低壓的優勢

隨著集成電路的發展和對更高數據速率的要求,低壓供電成為急需。降低供電電壓不僅減少了高密度集成電路的功率消耗,而且減少了芯片內部的散熱,有助于提高集成度。減少供電電壓和邏輯電壓擺幅的一個極好例子是低壓差分信號(Low Voltage Differential Signaling LVDS),同時也降低了系統功耗。

3.5. 小結

LVDS的優勢包括:

通信速度高達1Gbps或以上

電磁輻射EMI更低

抗擾度EMC更高

低功耗工作

共模范圍允許高達±1V的接地失調差額

4. 技術擴展

4.1. LVDS的傳輸距離傳輸距離

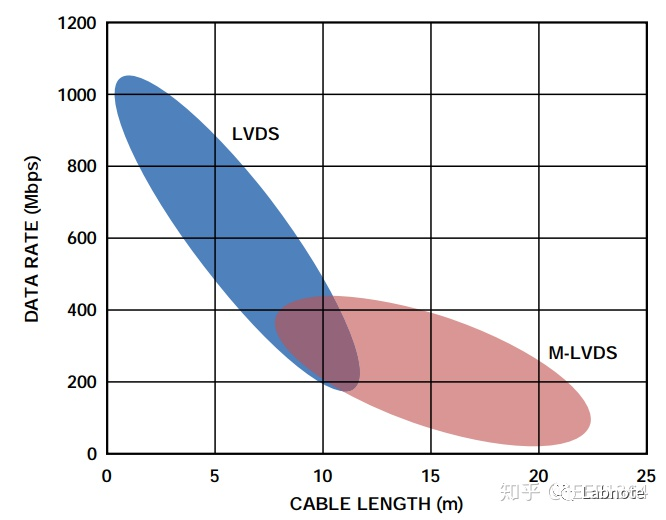

LVDS傳輸距離均受兩個主要因素的影響:傳輸介質和數據速率。關于給定傳輸距離,是否切合實際的標準決定于接收節點觀察到多大的抖動,這與應用環境有關。有些應用環境需要5%或更低的抖動,有些則容許高達20%的抖動。

PCB走線通常允許大約幾十厘米的傳輸距離;雙絞線電纜用于LVDS時允許大約幾米的傳輸距離;不同規格的PCB構造或電纜類型會對信號造成不同影響,進而影響最大傳輸距離。更高的數據速率會極大地限制傳輸距離;?1 Gbps下的LVDS或許只能通過1米的優質電纜進行傳輸(可能還需要額外的信號調理),但是在100 Mbps條件下傳輸距離可能達到10米 (具體取決于電纜類型)。下圖提供了部分應用環境下典型的LVDS和M-LVDS數據速率及電纜長度組合指示。

部分典型LVDS和M-LVDS應用中的電纜長度(雙絞線)與數據速率

部分典型LVDS和M-LVDS應用中的電纜長度(雙絞線)與數據速率

4.2. 端接和PCB布局

無論是使用電纜還是PCB走線,都應該結合傳輸線路理論對高速通信鏈路進行考慮。LVDS高數據速率需要快速上升時間,這意味著,隨著信號從驅動器一直傳播到總線端部,阻抗不連續和通信鏈路的端部會顯著影響傳輸信號。為避免信號降級,需要沿著通信介質控制阻抗,并保證合適的端接。

端接電阻應該與通信介質的阻抗匹配;對于LVDS,這通常為100 Ω。對于簡單的點到點鏈路,只需要端接距離驅動器最遠的總線端部,如圖14所示。對于多分支總線,如果驅動器在總線的一端,則可采用相同的端接方法,否則需要端接總線的兩端。

4.3. M-LVDS

面向多點低電壓差分信號(M-LVDS)的標準TIA/EIA-899將LVDS延伸到用于解決多點應用中的問題。相對于TIA/EIA-485 (RS-485)或控制器局域網(CAN),M-LVDS能夠以更低的功耗實現更高速度的通信鏈路。M-LVDS往往允許幾十米的傳輸距離,M-LVDS相對于LVDS的額外特性包括:

驅動器輸出強度更高

躍遷時間可控

共模范圍更廣

面向總線空閑條件提供故障安全接收器選項

4.4. 其他差分技術

下圖列舉了幾種常用通信協議的速率和通信距離對比:

速率和通信距離

速率和通信距離

5. Q&A

5.1. 終端電阻100Ω是怎么來的

這個值是根據spec計算出來的,lvds的驅動是3.5mA恒流源,接收端電平判別的典型值是350mv,算出得到終端電阻是100Ω。接收端判別電平的范圍可以根據具體器件的數據手冊來查看。如果想增大抗干擾能力,其實可以適當提高這個電阻的阻值,比較常用值是120Ω。

)

)

)

)