簡要介紹了功耗的組成,在此基礎上從工藝、電路、門、系統四個層面探討了納米級超大規模集成電路的低功耗物理設計方法。

關鍵詞:納米級;超大規模集成電路;電路芯片;電路設計

02

納米級超大規模集成電路芯片低功耗物理設計方法

2.4?系統層面的芯片低功耗物理設計?

2.4.1?軟硬件劃分軟硬件劃分是指將電路系統分為軟件、硬件兩部分。目前,很多知名電子設計自動化 EDA 公司已相繼發布了系統層面的電路設計軟件,能夠實現電路系統層面軟硬件劃分,被行業廣泛應用。例如,Synopsys 公司的 CoCentric 可以同時設計、仿真、實現多個系統核心元器件,Cadence 推出的 Virtual Component Co-design可以定義、分析、優化系統層面的電路設計,給電路設計者提供了系統集成、驗證所需技術和工具,圖形化界面方便設計人員進行協同設計和驗證。利用這些軟件設計人員可以從系統層面對軟件、硬件兩個角度綜合考慮,確定最佳設計方案。2.4.2 功耗管理功耗管理包括動態、靜態兩種管理方式。動態功耗管理是指根據實際情況控制空閑模塊關閉,以減少功耗。靜態功耗管理的對象是電路工作模式。如果系統空閑,則停止芯片工作,休眠系統,從而減少功耗。動態功耗管理實現需要操作系統,因此其應用受到限制。2.4.3 指令優化指令優化流程包括如下 4 步。(1)提取指令集。合理選用指令集可以讓系統功耗降至最低。(2)合理選擇指令長度,提高程序代碼密度,從而降低對存儲器的訪問,降低功耗。(3)優化指令編碼,減少指令讀取時總線信號翻轉,以降低功耗。(4)壓縮指令,指令在內存中進行壓縮,輸入CPU 之前再解壓可以降低 CPU 功耗。03

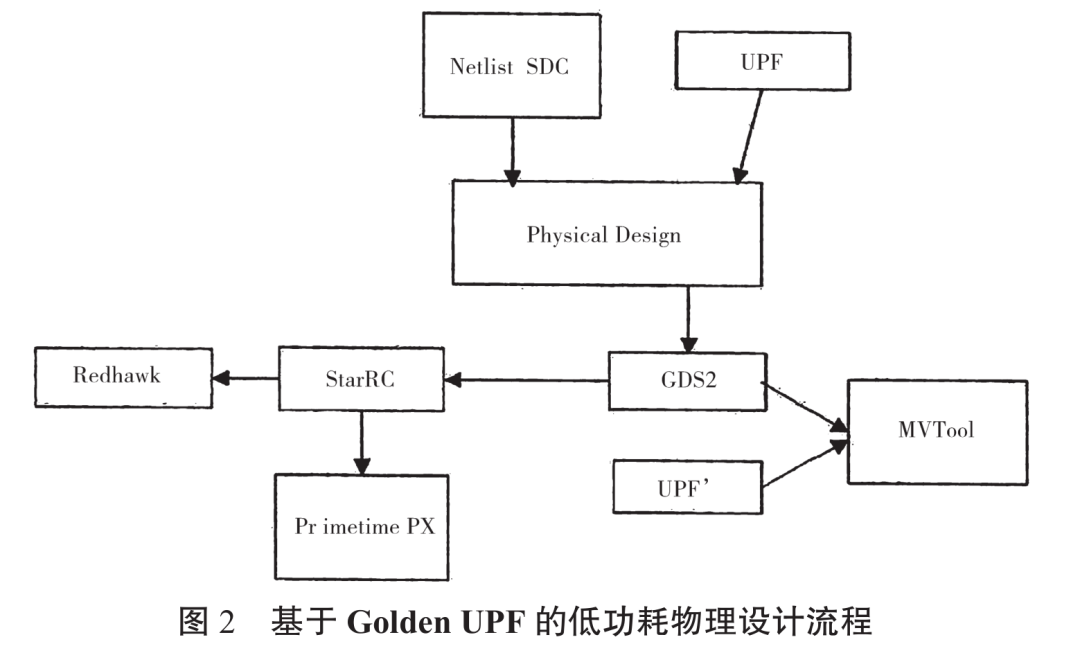

基于 Golden UPF 的低功耗物理設計流程

Golden UPF 主要有便于追蹤、無需修改 UPF 文件及設計效率高等優點。因此,本次研究基于 GoldenUPF(Unified Power Format)進行低功耗物理設計,在滿足電路性能需求的情況下實現低功耗設計目標,設計基本流程如圖 2 所示。

成員內部類)