基于觸發器的三位二進制同步減法計數器無效態000/110

1 課程設計的目的與作用

掌握用multisim 的電路仿真程序

熟悉同步計數器工作原理和邏輯功能

熟悉計數器電路的分析和設計方法

掌握161 芯片集聯成任意進制同步加法計數器

2 設計任務

三位二進制減法計數器(無效態: 000 011)

3設計過程

三位二進制減法計數器(無效態: 000 011)

3.1 狀態轉換圖

3.2 求時鐘方程

CP0 =CP 1 =CP 2 =CP

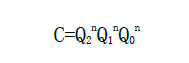

3.3 求輸出方程

3.4 求狀態方程

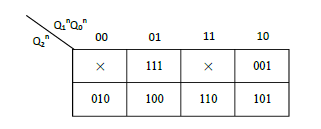

三位二進制同步加法計數器次態的卡諾圖

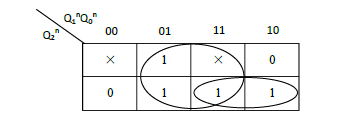

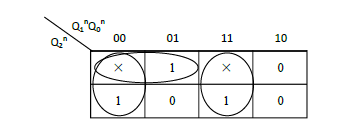

Q 2 n+1 的卡諾圖

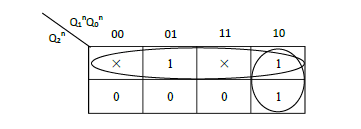

Q 1 n+1 的卡諾圖

Q 0 n+1 的卡諾圖

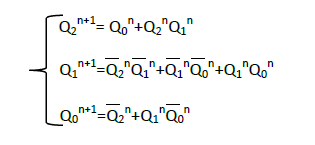

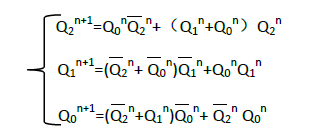

根據卡諾圖得到次態方程

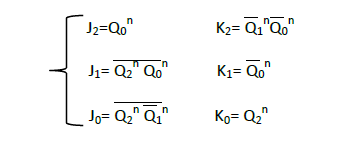

3.5 求驅動方程

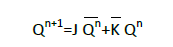

JK觸發器的特性方程為

變換狀態方程的形式:

根據上式,即可得下列驅動方程:

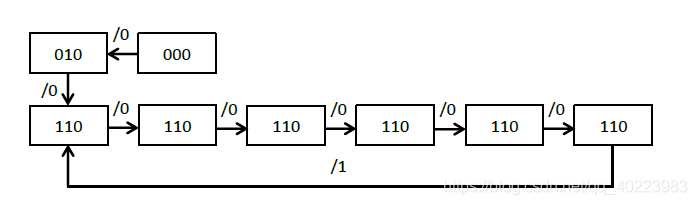

3.6 自啟動驗證及檢驗

該邏輯電路能夠自啟動

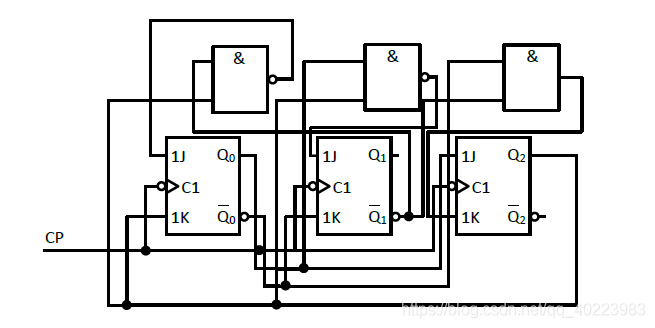

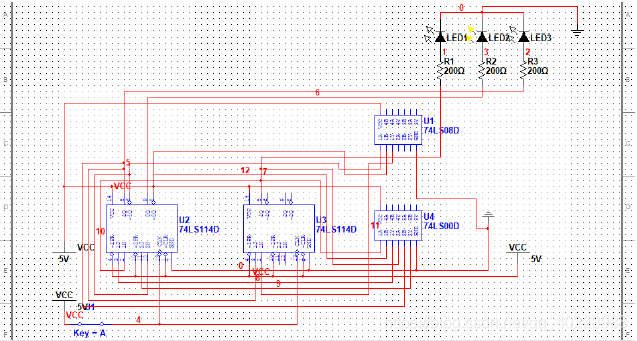

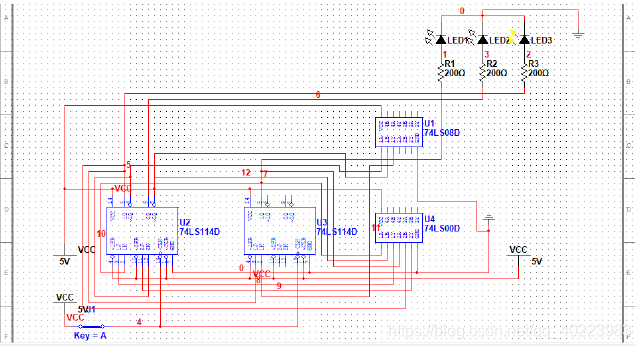

3.7 畫邏輯電路圖

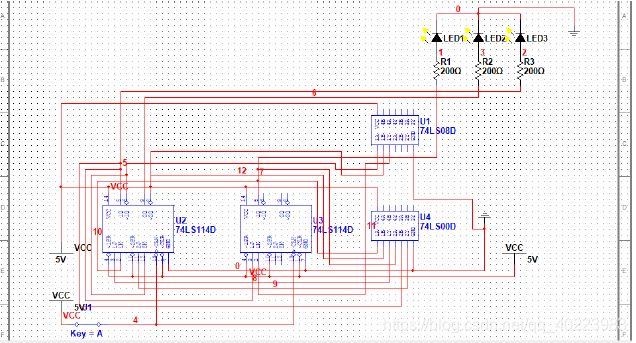

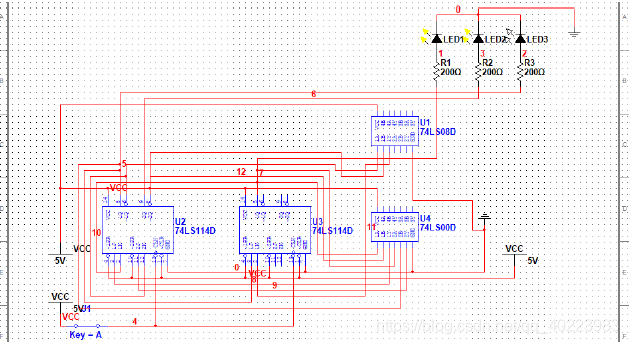

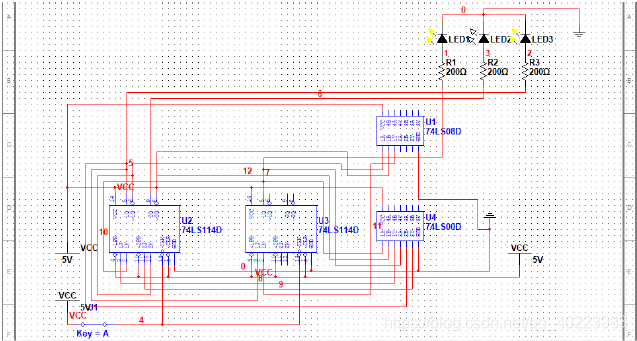

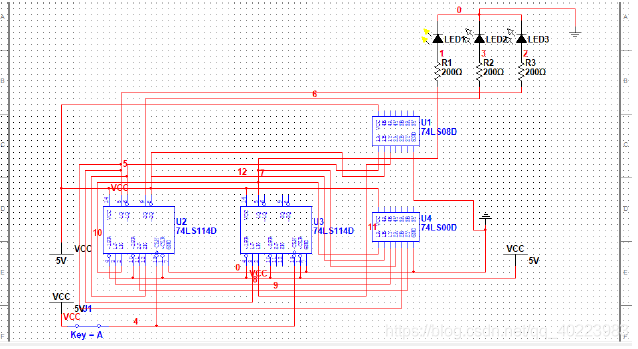

4 仿真結果分析

4.1 三位二進制減法計數器(無效態: 000 011)

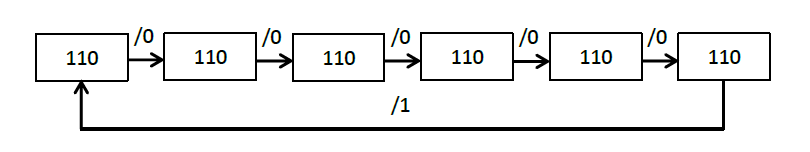

三位二進制減法計數器(狀態: 111)

三位二進制減法計數器(狀態: 110)

三位二進制減法計數器(狀態: 101)

三位二進制減法計數器(狀態: 100)

三位二進制減法計數器(狀態: 010)

三位二進制減法計數器(狀態: 001)

5 設計總結

通過這次數次電路課程設計的學習與實踐,我初步了解簡單數字電路設計過程以及仿真應用,熟悉了以 multisim 為軟件載體的數字電路仿真。其次,鍛煉了我的科學探索精神。在這次課設中,我嘗試了不同的設計思路,把所學的知識結合在一起,仿真出自己設計的電路。當然,在不斷嘗試的過程中,也遇到了不少的問題,獨立思考是必不可少的,同時借鑒網上,書本等材料以及和同學討論也是不可或缺的,也這次的課程設計,也培養了我的科學素養。

針對課題,是簡單的三位二進制加減法計數器的設計,我了解了最基本的數字電路的設計過程,解決簡單的時序問題。熟悉了通過卡諾圖,用簡單的觸發器,設計邏輯電路的過程。

同時掌握了 根據自己通過理論設計出來的數字電路,用 multisim 仿真驗證自己的電路 。 Multisim 這個軟件中的器件很齊全,而我只是簡單的了解,應用了其中的一些元器件。相信在以后的學習過程中,我能更加的熟悉 multisim 這個軟件的應用。

最后,我相信這次的課程設計不會是我學習數字電路的結束,而是我學習數字電路的開始,我將會用這次學到的知識,用在以后的 設計邏輯電路中。

6 參考文獻

[1]清華大學電子教研組 編 . 余孟嘗 主編 . 數字電子技術基礎簡明教程 第三

版 [M]. 北京:高等教育出版社, 2006

[2]信息學院數字邏輯實驗室 編 . 張利萍 張群芳 主編 . 數字邏輯實驗指導書

[M]. 沈陽理工大學

)

...)

:vagrant搭建redis與redis的監控程序redis-stat(轉))

函數)