?

引言

DFT是ASIC芯片設計流程中不可或缺的環節。其主要目的是在芯片前端設計驗證完成后插入一些諸如寄存器鏈等可供測試的邏輯,算是IC后端設計的范疇,屬于結構測試而非功能測試。主要是在ASIC芯片流片完成后,通過這些已插入的邏輯,檢測流片得到的芯片的制造質量。檢測一些固定故障等。

學習參考

- 數字系統測試和可測試性設計。【美】賽納拉伯丁 - 納瓦比 著。原本和譯本。

- 修真院講解視頻。

- E課網 DFT 課程。

- 華中科技大學IC設計中心 陳新武 講稿《集成電路測試方法研究》。

- Design-for-Test: Scan and ATPG Training?Student Workbook ,Copyright ?Mentor Graphics。

故障建模

對芯片制造過程中可能出現的制造缺陷進行建模,可以幫助分析具體故障以及產生測試向量。

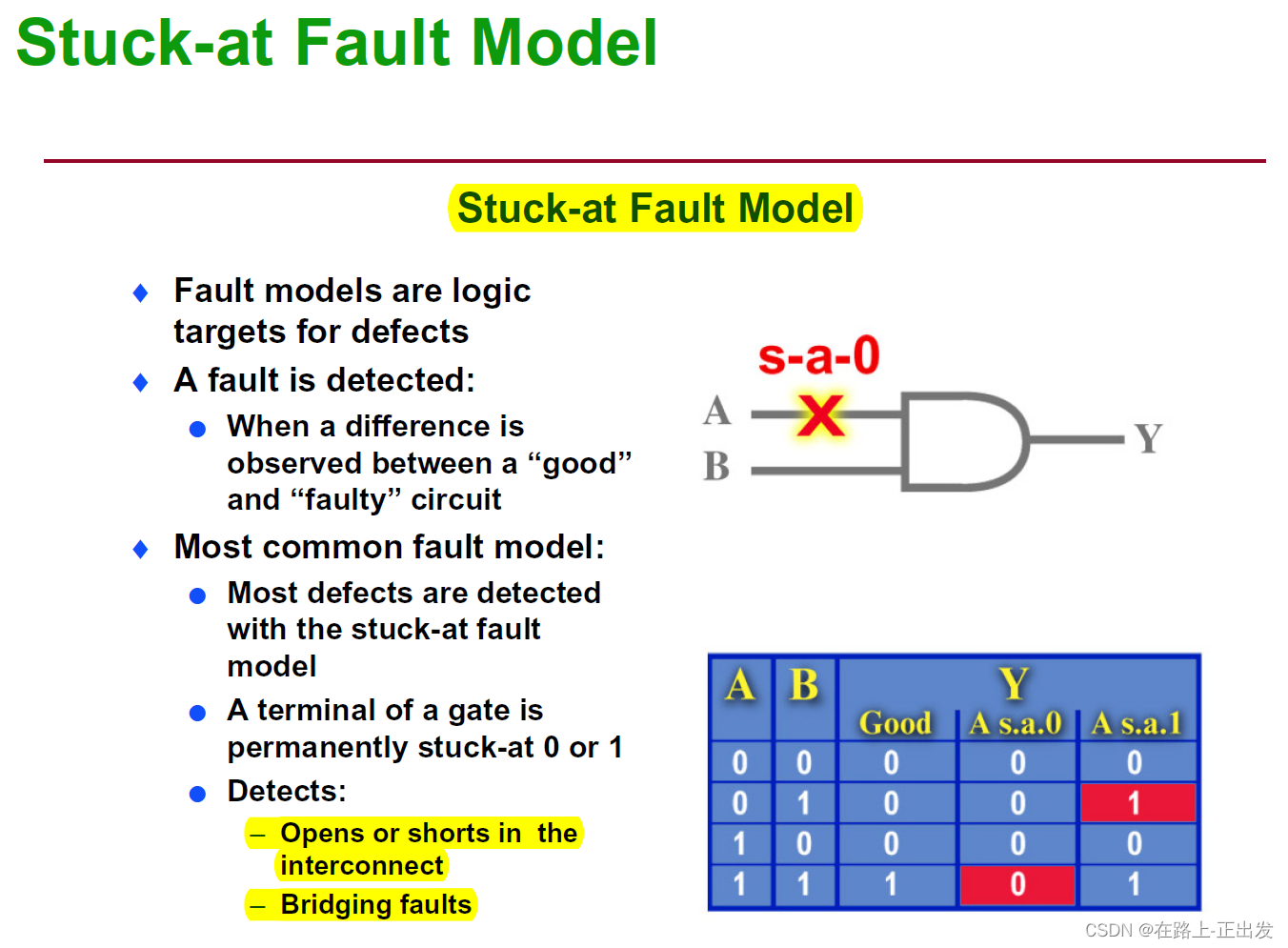

Stuck-at 故障模型

芯片制造過程中由于工藝或者環境控制不佳,導致某些芯片內的布線出現stuck-at問題,即該布線的電平被始終拉高或者拉低。

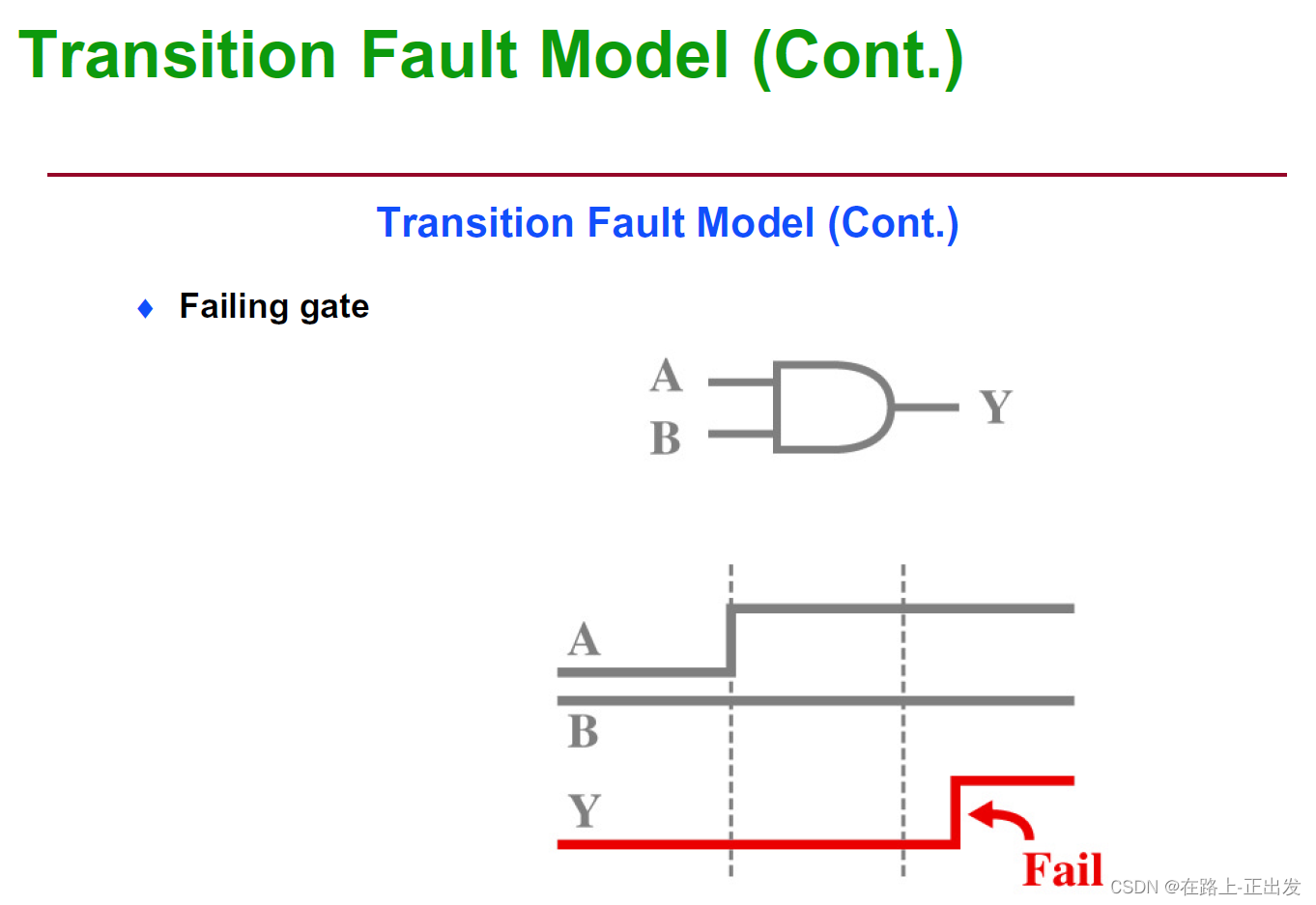

翻轉(transition)故障模型

電平轉換時間變長,即時鐘或者數據的邊沿跳變時間邊長,速率變慢。

對比一下:

?

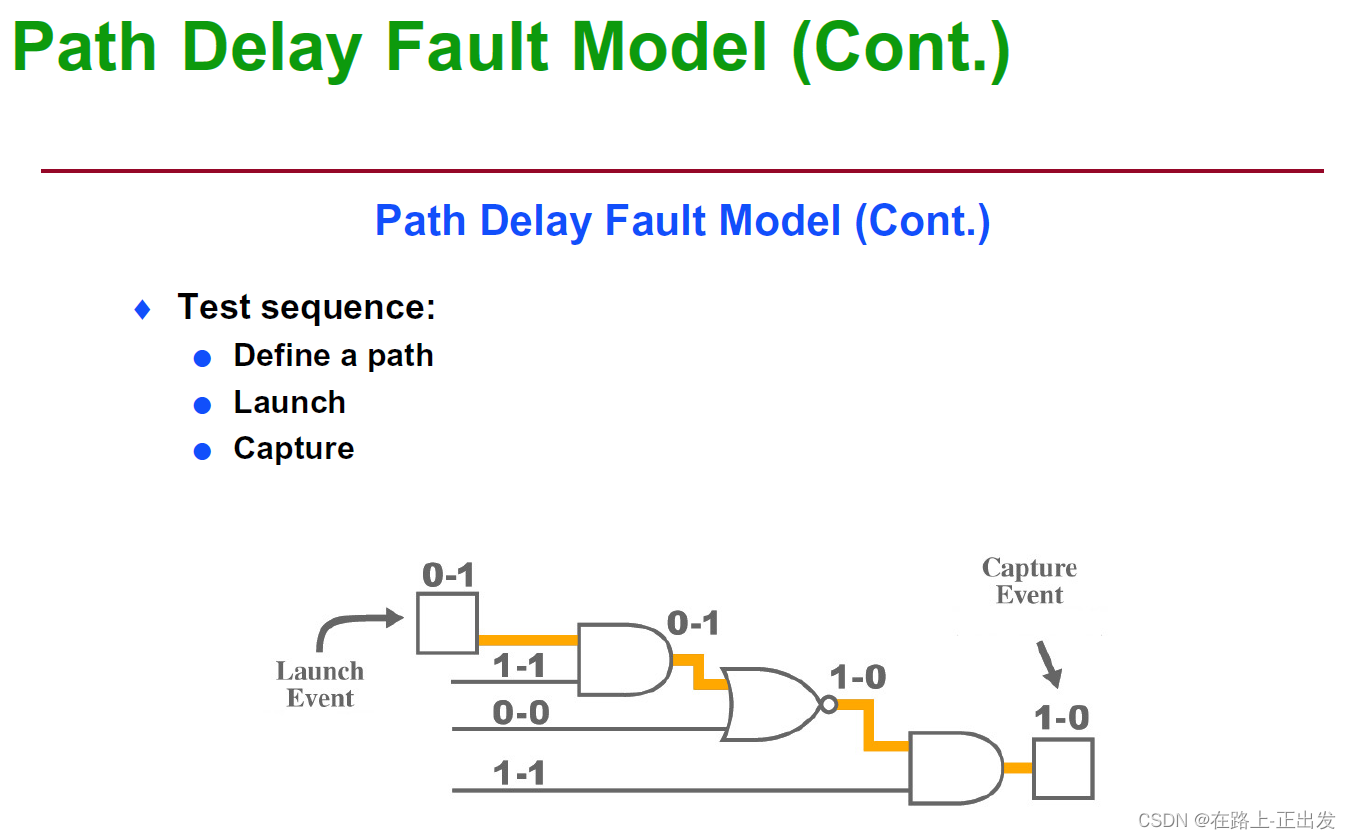

路徑延時故障模型

靜態電流測試

不了解的點擊這里:IDDQ簡介?

掃描 (Scan) 技術

基本說明

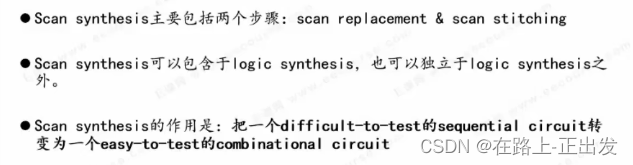

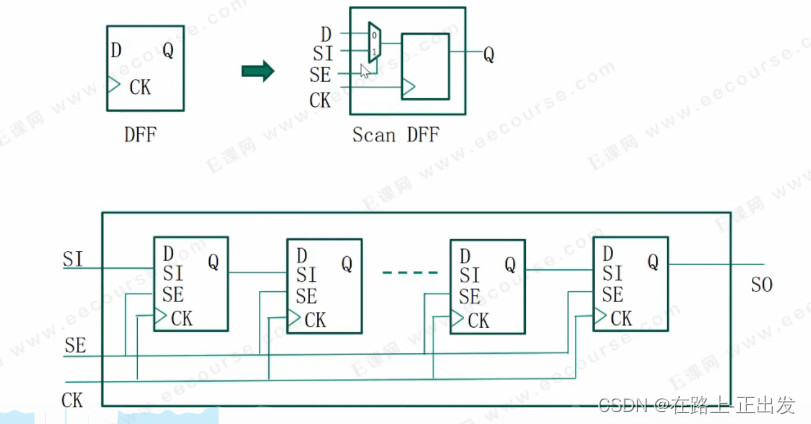

如下圖所示,首先是觸發器替換,將普通的觸發器,替換為掃描觸發器。然后是將各個掃描觸發器串聯起來。?

Scan Cell Type

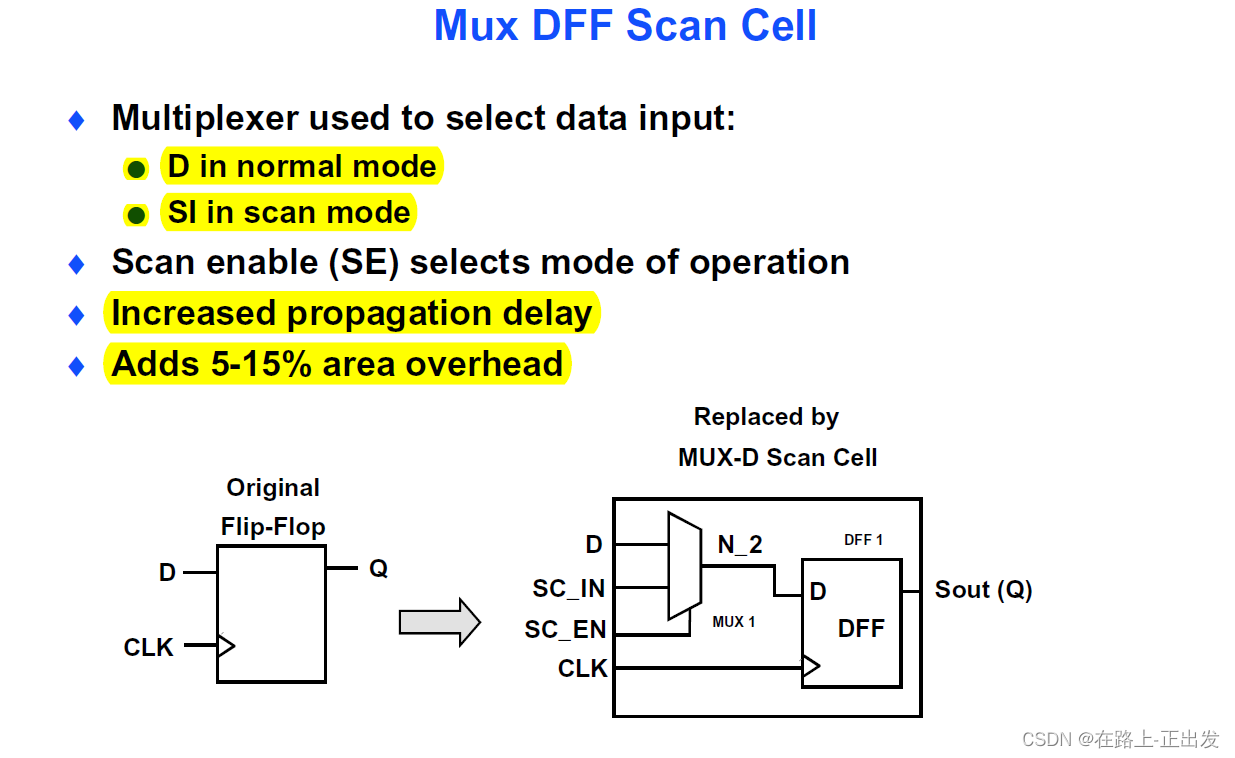

采用多路選擇器而增加的延遲表現在功能路徑中,有較少的面積增加。一個帶多路選擇器的D觸發器通常將一個標準D觸發器的面積增加15%到30%;增加的I/O端口最少的可以只有一個Scan_En。在實際設計中,可能并不需要增加一個另外的I/O端口用于Scan_in或者Scan_out,因為可以在設計中將這些引腳和功能引腳復用。?

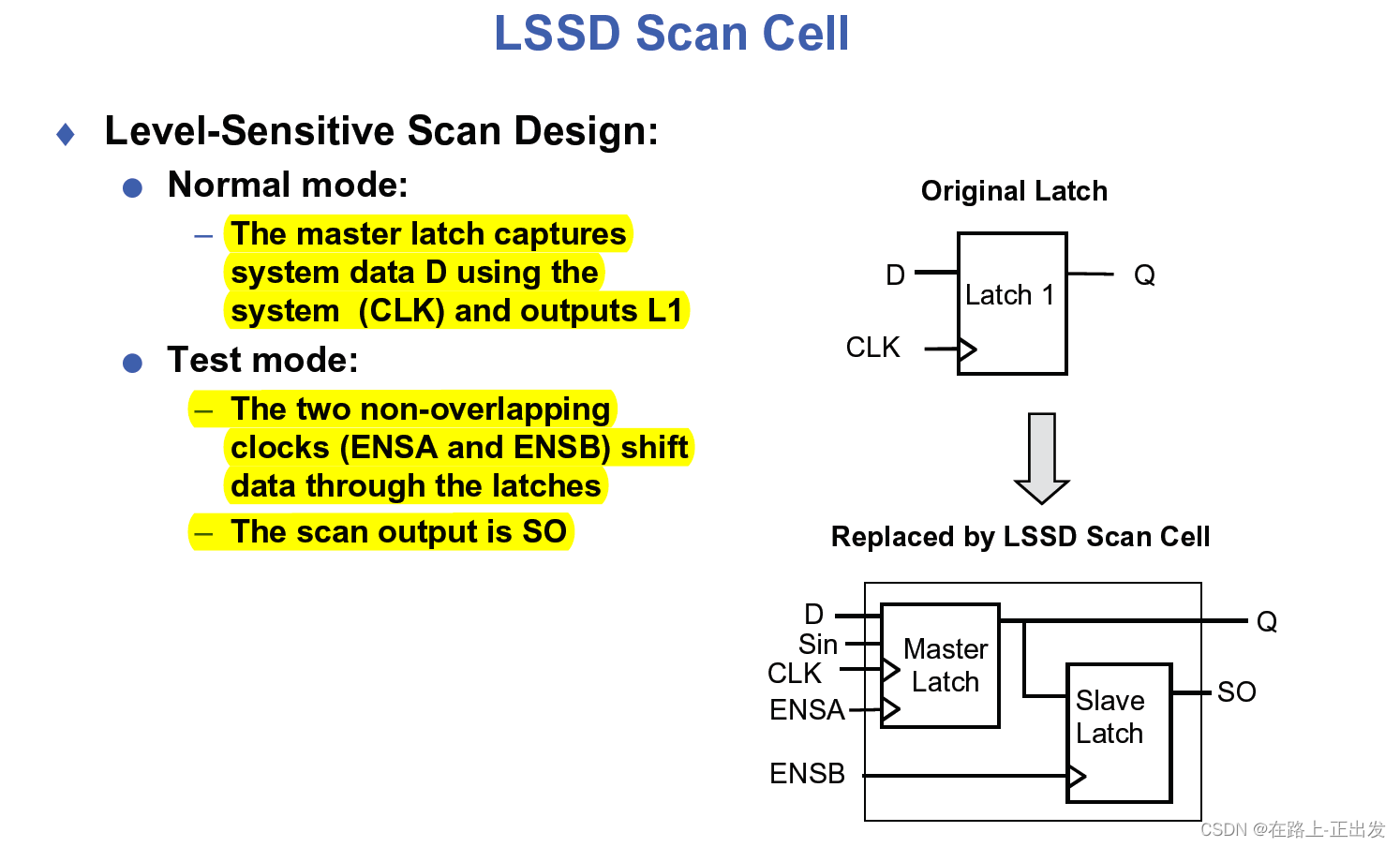

單鎖存電平敏感掃描單元的邏輯結構如圖所示。上圖為通常意義下的D觸發器,下圖為它相應的可掃描單元。增加了一個數據輸入端、兩個時鐘輸入端:?Test_Scan_Clock_a 和Test_Scan_Clock_b。增加的兩個時鐘是電平觸發的。在測試模式下,Test_Scan_Clock_a和Test_Scan_Clock_b連接到所有的同類掃描單元,分別在不同的時刻將掃描數據逐位移動。Scan_in引腳的數據來自上一個掃描單元。

單鎖存器LSSD的特征是:

a) 對電路性能的影響可以忽略;

b) 較高的面積代價。用一個LSSD單元替換一個簡單的鎖存器將會增加100%或者更多時序邏輯的面積。增加的主測試時鐘和從測試時鐘也增加了布線的面積(與多路選擇器型的觸發器掃描類型相比);

c) 支持帶有異步復位和清零端的鎖存器;

d) 因為增加了專用的測試時鐘,所以適合用于部分掃描設計。

專用時鐘控制的掃描方法是使用一個專用的、邊沿觸發的測試時鐘來提供串行移位驅動。在功能模式下,系統時鐘是活動的,系統數據被時鐘打入單元電路。在測試移位過程中,測試時鐘是活動的,掃描數據被打入該電路單元。電路符號如圖4-2所示。圖a為標準的D觸發器,圖b為專用時鐘控制的可掃描單元。在這種結構中,相當于有兩個D輸入端,兩個時鐘輸入端。在這種方式下,需要增加的測試引腳有:掃描輸入、測試時鐘、掃描輸出(可以和輸出功能引腳共用)。?

專用時鐘控制掃描方式的特征是:

對電路性能影響可以忽略;面積的增加可以接受:一個專用時鐘控制的掃描單元一般比普通的D觸發器的面積增加15%--30%;支持這種掃描方式的工藝庫具有觸發器和鎖存器兩種等效單元;很適用于部分掃描設計:專用的測試時鐘提供了一種機制,在掃描移位的過程中,可以很容易地保持非掃描單元的狀態;支持帶有異步置位和復位端的鎖存器;典型的應用是具有邊沿觸發的設計風格。

Scan Chains

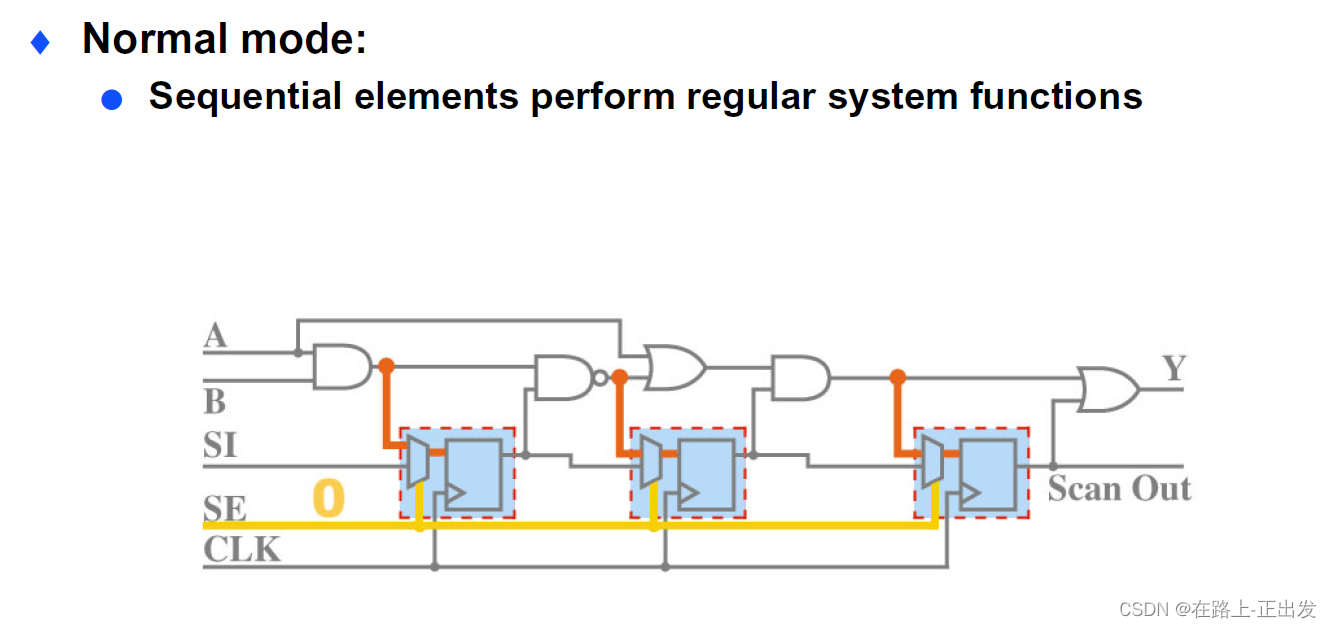

正常模式

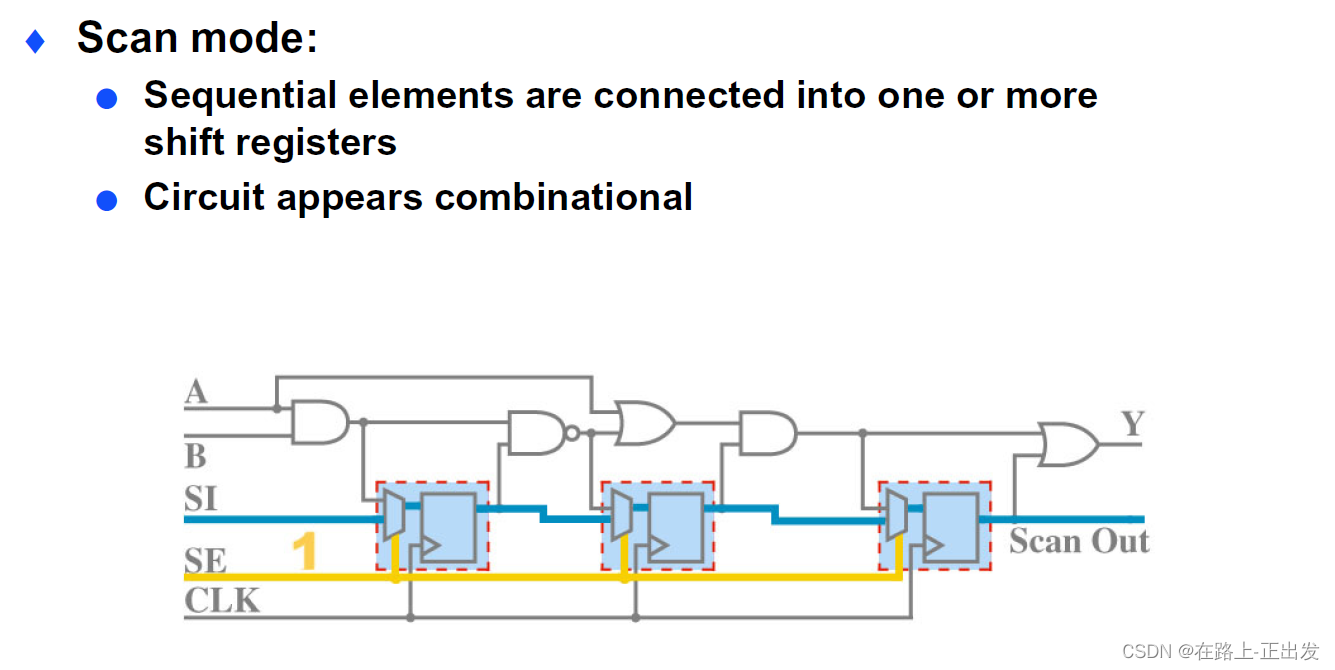

掃描模式

設計流程

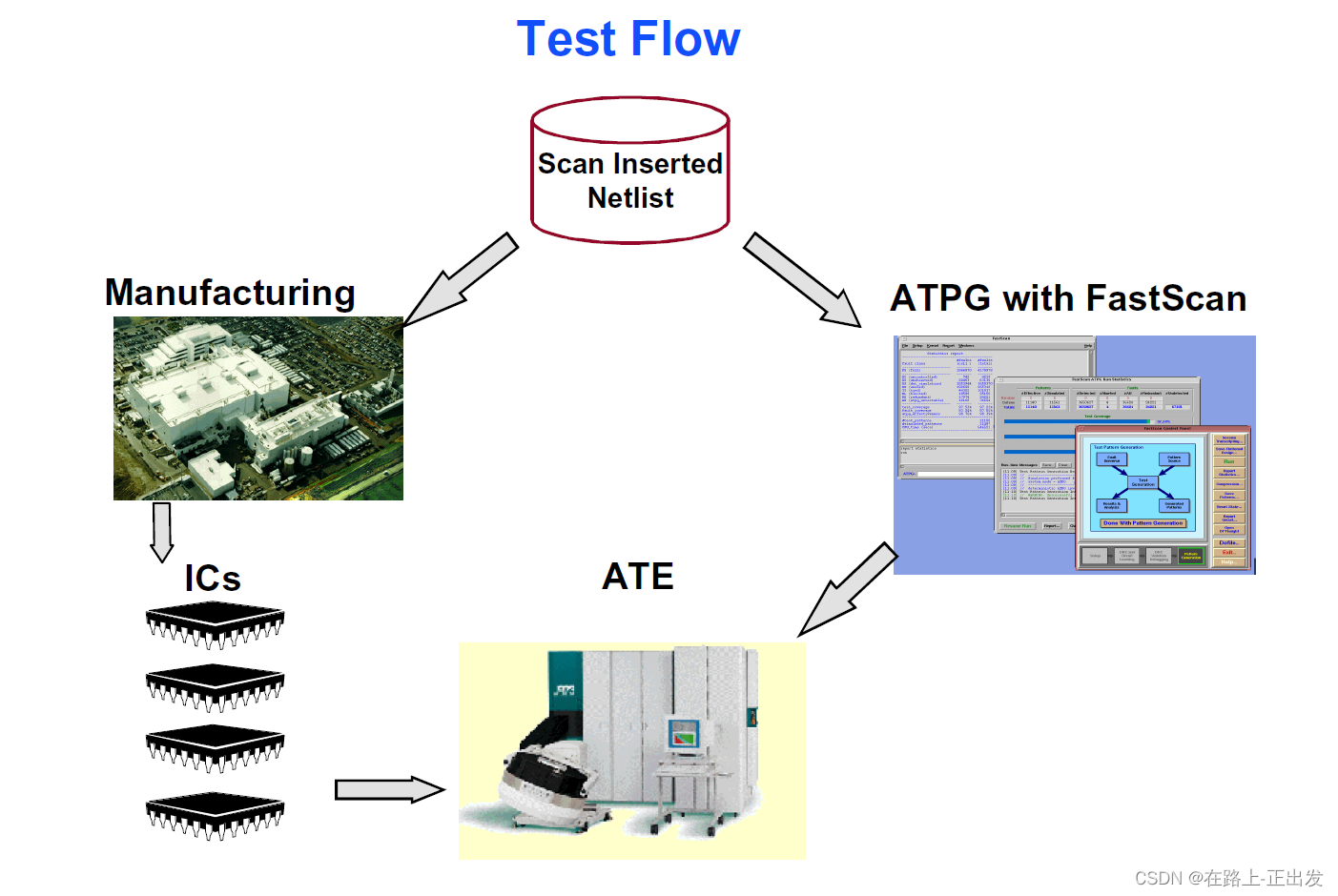

測試流程

工具流程

邊界掃描

移位寄存器單元插入到IC的核心邏輯與I/O管腳之間,以提供通過所有IC的一條串行測試數據通路。因為移位寄存器單元位于IC的邊界處,所以這些單元被稱為邊界掃描單元(BSC,Boundary Scan Cell),由它們構成的移位寄存器稱為邊界掃描寄存器。串行測試數據的輸入端被稱為測試數據輸入端(TDI),相應的輸出端被稱為測試數據輸出端(TDO)。為了完成測試功能,相互連接的邊界掃描單元必須具有數據移位、數據更新、數據捕獲等功能,這些功能是由測試控制邏輯來控制的。測試控制邏輯由兩條信號線驅動:測試方式選擇(TMS)和測試時鐘(TCK)。所以,整個邊界掃描測試要求IC中至少有四個可利用的測試管腳,或將它們附加到其他的功能管腳上。

邊界掃描測試技術的工作原理就是:JTAG測試儀利用一個四線測試接口,將測試數據以串行方式由TDI打入到邊界掃描寄存器中,通過TMS發送測試控制命令,經TAP控制器控制邊界掃描單元完成測試數據的加載和響應數據的捕獲。最后,測試響應數據以串行掃描方式由TDO送出到JTAG測試儀,在那里,將捕獲到的響應數據與期望的響應進行比較。四個管腳TMS、TCK、TDI和TDO被稱為測試訪問端口(TAP, Test Access Port),全部測試控制邏輯被稱為TAP控制器。

內建自測 BIST

BIST主要完成測試序列生成和輸出響應分析兩個任務。通過分析被測電路的響應輸出,判斷被測電路是否存在故障。因此,對數字電路進行BIST測試,需要增加三個硬件部分:測試序列生成器、輸出響應分析器和測試控制部分。

確定性測試方法是一種針對特定的電路故障進行測試的方法,雖然可以得到很高的故障覆蓋率,但硬件開銷大,僅在測試碼個數較少的時候采用。

偽窮舉測試的方法是把所有可能輸入都加以計算的測試方法。它的最大特點是故障覆蓋率可以達到100%,但其計算量與輸入端子呈冪次方關系,因此計算量很大。如果將電路分為多個原始輸入變量互相獨立的塊,則測試數將大大減少。偽窮舉法就是這樣一種壓縮測試向量的方法。偽窮舉法也具有很高的故障覆蓋率,但偽窮舉法對電路進行劃分比較困難,有相當的局限性。而且由于加入了附加硬件,可能對電路性能產生負面效應。

偽隨機測試是一種廣泛使用的測試方法,該方法可以對被測試電路產生大量的測試代碼,而且硬件電路開銷較小,同時具有較高的故障覆蓋率。LFSR(Linear Feedback Shift Register,線性反饋移位寄存器)就是這樣一種測試代碼生成電路。

實現輸出響應分析的方法有ROM比較邏輯法、多輸入特征寄存器法和跳變計數器法等。ROM比較邏輯法是將正確的響應存儲在芯片內的ROM中,在測試的時候,將其與測試響應進行比較,但這種方法會因為占用太多的芯片面積而毫無實用價值。多輸入特征寄存器方法是將被測試電路中各節點的響應序列進行處理,得到與測試響應序列等長的特征字(Signature),然后與無故障電路節點的響應序列特征值進行比較,如果兩者相同,則說明電路正常,否則表明被測試電路有故障存在。跳變計數器法是通過比較輸出響應的跳變總數,來判斷被測試電路是否正常工作,因此需要存儲和比較跳變次數,從而使得所需要的存儲空間與測試時間都得到大幅度的降低。但是后面兩種方法是以犧牲故障覆蓋率為代價的。

安裝 Anaconda)

)