西工大數字集成電路實驗

練習六 加法器的設計

一、使用與非門(NAND)、或非門(NOR)、非門(INV)等布爾邏輯器件實現下面的設計。

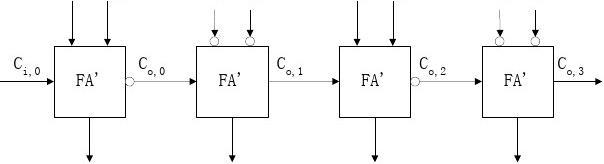

1、仿照下圖的全加器,實現一個N位的減法器。要求仿照圖1畫出N位減法器的結構。

ABABABAB0123

圖1 四位逐位進位加法器的結構

2、根據自己構造的N位減法器,寫出減法器最差情況下的延遲Tsub(用Tcarry,Tsum來表示)。并進一步嘗試用布爾器件的延遲Tnand、Tnor、Tinv來表示Tsub。

二、利用課本416頁介紹的鏡像加法器,實現16位的串行進位鏈路加法器。假設標準反相器(Wpmos=2 ,Wnmos=1)的本征延遲為Tp0=20ps,Tsum=120ps。(認為 1,并且所有的邏輯類型具有與反相器相同的本征延遲)

1、實現一個 16 位進位加法器,要求不進行進位鏈路中反相器的優化設置(其它延遲優化是要考慮的),要求加法器在輸入最差情況下的延遲小于3ns,試確定全加器中各管子尺寸。

2、實現一個16位進位加法器,要求優化進位鏈路中反相器設置,以達到最優的進位鏈路延遲,要求加法器在輸入最差情況下的延遲小于3ns,試確定全加器中各管子尺寸。

VDD

VDD

A

"0"-Propagate

Ci

"1"-Propagate

A

B

A

Generate

B

B

Ci

AB

B

B

Kill

A

Co

A

BVDD

Ci

ABCiSCi

24 transistors

提示:假設出關鍵路徑中相關門的尺寸系數。

)

![洛谷P3273 [SCOI2011] 棘手的操作 [左偏樹]](http://pic.xiahunao.cn/洛谷P3273 [SCOI2011] 棘手的操作 [左偏樹])