Debug與禁止優化

Debug模式是調試模式,會有很多冗余的調試代碼,供開發者調試程序使用。

VS是默認使用Debug模式的,我使用的是VS 2017。

在Debug模式下,是默認開啟禁止優化的,我們來查看一下

- 在左側源文件的

main.c處右鍵單擊,選擇屬性

- 找到C/C++下的優化

可以看到,默認是禁用優化。

Release與不同等級的優化

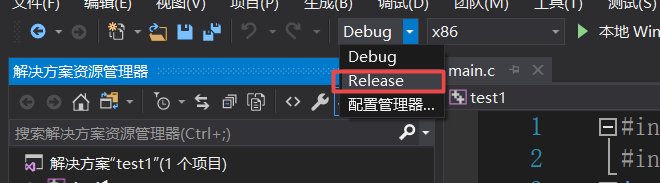

首先切換到Release模式

再查看一下優化

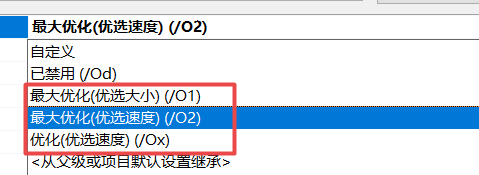

可以看到,默認優化方式是O2。

打開下拉菜單

可以看見有三種優化方式,這個你是可以自己選擇的。

Debug與Release的區別

- Debug是調試模式,僅供開發者調試使用,不能作為產品發布

- Release是發布模式,生成的可執行文件可以作為產品發布

Release中三種優化模式的區別

發布的產品,不同優化級別有所區別

- O1:這個模式下,文件大小最小,速度比O2慢

- O2:這個模式下,速度最快,文件大小比O1大

- Ox:這個模式下,兼顧文件大小與速度,可能犧牲兼容性

備注:這只是大致的含義,不包含細節,具體細節請閱讀專業文檔。

使用反匯編對比這幾種方式

VS 2017 查看反匯編

Debug與Release的區別

如果要將中文翻譯成英文,有兩種方式

- 直譯

- 意譯

將高級語言翻譯成匯編語言,也有兩種方式

- 直譯:Debug

- 意譯:Release

Debug是直接將你寫的高級語言語法進行翻譯,基本上是按照你的書寫格式進行的,而Release則是自己寫的,但是含義完全一樣,這里和語言的意譯不同,是真的完全一樣。

test與跳轉指令(je jle jge jg jl……)組合的含義)

)

)

)