0 前言

本文將會以R-S鎖存器為例,引出鎖存器的核心和本質,之后再帶你構建更多類型的鎖存器,你能夠:

- 感受到由淺入深的學習方式

- 體會到掌握核心本質的快感

- 深刻理解核心套外殼的設計理念(產品迭代1.0–>2.0–>3.0)

同時,強烈建議你使用logisim軟件,邊看文章邊實踐,這樣能夠加深理解,這款軟件半小時即可入門,圖形化的操作方式,簡單又好用。

核心套外殼的思想,能夠幫助你【區分表象與本質,抓住問題的核心,理解設計理念!】

1 確立一個目標,提升你的認知效率

點進這篇文章,我想你是非常想要學會鎖存器相關知識的,那么,為了進一步提高你的認知效率,我先給你定下一個目標,帶著這個目標,再去一步一步尋找和學習相關知識,并且,你應該使用軟件,在實踐中學習,這么一來,你的認知效率將會翻倍。

我們都知道計算機的硬盤和內存,我們也知道,這些設備能夠存儲數據,并且這些數據是二進制信息,也就是0、1的各種排列組合,那么,你是否曾經產生疑惑,4GB、16GB,乃至1TB的信息,是如何被存儲的?

今天讓我們來解答這個問題,我們先不管1TB的信息如何存儲的,今天我們就談:如何存儲1位二進制信息,也就是如何存儲一個0或者一個1。

我們需要制作一個器件,能夠存儲一個0或者一個1。這個器件,就是R-S鎖存器,在通電狀態下,它能夠鎖住(存儲)1個二進制位,也就是1 bit。

讓我們來一步步地揭開它的神秘面紗吧!

2 R-S鎖存器

2.1 基本結構

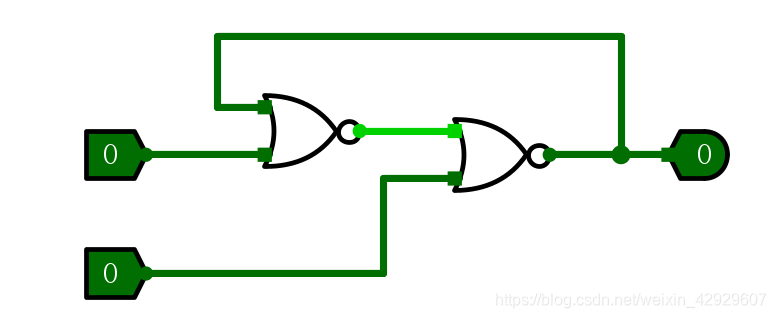

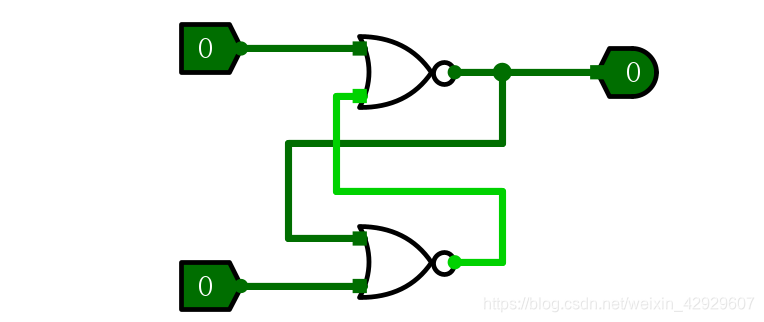

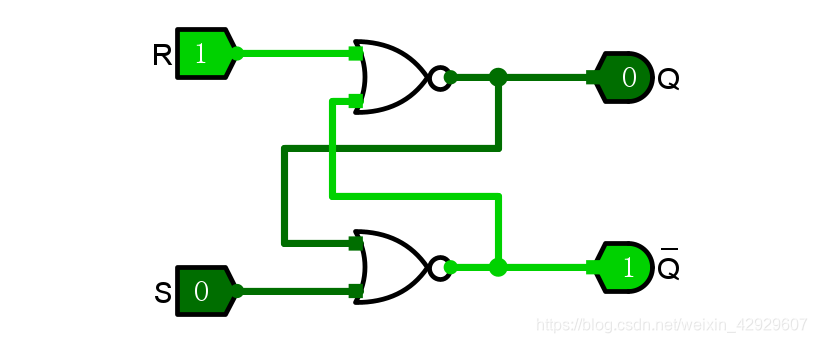

我們來看一下他=它的結構,通常有兩種描述方法:

- 描述1

- 描述2

這兩種結構完全一樣,只不過放置的方式不一樣,通常我們會采用描述2的方式。

可以看到,R-S鎖存器包含了2個或非門,2個輸入端口,1個輸出端口,這個結構真的簡單至極。

如果你學過一點數字邏輯的知識,也許你會跟我爭辯,R-S鎖存器不是2個輸出端口嗎?先按照我說的繼續往下聽,之后會解釋的。

2.2 如何鎖住1-bit

那么,這樣一個結構,如何鎖住(存儲)1-bit的?

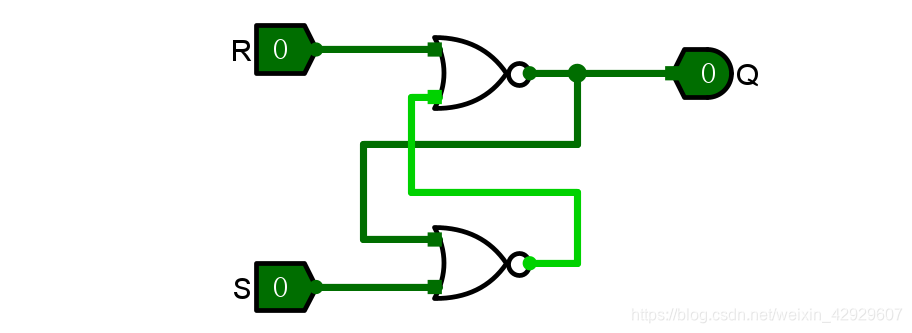

為了方便描述,我們先為上面的結構命名一下。

- 2個輸入端口分別命名為

R和S - 1個輸出端口被命名為

Q

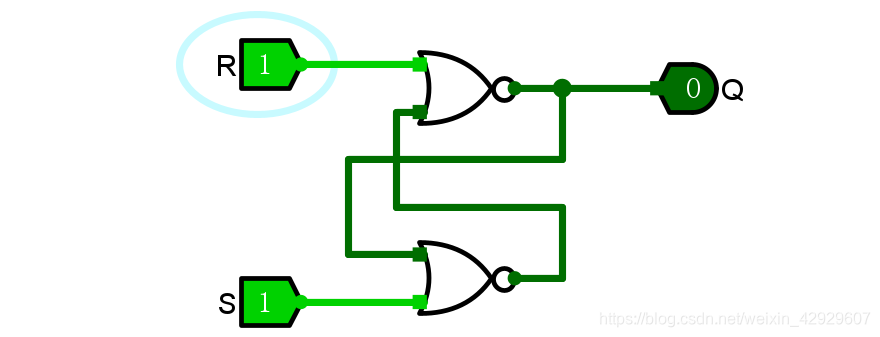

讓我們記住這個初始狀態

| R | S | Q |

|---|---|---|

| 0 | 0 | 0 |

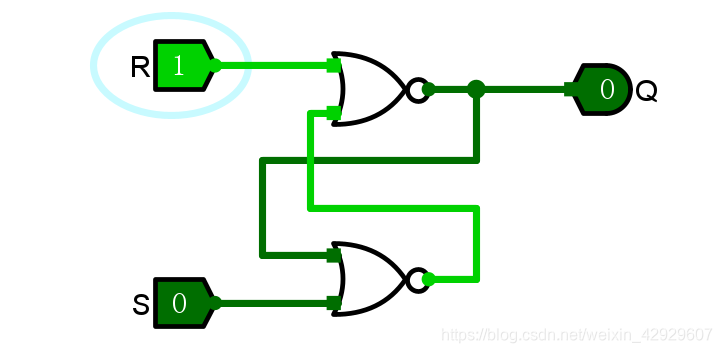

然后,我們將R置為1。

你會發現,此時的狀態是

| R | S | Q |

|---|---|---|

| 1 | 0 | 0 |

我們再將S置為1

此時的狀態是

| R | S | Q |

|---|---|---|

| 1 | 1 | 0 |

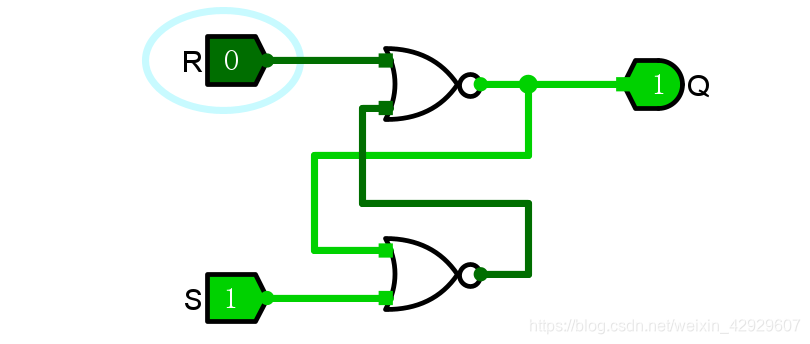

我們再將R置為0

此時的狀態是

| R | S | Q |

|---|---|---|

| 0 | 1 | 1 |

我們再將S置為0

此時的狀態是

| R | S | Q |

|---|---|---|

| 0 | 0 | 1 |

接下來,我們匯總一下上面的幾種狀態

| R | S | Q |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

| 0 | 1 | 1 |

| 0 | 0 | 1 |

我們可以看到,同樣是0,0,但是輸出卻可能是0或1,這也就意味著,這不是組合邏輯,而是時序邏輯,輸入的順序會影響結果。

同時,我們再繼續進行實驗可以發現(此處請自行完成實驗,親自體驗以下結論)

- 一旦置

R = 1,S = 0,S不變的情況下,無論R如何改變,Q都等于0 - 一旦置

R = 0,S = 1,R不變的情況下,無論S如何改變,Q都等于1 - 當

R = 0,S = 0的時候,Q的結果,取決于上一個狀態。如果之前是因為R = 1,S = 0導致的Q = 0,則現在的Q依然0;如果之前是因為R = 0,S = 1導致的Q = 1,則現在的Q依然為1 - 一旦置

R = 1,S = 1,Q一定等于0,這種情況與我們的目標不符,我們需要禁止它

因此,我們得到了R-S鎖存器特性表

| R | S | Q |

|---|---|---|

| 0 | 0 | 和之前狀態的Q一樣 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 禁止使用 |

我帶你分析完了這些,我們改回看主題,看一下它是如何鎖住1-bit的。我們看一下剛才描述的狀態:

- 一旦置

R = 1,S = 0,S不變的情況下,無論R如何改變,Q都等于0 - 一旦置

R = 0,S = 1,R不變的情況下,無論S如何改變,Q都等于1

我們觀察后面加粗的句子,不難看出,1個二進制數被“鎖在”了器件中,這也就是所謂的鎖存器,它在功能上,實現了存儲1個二進制位。

2.3 為什么可以鎖住1-bit

剛才,我們知道了R-S鎖存器能夠存儲1個二進制位,并且已經達成了目標,是的,我們成功存儲了1個二進制位,但是,這還不夠,我們應該保持好奇心,問一問自己,為什么能夠鎖住?

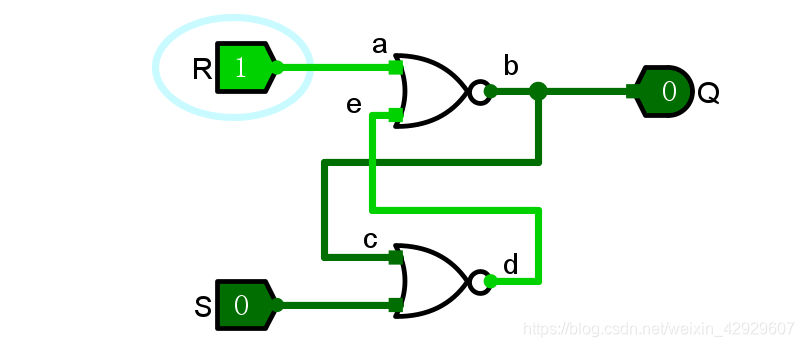

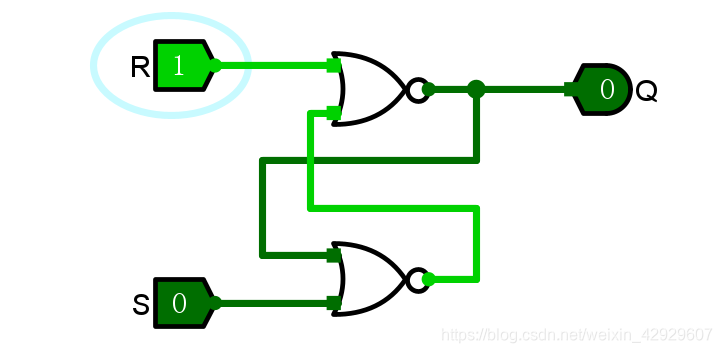

讓我們來分析一下R-S鎖存器的工作,以R = 1,S = 0為初態舉例。

下面是初態,并且我在幾個關鍵的地方做了標記。

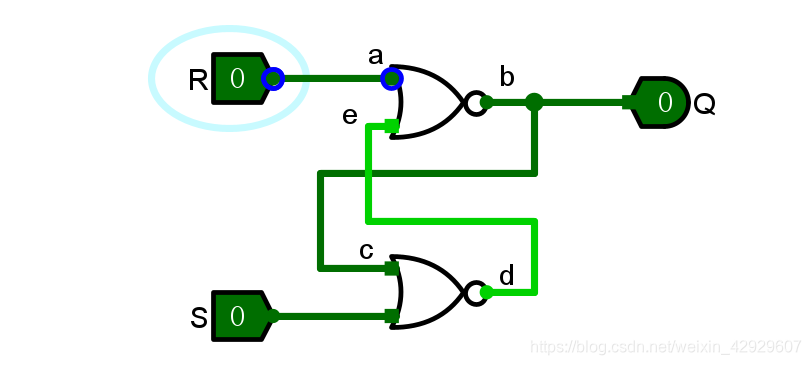

之后,我令R = 0,我們來逐步地分析一下,到底發生了什么。

首先,0信號傳到了a端,此時a = 0

然后,a和e進行或非運算,得到的結果傳到了b端,此時b = 0

然后b端的結果,反饋到了c端,c = 0;之后,可以得到d = 1;之后,d端的結果又反饋到了e端,可以得知,e = 1并沒有發生變化,就此,這個過程就穩定了下來,b端輸出到Q的數據也就是最終結果了。

我們梳理一下這個過程,在令R = 0之后,只有a端的數據變為了0,其他端口的數據均沒有變化,這樣一來,也就產生了鎖住數據的現象,產生這種現象的原因,是因為反饋回路的存在。

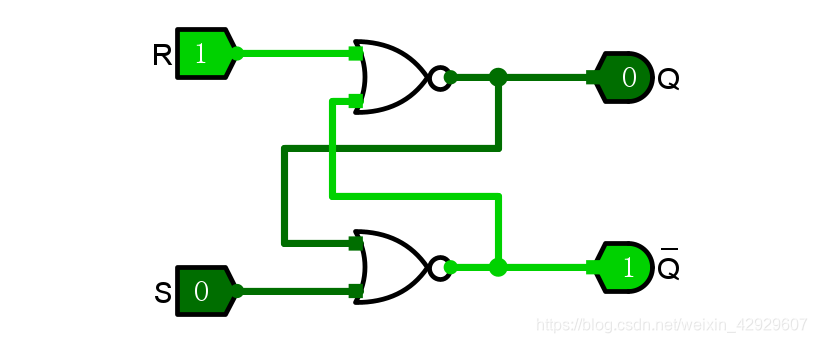

我們可以知道,bc鎖住了0,de鎖住了1,這二者正好相反,因此我們有時候也會將R-S鎖存器設計為下面的樣子,這樣可以獲得兩個一直相反的輸出結果

其中,上面讀作輸出Q,下面讀作輸出Q拔,二者的取值永遠相反,你也能夠理解,為什么之前我們禁止了R = S = 1的情況,因為這樣輸出就不相反了,與設計目標不符。

2.4 為什么叫“R-S鎖存器”

為什么這個器件被命名為R-S鎖存器呢?為什么不叫別的名字?

我們要知道,凡是命名,都有其含義,都能表達其意義,這樣的命名才有價值,R-S鎖存器也是如此。

它是英文名稱是:Set-Reset latch,有被稱為S-R Latch或者R-S Latch

我們來解釋一下

- R就是

reset,重置、復位的意思,所以,當僅有它為1的時候,輸出Q = 0 - S就是

set,設置、置位的意思,所以,當僅有它為1的時候,輸出Q = 1 - Latch,鎖存器的意思,它能夠存儲1個二進制位

2.5 R-S鎖存器的功能

R-S鎖存器,也可以被稱為置位復位觸發器,我想你明白這個含義了,現在我們只是總結一下。

| R | S | Q | 說明 |

|---|---|---|---|

| 0 | 0 | 和之前狀態的Q一樣 | 保持 |

| 0 | 1 | 1 | 置位 |

| 1 | 0 | 0 | 復位 |

| 1 | 1 | 禁止使用 | 非法 |

3 鎖存器的核心和本質

通過R-S鎖存器,我們可以理解鎖存器的本質,掌握一類鎖存器的核心,這才是我們要關注的重點內容,至于鎖存器的設計和樣子,不是最重要的,那只不過是在核心的基礎之上,套上了外殼,從而讓其擁有更廣泛的的應用。

關于核心套外殼,我有必要進一步解釋一下,我們知道,計算機領域又很多核心部件,例如CPU,這是被外國壟斷的高科技器件,它是核心,而計算機其他的部分,內存、硬盤、顯示器等等,都是外殼,我們給核心套上不同的外殼,就構成了不同的計算機,能夠進行不同的應用;又比如富士康代工廠,他們做的就是給核心套上外殼的工作。

我想你應該能夠理解核心的重要性了。

那么鎖存器的核心是什么?

這就是鎖存器的核心,原理方面,我之前已經詳細講解過,不再贅述,但是希望你認真對待那些看似簡單容易的知識,因為它們可能蘊含著擁有無窮力量的核心思想。

3.1 核心套外殼的產品

那么核心套外殼之后,有那些產品呢?有很多,例如:

- 基本R-S鎖存器

- 門控R-S鎖存器

- D型鎖存器

甚至,由此核心,還可以構成各種各樣觸發器。

需要注意的是,這些外殼,并不是死板的,你完全可以根據需要,靈活地變化他們,不必拘泥于某種特定的形式,不過前提是,變化之后的產品真的很好用,否則,你更應該直接使用封裝好的產品。

后面的小節,我會為你詳細講解核心套外殼的產品。

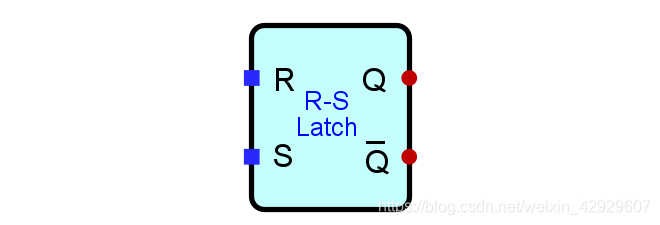

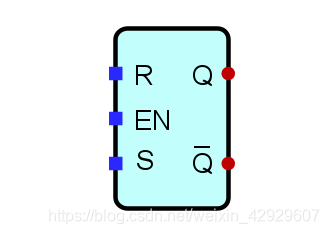

3 外殼一:基本R-S鎖存器

嘿!一個新的目標出現了,之前我們為了存儲1位數據,制作了R-S鎖存器,現在,我們需要存儲一位數據,并能夠讓他輸出存儲的數據,以及和存儲數據互補(0和1在二進制下是互補的)的數據。

這個產品我不再分析,因為你之前見過了:

現在我們將其封裝一下,讓它更像一個產品。

至于它的功能,我想你已經知道了,基本R-S鎖存器,增加的外殼是一個輸出端口。

4 外殼二:門控R-S鎖存器

現在,新的任務又下達了,我們的基本R-S鎖存器,可以隨意被使用,這可不好,現在我們需要增加一個開關,只有開關打開的時候,基本R-S鎖存器才可以被使用。

我們考慮一下,看看上面封裝好的基本R-S鎖存器,我們可以加的外殼是:在進入R、S輸入端口之前,增加2個與門,這樣就可以控制輸入信號的有效、無效。

你可以試一試這個電路,這就是門控R-S鎖存器。

名稱的含義,門控,就是加一個開關,它被稱為使能端(Enable terminal),簡寫EN。

我們將它封裝一下:

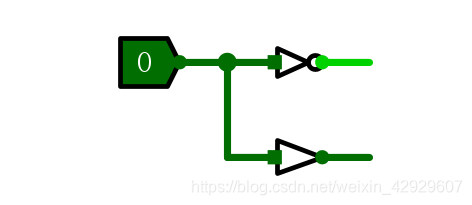

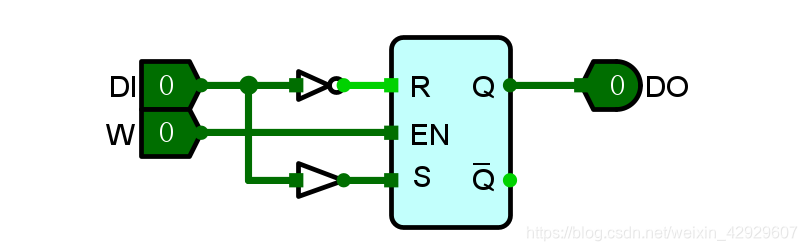

5 外殼三:D型鎖存器

全新的任務

- 徹底禁止掉

R = S = 1的情況,對于任何輸入的數據,使其,不可能存在這種情況,保證安全,完全避免非法狀態。 - 讓這個器件能夠實現數據0和1的寫入,并且能夠控制是否寫入。

我們由門控R-S鎖存器開始思考,既然R和S不能相同,那就只能相反了,這樣雖然會舍棄掉R = S = 0的情況,不過,既然這種情況會與上一個狀態相同,而上一個狀態R和S一定相反,所以,舍棄掉又有何妨呢?因此,我們的思路就有了,讓R和S永遠相反,我們怎么做呢?我想你應該知道了,使用1個輸入端和1個非門!

就像下面這樣,加緩沖器是為了讓數據流動時間和加了非門的線路同步

那么第二個目標如何達成?顯然我們已經完成了一部分,1個輸入端和1個開關我們已經有了,我們只需要,去掉Qbar即可。

你會發現,這里有了較大的變化,我的節奏加快了,如果你前面認真實踐了的話,我想你是適應這種變化的。

我來解釋一下這些變化

- 為了達成目標,我們要讓R和S的值一直相反,因此我們加了一個非門和緩沖門,用一個輸入端操控它,注意,不要將非門放錯位置,你仔細想一下會明白怎么放置的(舉一個例子就好,例如

DI = 0的時候,如何讓DO = 0)。 - 我們將開關作為寫入端

- 我們不使用Qbar端口

我來解釋一下端口名稱的變化

- DI:數據輸入端,可以控制輸入的數據是0還是1

- DO:數據輸出端,可以讀取存儲在鎖存器中的數據

- W:寫入端,可以控制是否將數據寫入端的數據寫入到鎖存器中

- 若

W = 1,則DI中的數據會被寫入到鎖存器中,并且存儲起來,此時,DO讀取的數據是和DI一樣的 - 若

W = 0,則DI中的數據不會被寫入到鎖存器中,此時,DO將會讀取鎖存器中存儲的數據,與DI的數據無關

- 若

我們封裝一下這個器件

擴展內容:這也是我們現在會常用的鎖存器類型,我們通常會使用Verilog HDL實現它

module moduleName (input wire w,input wire Din,output reg Dout);always @(w or Din)beginif(w)Dout <= Din;elseDout <= Dout;endendmodule關于Verilog HDL的知識,你可以自行搜索,如果你不感興趣,這部分內容可以忽略。

6 一點注意

這里器件的存儲,不是永久保存,因為它的本質是電子器件,電是難免會泄露的,我們還需要對其做一些補充,這里不深入展開。

另外,對于門控R-S鎖存器中的開關,也被稱為保持位(Hold That Bit),當它為0的時候,無論R、S怎么變,鎖住的數據也不會改變,這也就是所謂的保持。

7 思考題&預告

我留下思考題和預告,請你仔細思考并認真實踐

- 最初,我們使用或非門構造了R-S鎖存器,事實上,與非門一樣可以完成這件事情,我在3.1節提過,產品的設計的不能死板,它是靈活的,請你思考一下如何設計。

- 請思考一下,具體講解的幾種外殼,有沒有感受到,外殼的設計也又核心思想支撐? 之后我們會揭秘。

- 核心套外殼的產品,也完全可以作為新的核心,為他們再賦予外殼,做出更多有用的產品。

- 我們的目標是構建一個RAM存儲器,以R-S為鎖存器的RAM產品,隨著時代的發展,它的性能提升進入了瓶頸期,這個時候,人們的最佳選擇是優化核心,這也由RAM存儲器,轉變成了SRAM、DRAM等類型的存儲器,這些后面也會提及(也可以按照此思路,去想一想:算盤–>計算器–>電子計算機–>量子計算機)。

test與跳轉指令(je jle jge jg jl……)組合的含義)

)

)

)