前提

8088有兩個組態:

最大組態和最小組態,通過引腳MN/MX*的電平決定組態。(*表示低電平有效)

兩種組態沒有本質區別。

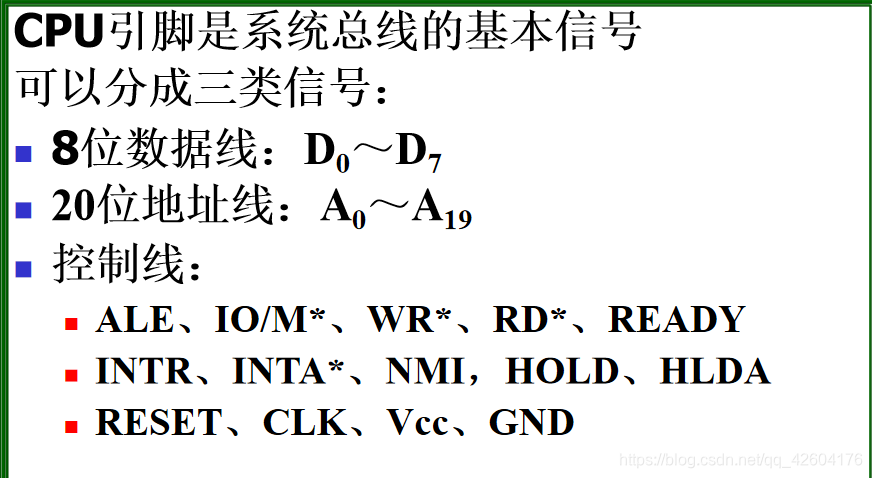

8088的引腳:

引腳可分為下面幾種類別:

1、數據和地址引腳

2、讀寫控制引腳

3、中斷請求和響應引腳

4、總線請求和響應引腳

5、其它引腳

1.數據和地址引腳

AD7~AD0(Address/Data):T1時輸出存儲器或I/O端口的低8位地址A7~A0,其他時間傳送8位數據D7~D0 。

性質:分時復用 // 雙向 //三態

A15~A8(Address):提供全部20位地址中的中間8位地址A15~A8

性質:地址引腳 // 輸出 //三態

A19/S6~A16/S3(Address/Status):T1時訪問存儲器的高4位地址A19~A16(或T1時訪問I/O端口時全部置零),其他時間輸出狀態信號S6~S3。

性質:分時復用 // 輸出 //三態

2. 讀寫控制引腳

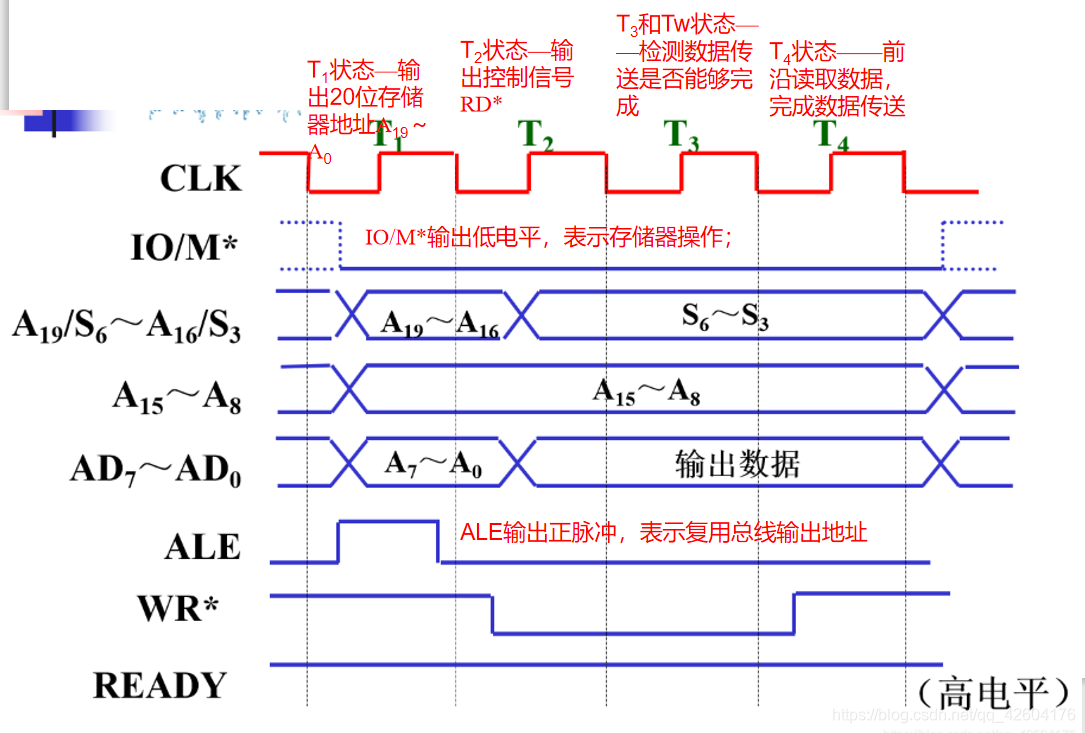

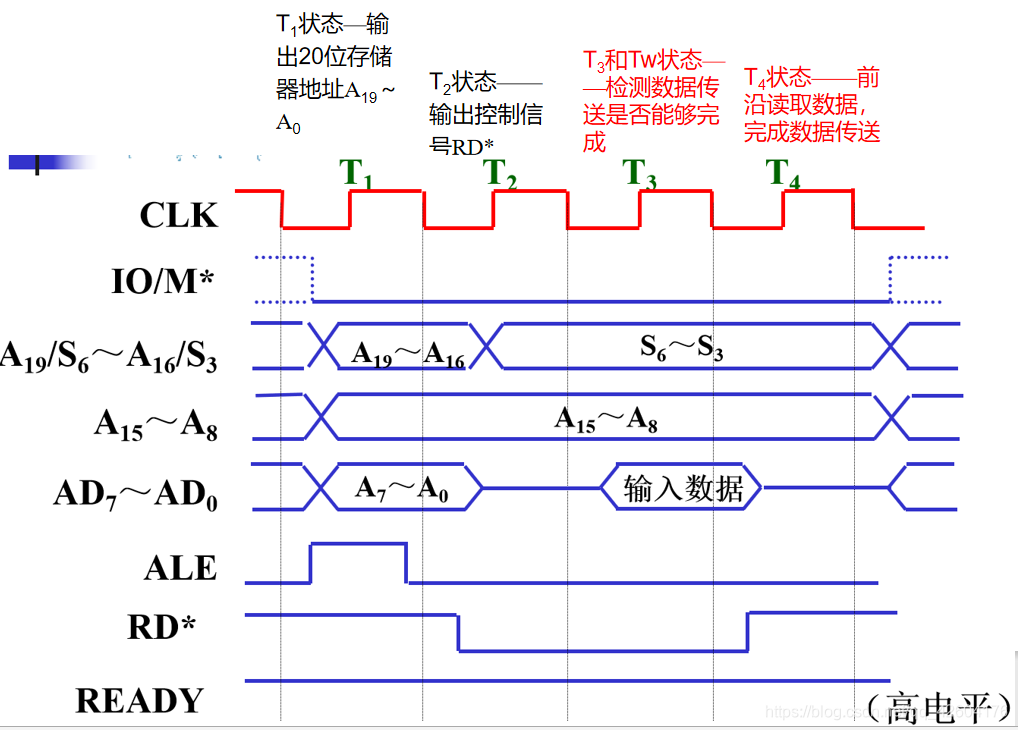

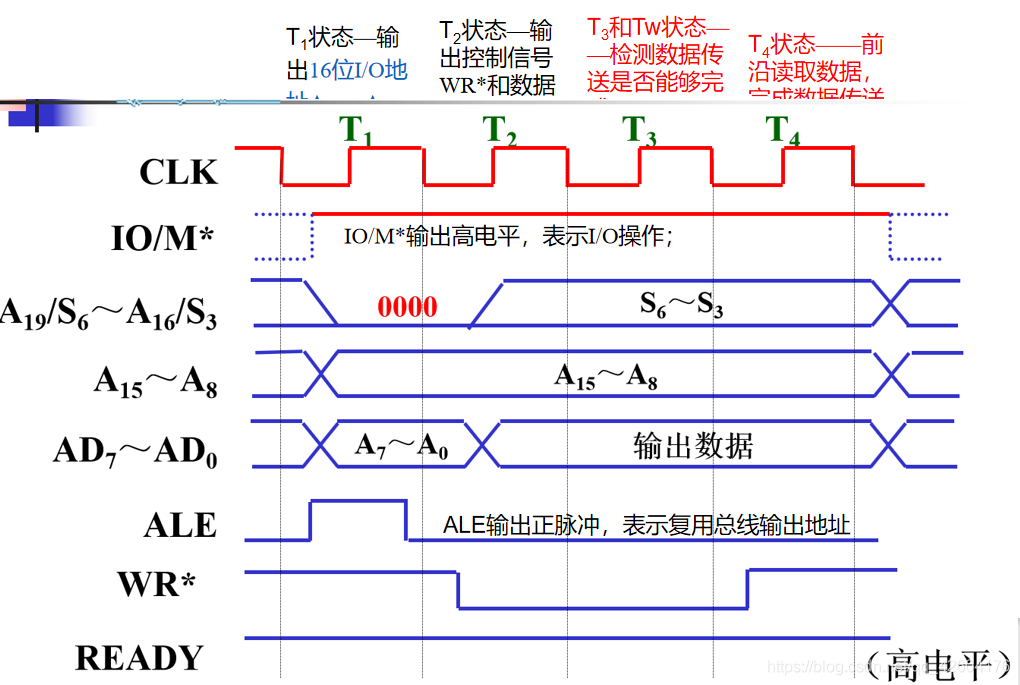

ALE(Address Latch Enable):高電平時將AD7~AD0和A19/S6~A16/S3地址鎖存

性質:地址鎖存允許,輸出、三態、高電平有效

IO/M*(Input and Output/Memory) :高電平CPU訪問IO,A15~A0提供地址;低電平訪問存儲器,A19~A0提供地址

性質:I/O或存儲器訪問,輸出、三態

WR*(Write) :有效時,表示CPU正在寫出數據給存儲器或I/O端口

性質:寫控制,輸出、三態、低電平有效

RD*(Read):有效時,表示CPU正在從存儲器或I/O端口讀入數據

性質:讀控制,輸出、三態、低電平有效

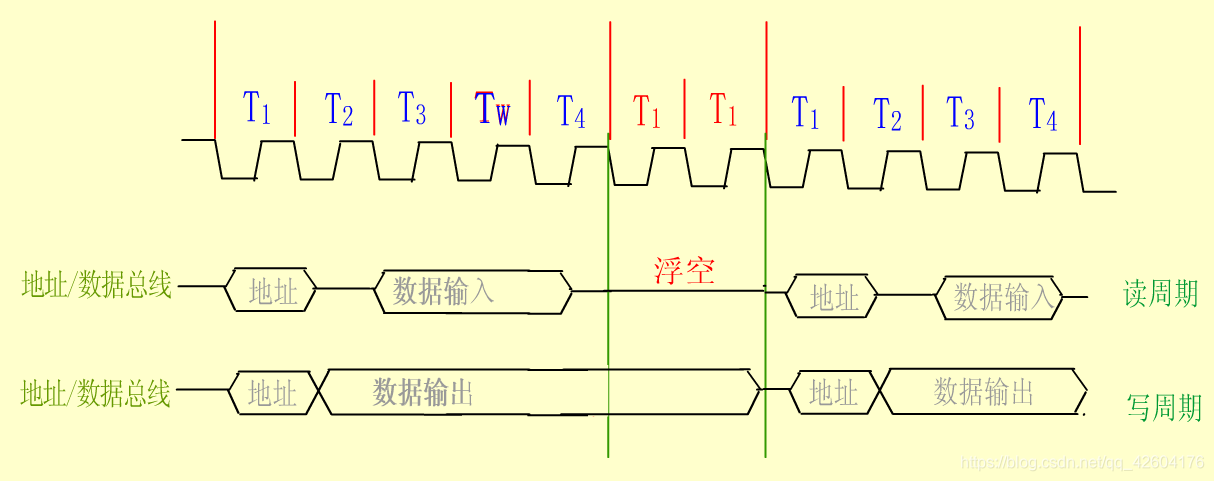

四種基本的總線周期

==READY ==:T3的前沿測試該引腳,高有效直接進入T4,低無效插入等待周期Tw。(無論CPU處在操作周期還是等待周期都進行此操作)

性質:存儲器或I/O口就緒,輸入、高電平有效

DEN*(Data Enable) :有效時,表示當前數據總線上正在傳送數據,可利用他來控制對數據總線的驅動

性質:數據允許,輸出、三態、低電平有效

DT/R*(Data Transmit/Receive):高電平時數據自CPU輸出(發送)低電平時數據輸入CPU(接收)

性質:數據發送/接收,輸出、三態

SS0*(System Status 0):狀態輸出信號

CPU八種工作狀態

3. 中斷請求和響應引腳

INTR(Interrupt Request) :有效時,表示請求設備向CPU申請可屏蔽中斷;該請求的優先級別較低,并可通過關中斷指令CLI清除標志寄存器中的IF標志、從而對中斷請求進行屏蔽

性質:可屏蔽中斷請求,輸入、高電平有效

INTA*(Interrupt Acknowledge) :有效時,表示來自INTR引腳的中斷請求已被CPU響應,CPU進入中斷響應周期

性質:可屏蔽中斷響應,輸出、低電平有效

NMI(Non-Maskable Interrupt) :該請求的優先級別高于INTR,并且不能在CPU內被屏蔽;用于系統發生緊急情況時

性質:不可屏蔽中斷請求,輸入、上升沿有效

有效時,表示外界向CPU申請不可屏蔽中斷

4. 總線請求和響應引腳

HOLD :有效時,表示總線請求設備向CPU申請占有總線

性質:總線保持(即總線請求),輸入、高電平有效

HLDA(HOLD Acknowledge):有效時,表示CPU已響應總線請求并已將總線釋放

此時CPU的地址總線、數據總線及具有三態輸出能力的控制總線將全面呈現高阻,使總線請求設備可以順利接管總線

5. 其它引腳

CLK(Clock)

性質:時鐘輸入

Vcc

性質:電源輸入,向CPU提供+5V電源

GND

性質:接地,向CPU提供參考地電平

MN/MX*(Minimum/Maximum):接高電平時,8088引腳工作在最小組態;反之,8088工作在最大組態

性質:組態選擇,輸入

TEST* :不用管它,測試引腳用的

性質:測試,輸入、低電平有效

引腳小結

四種基本總線周期詳解

存儲器寫總線周期

存儲器讀總線周期

I/O寫總線周期

I/O讀總線周期

插入等待狀態Tw

目的:同步時序通過插入等待狀態,來使速度差別較大的兩部分保持同步

1.在T3的前沿檢測READY引腳是否有效

2. 如果READY無效,在T3和T4之間插入一個等效于T3的Tw ,轉1

3. 如果READY有效,執行完該T狀態,進入T4狀態

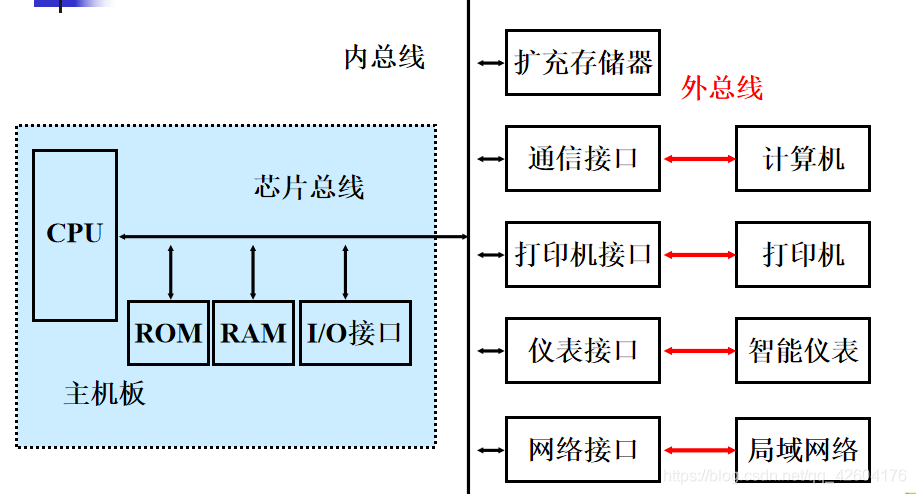

總線概況

)

)

)

方法與示例)