0x00?回顧:AND/OR/NOT 邏輯的特性

AND:與門可以具有兩個或更多的輸入,并返回一個輸出。當所有輸入值都為 1 時,輸出值為 1。如果輸入值中有任何一個為 0,則輸出值為 0。

OR:或門可以具有兩個或更多的輸入,并返回一個輸出。如果輸入值中至少有一個為 1,則輸出值為 1。如果所有輸入值都為 0,則輸出值為 0。

NOT:非門具有一個輸入和一個輸出。當輸入值為 1 時,輸出值為 0;當輸入值為0時,輸出值為1。

晶體管級邏輯門 AND/OR/NOT 的結構:

0x01?扇出的概念(Fan-out)

扇出?(fan-out) 是一個定義單個邏輯門能夠驅動的數字信號輸入最大量的專業術語。

扇出即輸出可從輸出設備輸入信號的電路的數量。它的英文含義是“分散”。扇出的大小表示一個輸出被多個其他邏輯門的輸入使用。如果刪除太大,電路可能會受損或信號無法正確傳遞,因此需要解決這個問題。可以通過將一個信號分割為兩個部分進行處理或創建緩沖區等方法來減小扇出的影響。

0x02?傳播延遲(Propagation Delay)

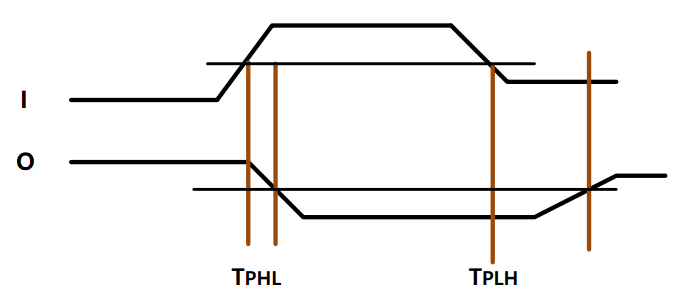

傳播延遲 (Propagation Delay) 是指邏輯電路從接收輸入信號到產生輸出結果所需的平均時間。它受邏輯門的數量及其延遲時間的影響,表示如下:

其中,(Propagation Delay)是傳播延遲時間,

(Propagation delay time from High to Low)是輸出響應輸入信號從邏輯 1 變為邏輯 0 所需的時間,

(Propagation delay time from Low to High)是輸出響應輸入信號從邏輯 0 變為邏輯 1 所需的時間。

延遲時間隨著通過門數的增加而增加,因此在設計邏輯電路時必須牢記這一點,以提高效率。

0x03?Verilog 中的 task 和 function

Verilog 中的任務 (task) 和函數 (function) 是用來減少代碼重復的關鍵字,就像 C 語言中的函數一樣。換句話說,在具有大量相同行為的項目中,任務和函數可以用來簡化代碼。任務和函數都可以有局部變量、全局變量、寄存器、時間變量、整數、實數等,但不能有導線。 它們也只包含行為語法,沒有始終和初始語法。具體區別如下:

① task:

- 可以使用 task 和 endtask 將開始和結束包圍起來進行聲明。

- 可以包含延遲、時序和事件控制語句。

- 可以有一個或多個輸入、輸出、input 等參數,也可以沒有任何參數。

- 內部可以同時調用任務(task)和函數(function)。

- 如果不使用時間延遲功能,可以進行綜合。

- 可以在非零仿真時間下執行。

- 可以通過命令語句調用,但不能在表達式內部使用。

② function:

- 可以使用 "function" 和 "endfunction" 將開始和結束包圍起來進行聲明。

- 不能包含延遲、時序和事件控制語句。

- 至少有一個以上的輸入,并且只有一個返回值。

- 內部只能調用函數(function)。

- 可以進行綜合,并用于組合電路建模。

- 總是在仿真時間為 0 時執行。

0x04?FPGA 的工作原理

描述FPGA的工作原理:使用Vivado和Verilog語言驗證FPGA工作時,可以使用以下程序。

Verilog 編碼(Verilog Coding)

在 Vivado 中編寫 Verilog 設計源代碼和測試平臺代碼來控制門的行為。在這種情況下,變量值中的 0 或 1 可以作為 FPGA 中的 "開關 "來實現。(開關打開 = 1,開關關閉 = 0,等等)。

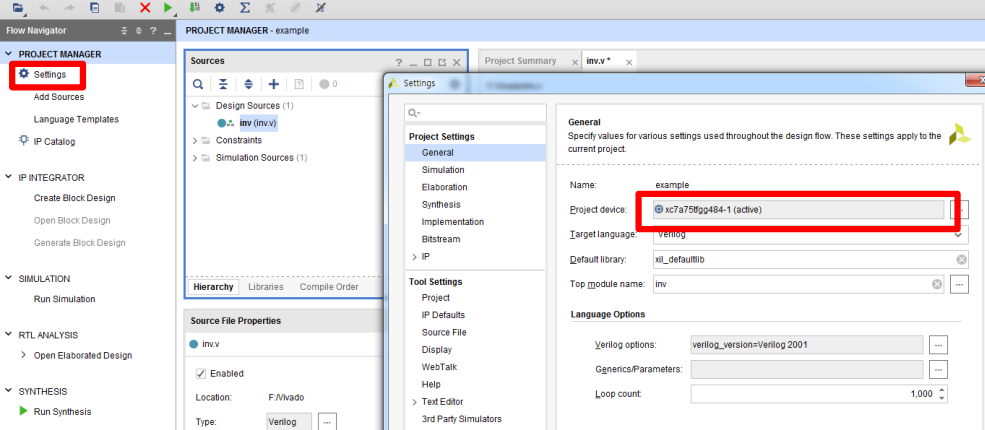

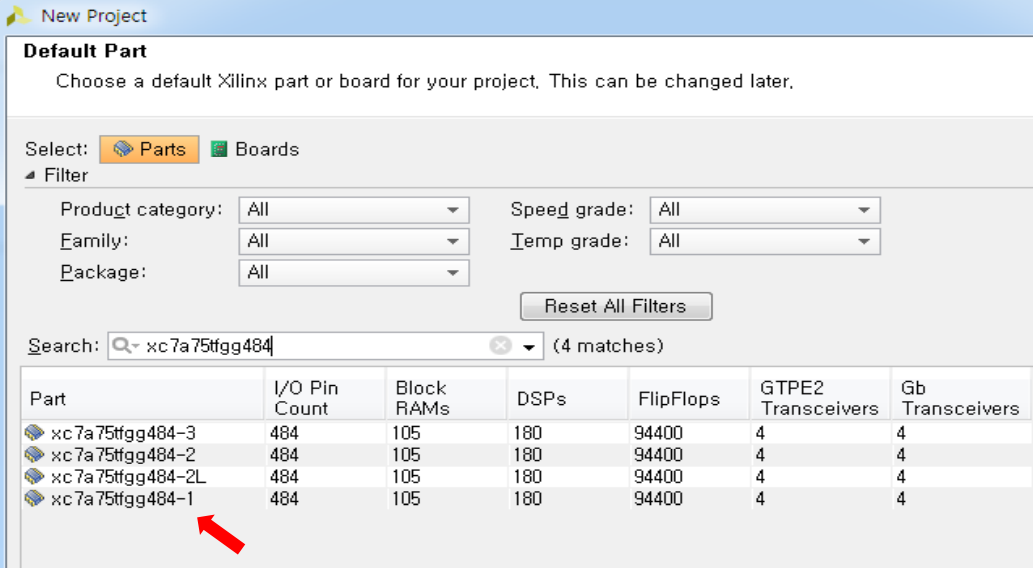

設備分配(Device assignment)

要操作FPGA,需要為項目分配相應的器件。在 Vivado 中,這可以在 Project Manager > Settings > Project device 菜單中完成,設備應為 xc7a75tfgg484-1 (Artix7)。Artix-7 FPGA 是 FPGA 器件,可為邏輯、信號處理、嵌入式存儲器、LVDS I/O、存儲器接口和收發器提供優化的性能。

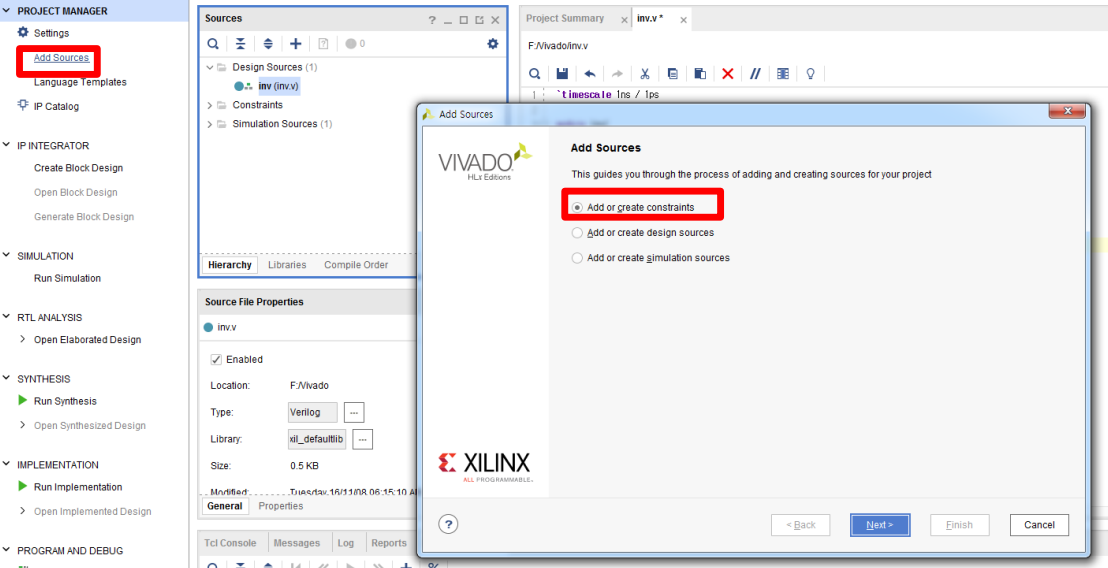

引腳分配(Pin assignment)

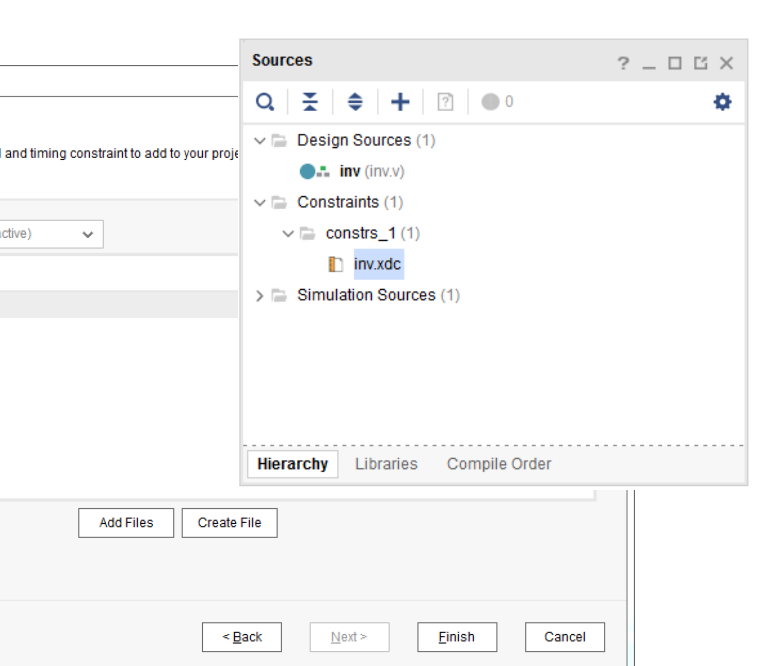

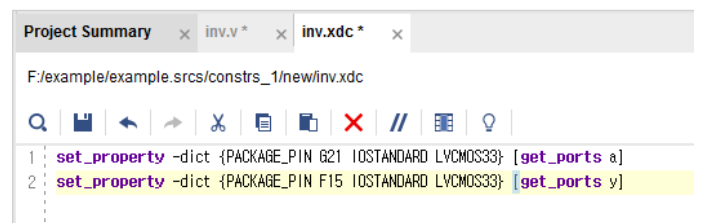

引腳只是 Verilog 代碼中的輸入和輸出變量。您可以通過 Vivado 的 Project Manager > Add Sources > Add或create constraints > Create File 創建一個 .xdc 文件,并從 FPGA 引腳列表和Verilog 源的端口鏈接您要分配的引腳。舉個例子:

set_property -dict {PACKAGE_PIN G21 IOSTANDARD LVCMOS33} [get_ports a] [get_ports a] [get_ports a] [get_ports a [get_ports a]綜合/實現(Synthesis/Implement)

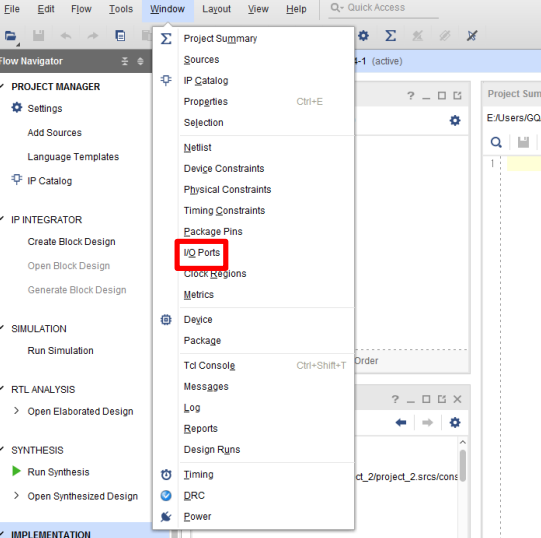

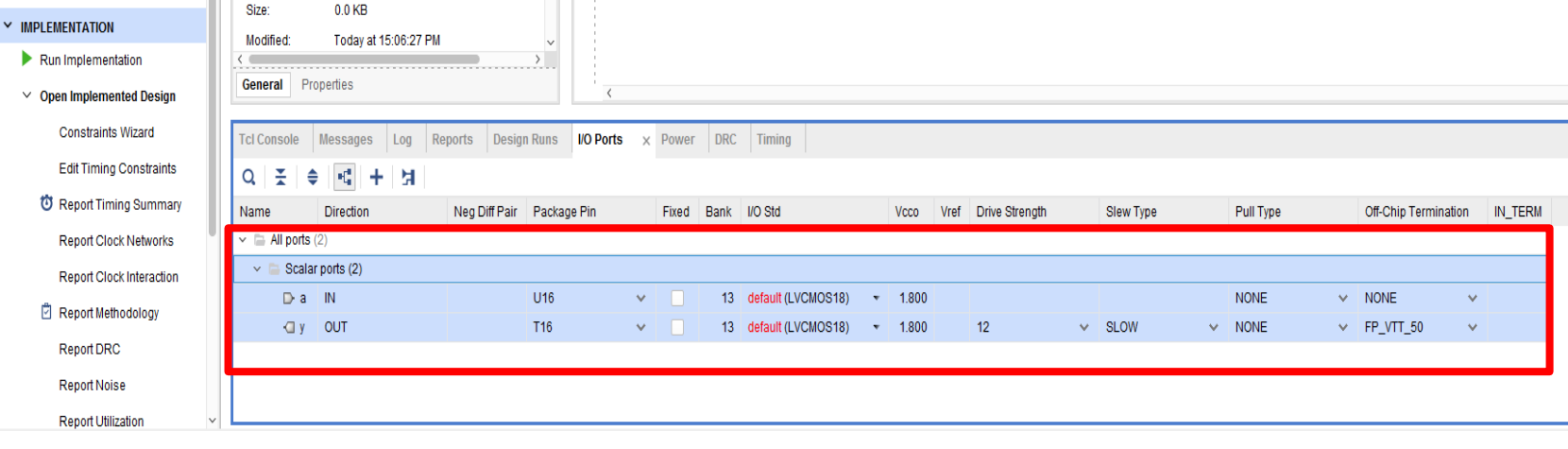

在 Vivado 中,可以通過 Synthesis > Run Synthesis、Implementation > Run Implemented > Open Implemented Design 創建綜合設計和布線設計。

器件配置(Device Configuration)

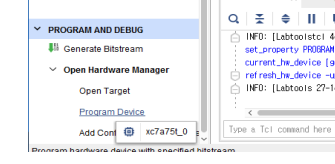

設備配置可以通過 Vivado 中的“編程和調試”>“生成比特流”>“打開硬件管理器”來完成。

FPGA 行為

在 Vivado 中,單擊 Program and debug > Open Hardware Manager > Open Target > Auto Connect,然后在 Project[title] > Project[title]_runs > impl_1 文件夾中添加 debug_nets.ltx 文件。

Program and debug > Program Device > Debug probes file > Select the debug_nets.ltx file added above and specify the Program device(xc7a75t_0) to connect to the external FPGA device。

0x05 具體操作過程

Device assignment:

Device assignment → Device : xc7a75tfgg484

Pin assignment

鏈接你希望在 FPGA pin list 中分配的 Pin 和 Verilog 源端口:

set_property -dict {PACKAGE_PIN G21 IOSTANDARD LVCMOS33} [get_ports a]

set_property -dict {PACKAGE_PIN F15 IOSTANDARD LVCMOS33} [get_ports y]?

?

Synthesis / Implementation:

Device configuration:

我的板子比較老,是 FPGA Starter Kit Ⅲ:

初始化狀態如下所示:

Open Target →??點擊 auto connect,自動連接:

選擇?Program Device:

🚩 輸出結果演示:

📌 [ 筆者 ]? ?王亦優

📃 [ 更新 ]? ?2022.9.20

? [ 勘誤 ]?? /* 暫無 */

📜 [ 聲明 ]? ?由于作者水平有限,本文有錯誤和不準確之處在所難免,本人也很想知道這些錯誤,懇望讀者批評指正!| 📜 參考資料? Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |

)

)