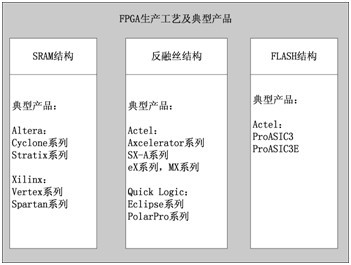

1.生產FPGA的廠家有:

ALTERA

XILINX

ATCEL

Lattice

ps:

Altera和Xilinx主要生產一般用途FPGA,其主要產品采用SRAM工藝

Actel主要提供非易失性FPGA,產品主要基于反熔絲工藝和FLASH工藝

ps: 熔絲,顧名思義:把絲熔掉,反熔絲技術恰相反,原來斷接的點在燒錄之后,短接上了,這種短接是永久性的!

反熔絲是一次性!!

2.FPGA是由存放在片內RAM中的程序來設置其工作狀態的,工作時需要對片內的RAM進行編程,在掉電時FPGA變成一個白片!!

由于LUT主要適合SRAM工藝生產,所以目前大部分FPGA都是基于SRAM工藝的,而SRAM工藝的芯片在掉電后信息就會丟失,一定需要外加一片專用配置芯片,在上電的時候,由這個專用配置芯片把數據加載到FPGA中,然后FPGA就可以正常工作,由于配置時間很短,不會影響系統正常工作。

對此有不同的編程配置方法:

并行主模式為一片FPGA加一片EPROM的方式;

主從模式可以支持一片PROM編程多片FPGA;

串行模式可以采用串行PROM編程FPGA;

外設模式可以將FPGA作為微處理器的外設,由微處理器對其編程。

3.FPGA與CPLD的辨別和分類:

將以乘積項結構方式構成邏輯行為的器件稱為CPLD;

將以查表法結構方式構成邏輯行為的器件稱為FPGA。

4.FPGA 內部三個基本的資源:

CLB可編程邏輯功能塊、IOB可編程輸出輸入塊、可編程內部互連線資源。

5.FPGA實現功能的方式:

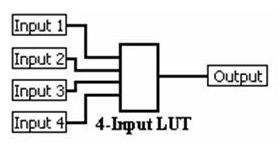

PLD/FPGA開發軟件會自動計算邏輯電路的所有可能的結果,并把結果事先寫入RAM,這樣,每輸入一個信號進行邏輯運算就等于輸入一個地址進行查表,找出地址對應的內容,然后輸出即可。

A,B,C,D由FPGA芯片的管腳輸入后進入可編程連線,然后作為地址線連到到LUT,LUT中已經事先寫入了所有可能的邏輯結果,通過地址查找到相應的數據然后輸出,這樣組合邏輯就實現了。

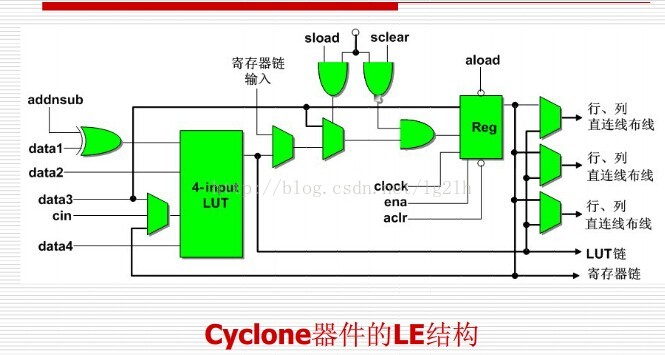

1個lab由8個LE(最小邏輯單元)組成;一個LE主要由寄存器和LUT組成。(LOOK-UP-TABLE)

一個邏輯單元主要由以下部件組成:一個四輸入的查詢表(LookUp Table,LUT),一個可編程的寄存器,一條進位鏈,一條寄存器級連鏈。

LUT本質上講就是一個16bit的SRAM(靜態隨機存儲器),4個輸入實際上就是SRAM的地址。其實等同于一個真值表。(16bit=24,每個輸入有2種可能,即2*2*2*2=16)

靜態RAM(SRAM)速度非常快,只要電源存在內容就不會自動消失。其基本存儲電路為6個MOS管組成1位,因此集成度相對較低,功耗也較大。一般高速緩沖存儲器用它組成。

動態RAM(DRAM)的內容在10-3或l0-6秒之后自動消失,因此必須周期性的在內容消失之前進行刷新。由于它的基本存儲電路由一個晶體管及一個電容組成,因此它的集成度高,成本較低,另外耗電也少,但它需要一個額外的刷新電路。

*/來源于網絡/**

)

![全新升級的AOP框架Dora.Interception[5]: 實現任意的攔截器注冊方式](http://pic.xiahunao.cn/全新升級的AOP框架Dora.Interception[5]: 實現任意的攔截器注冊方式)

)

)

:結構化展示多維數據)