前面學習了進行低功耗的目的個功耗的構成,今天就來分享一下功耗的分析。由于是面向數字IC前端設計的學習,所以這里的功耗分析是基于DC中的power compiler工具;更精確的功耗分析可以采用PT,關于PT的功耗分析可以查閱其他資料,這里不涉及使用PT的進行功耗分析。

(1)功耗分析與流程概述

上一個小節中講解了功耗的構成,并且結合工藝庫進行簡要地介紹了功耗的計算。但是實際上,我們根本不可能人工地計算實際的大規模集成電路的功耗,我們往往借助EDA工具幫我們分析電路的功耗。這里我們就介紹一下EDA工具分析功耗的(普遍)流程,然后下一小節我們將介紹低功耗電路的設計和優化。

①功耗分析流程的輸入輸出

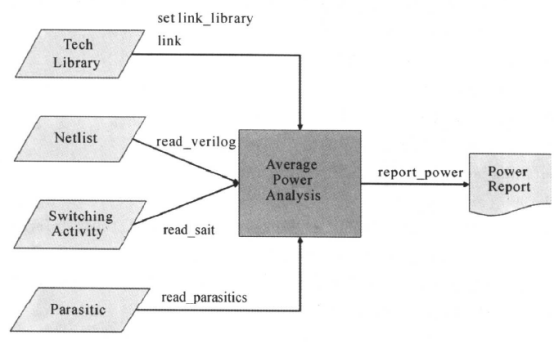

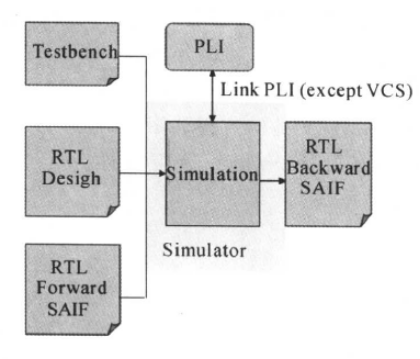

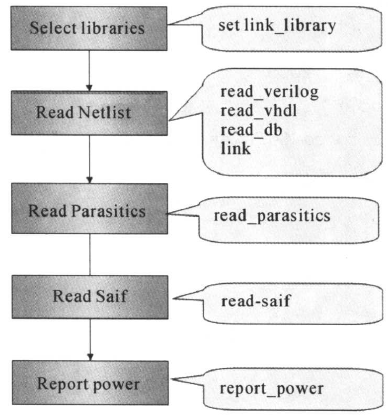

???功耗分析的流程(從輸入輸出關系看)如下所示:

?

上面的圖中,需要四種東西:

·tech library:這個就是包含功耗信息的工藝庫了,比較精確的庫里面還應該包含狀態路徑(SDPD)信息,代工廠提供。

·netlist:設計的門級網表電路,可以通過DC綜合得到。

·parasitic:設計中連線等寄生參數,比如寄生電容、寄生電阻,這個一般是后端RC寄生參數工具提供,簡單的功耗分析可以不需要這個文件。

·switch activity:包含設計中每個節點的開關行為情況,比如說節點的翻轉率或者可以計算出節點翻轉率的文件。這個開關行為輸入文件是很重要的。這個開關行為可以有不同的形式提供,因此就有后面不同的分析功耗的方法。

(注意,不管使用什么方法進行功耗分析,功耗分析的時候,輸入設計文件的都是門級網表文件)

?

②開關行為的一些概念

??說到開關行為,我們前面的翻轉率也是一種開關行為。此外我們還有其他關于開關行為描述的概念,這里我們通過舉例說明,如下圖所示:

?

?

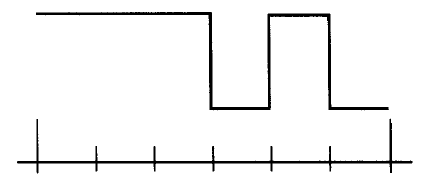

·翻轉(次)數:邏輯變化的次數,上圖中信號的翻轉數為3.

·翻轉率:前面也有相關介紹,這里重提一下,翻轉率是單位時間內信號(包括時鐘、數據等等信號)的翻轉次數。上圖中翻轉率為3/6 = 0.5(6個時間間隔內,翻轉了3次)

·T1,T0:(節點)信號的邏輯值為1和0的持續時間,上圖中T1為4,T0為2。

·靜態概率(static ?probability ,SP):(節點)信號邏輯值為1的概率,上圖中的SP為4/6=2/3。

?

?③開關行為(文件)情況表示

前面我們說到了功耗的分析需要開關行為的情況,一般就是指每個節點的翻轉率情況,我們有下面方式設置翻轉率:

??·直接命令進行:例如命令:

set_switching_activity??-static ??0.2 ??-toggle_rate ??20 -period ?1000 [all_inputs]

這時,翻轉率設置的節點是輸入,響應的翻轉率為:Tr = 20/1000 = 0.02GHz

??·SAIF文件:即switching activity interchange format,開關行為內部交換格式文件,用于仿真器和功耗分析之間交換信息的ASCII文件(美國標準信息交換碼文件)。

??·VCD文件,即value change dump 文件,它也是一個ASCII文件,文件中包括了一個設計中所選擇變量值的變化信息,這些信息通過在仿真testbench中使用“VCD系統函數”得到。

??在Synopsys的低功耗設計流程里面,可以使用power compiler(包含在design compiler中)進行功耗分析。我們可以通過命令來定義節點的翻轉率的方法來分析功耗----稱為無向量(vector-free)分析法;由于SAIF文件和VCD文件可以通過對電路仿真得到,它們是仿真接口格式文件,因此也可以通過VCS仿真器產生SAIF或者VCD文件的方法分析功耗。當要分析的結果比較精確時,一般使用SAIF文件或者VCD文件(VCD文件通過相關命令轉換成SAIF文件,而后使用SAIF進行功耗分析)。

?

(2)無向量分析法

前面我們說到,無向量分析法就是通過命令來定義節點的翻轉率的方法來分析功耗。我們先來逐條學習需要什么的命令,然后在后面進行舉例說明無向量分析法的腳本。

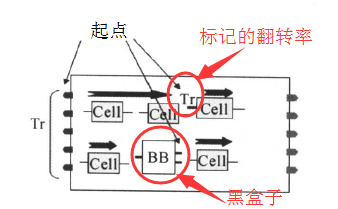

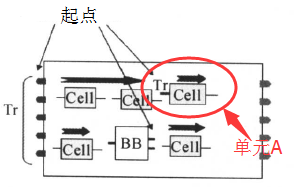

在學習設置翻轉率的命令之前,我們先來了解一下什么是設計的傳播起點和黑盒子。我們定義傳播的起點為設計的輸入端和黑盒子的輸出端,黑盒子是指在工藝庫里沒有功能描述的單元(比如ROM 、RAM或者一些IP核)。例如對于下面的設計中:

?

上面的設計有三處起點,一處是整個設計的輸入端,一處是黑盒子的輸出端,還有一處是某個單元的輸入端。最后一處的起點不包含在我們的定義中,但是我們也把它當做起點,因為這是被標記了翻轉率,這個我們后面進行講解。

利用無向量分析法分析功耗時,我們不必提供設計內部節點的翻轉率,而是通過設置起點的翻轉率就行了。我們有兩種方法設置翻轉率,一種是通過設置翻轉變量,一種是通過標記的方法。下面我們就來介紹如何通過這兩種方法進行設置翻轉率。

①設置翻轉變量

在power compiler中,可以設置下面的兩個翻轉變量進行設置翻轉率:

power_default_toggle_rate

power_default_static_probability

下面就來介紹一下這兩個變量(主要介紹power_default_toggle_rate)。

power_default_toggle_rate:其用法我們可以在DC中進行man一下,這個變量設置設計中默認使用的翻轉率。定義方式是:

set ??power_default_toggle_rate ??翻轉值

翻轉值默認是0.5。這個翻轉值不是翻轉率,這個變量定義的翻轉率是個相對的值:

·如果設計定義了時鐘,這個power_default_toggle_rate變量定義的翻轉率就以最快的時鐘為參考,比如翻轉值為0.5時,設計中最快的時鐘為10ns,那么翻轉率Tr = 0.5/10ns = 0.05GHz,也就是整個設計中默認的翻轉率是0.05GHz。

·如果設計中沒有時鐘,那么就會以工藝庫中的時間單位作為參考,例如工藝庫中的時間單位是ns,翻轉值為0.5,那么翻轉率Tr = 0.5/1ns = 0.5GHz。

power_default_static_probability:這個設置的是默認的靜態概率,也就是起點的邏輯值是1的概率。至于靜態概率,這里就不詳細描述了。這兩個變量的默認翻轉值都是0.5,翻轉率是很大的,一般情況下需要減小一點,比如設置為0.01和0.02這樣的。

?

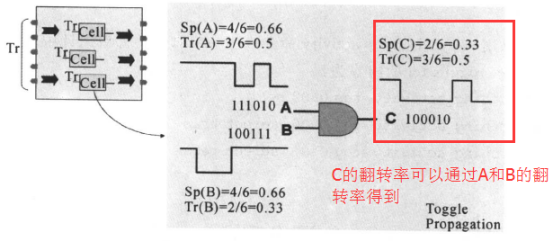

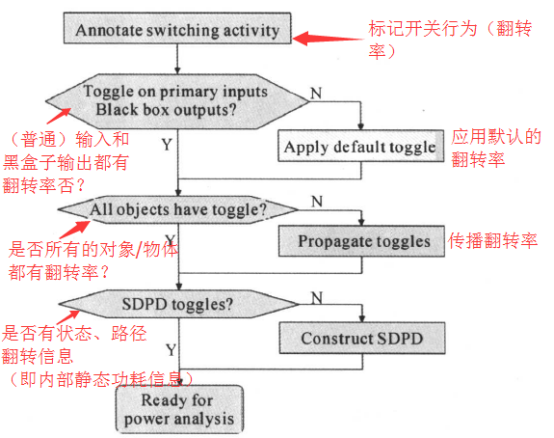

一般情況下,默認的翻轉率是設置在起點上的,也就是說起點的翻轉率用的是power_default_toggle_rate這個變量設置的翻轉率,內部節點的翻轉率可以通過傳播得到,如下圖所示:

?

需要說明的是,傳播不可以穿過沒有功能描述的黑盒子,也就是不能通過傳播的方式得到黑盒子的輸出翻轉率,因此我們在最前面就定義了,將黑盒子的輸出當做起點,這樣其他節點的翻轉率可以通過傳播得到(包括黑盒子的輸入),黑盒子輸出的翻轉率通過默認設置的翻轉率得到,我們就得到了設計中所有節點的翻轉率。

?

②標記翻轉率

上面的方式設置的是默認的翻轉率。當我們需要為某個節點標記某個指定的翻轉率,而不是使用默認的翻轉率時,我們就用到了標記頻率,如下圖所示:

?

單元A的輸入端口標記了特定翻轉率,比如說0.04GHz。標記的翻轉率比傳播的翻轉率優先級更高,被標記翻轉率的節點將作為一個新的起點,這就不屬于起點的定義,但還是叫它為起點的原因。標記翻轉率之后,這個單元后續的節點的翻轉率將通過這個新標記的翻轉率傳播得到。

設置標記翻轉率(簡稱設置翻轉率)的命令主要有兩條:

set_switching_activity 和 set_case_analysis,下面就來講解一下這兩條命令的意思。

set_switching_activity?:設置某個節點的翻轉率和靜態概率,在使用無向量分析法估算功耗的時候,這個命令被廣泛使用,越多的節點上被標記翻轉率,估算功耗的精度就越高。命令和選項如下所示:

set_switching_activity

???????????????[-static_probability static_probability]

???????????????[-toggle_rate toggle_rate]

???????????????[-state_condition state_condition]

???????????????[-path_sources path_sources]

???????????????[-rise_ratio rise_ratio]

???????????????[-period period_value | -base_clock clock]

???????????????[-type object_type_list]

???????????????[-hierarchy]

???????????????[object_list]

???????????????[-verbose]

下面來簡單介紹一下常用的幾個選項,詳細的介紹可以通過man set_switching_activity獲取。

-static_probability?:設置靜態概率。

-period?? ?period_value | -base_clock clock:設置時鐘(周期),-period和 -base_clock只能設置其中一個。

-toggle_rate:設置翻轉值,與-period或者 -base_clock相關聯。翻轉率Tr等于:用-base_clock選項指定的時鐘周期里面的翻轉數目 ?或 用-period選項指定的時間段里的翻轉數目;當沒有這個設置兩個選項時,將使用工藝庫里面的時間單位,即翻轉率等于在每個庫單位時間內的翻轉數目。

下面來舉例說明這個命令的用法:

例一:

create_clock CLK -period 20

set_switching_activity ?-base_clock ?CLK ?-toggle ??0.5 ?-static ?0.015 ?[all_inputs]

上述命令設置了時鐘周期為20ns,然后命令使用的是-base_clock的選項,所有輸入端的翻轉值為0.5,靜態概率為0.015,于是得到翻轉率Tr=0 .5/20=0.025 GHz

?

例二:

set_switching_activity -period ?1000 ?-toggle ?25 ?-static ?0.015 ??[all_inputs]

上述沒有創建時鐘,但是使用了period選項,意思是1000個周期內翻轉了25次,于是我們就可以得到所以輸入的翻轉率Tr=25/1000=0. 025 GHz

?

例三:

set_switching_activity -toggle ?0.025 ?-static ?0.015 [all_inputs]

上述命令中,-period和 -base_clock這兩個選項都沒有使用,這個時候就跟工藝庫里面的時間單位有關了,若庫中時間單位為ns,那么我們就得到翻轉率Tr=0.025 /1 = 0.025 GHz

?

上面講解了set_switching_activity ,下面我們就來講解一下set_case_analysis。

set_case_analysis?用來指定一個靜態邏輯值,也就是設置信號為常數,不進行翻轉;設計里面的一些信號需要這樣子設計,例如復位信號,設置如下所示:

set_case_analysis ?1 ?[get_ports reset]

則設置了reset的值常為1.

=================================================================================================

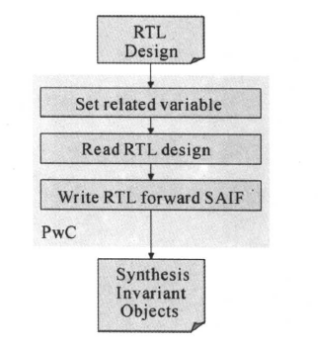

上面我們講解了設置翻轉率的方法,下面舉例說明一下如何綜合使用這兩種翻轉率。例如對于下面的設計:

?

翻轉率的設置要求如下所示:

1.正確地定義時鐘;

2.使用set_case_analysis命令設置常數控制信號reset;

3.在傳輸起點設置翻轉率,在輸入端和黑盒子輸出端設置任何已知的翻轉率,其他的起點將使用默認的翻轉率。

4.讓工具在設計中把翻轉率傳播下去

上面的沒有要求具體的翻轉率,因此我們可以設置我們想要的翻轉率,根據上面的要求,我們編寫相應的tcl腳本如下所示:

create_clock ?-p ?4 ?[get_ports clk}

set_case_analysis ?0 ?reset ?[get_ports ?reset]

set_power_default_toggle_rate ?0.003

set_switching_activity -tog 0.02 ?a

set_switching_activity -tog 0.06 ?b

set_switching_activity -tog 0.11 ?x

上面的腳本中,設置了周期為4(ns)的時鐘,然后利用set_case_analysis命令,設置reset端口為常數;翻轉值為0.003,那么對應的翻轉率為0.003/4ns,這個是默認的翻轉率;然后利用set_switching_activity命令指定a、b、x的翻轉值,其翻轉率為 翻轉值/4ns。

=============================================================================================

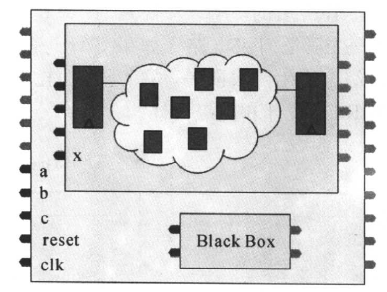

前面介紹了無向量分析法進行功耗分析,在介紹一下使用SAIF文件的方法進行功耗分析之前,我們先來介紹一下綜合不變物體和綜合變化物體的概念,下圖為一個電路的RTL設計和門級設計:

?

?

根據定義,在綜合前和綜合后,設計中的寄存器數目和寄存器的結構是不變的,輸入/輸出端口和層次邊界是不變的,設計中的黑盒子是不變的。這些不變的物體稱為綜合不變物體(Synthesis Invariant Objects,有時候也叫綜合不變對象)。設計中大部分的組合電路生成與設計約束有很大的關系,不同的約束產生不同的組合電路。這些變化的物體稱為綜合變化的物體(Synthesis Variant Objects)。由于SAIF文件中涉及這兩個概念,這里先進行介紹。

介紹完這兩個概念之后,下面我們就來了解一下使用SAIF進行功耗分析。SAIF文件當做翻轉率輸入文件的方法有兩種方式,也就是說利用SAIF進行功耗分析有兩種方法——對RTL級的電路仿真后得到的SAIF文件(稱為RTL backward SAIF)?以及 ?對門級網表的電路仿真后得到的文件(稱為Gate backward SAIF)。下面逐個進行具體介紹。

?

(3)SAIF--RTL BACK分析法

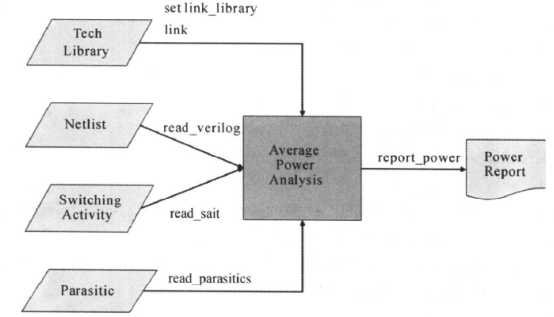

RTL?backward?SAIF文件是通過對RTL代碼進行仿真得到的,當設計很大的時候,門級仿真時間就會很長,這時候就可以使用這種方法進行分析。使用這種方法進行分析功耗的速度比較快,但是進度不夠門級仿真SAIF文件的高。

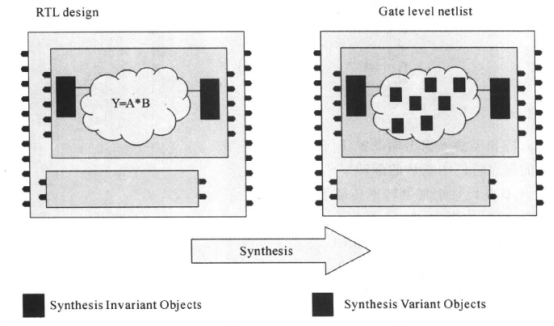

①RTL?forward?SAIF文件

RTL?forward?SAIF文件是記錄RTL設計中綜合不變物體的開關行為文件,可以簡單地理解:RTL?forward?SAIF文件簡要地記錄了綜合不變物的翻轉率。RTL?backward?SAIF文件的產生需要RTL?forward?SAIF文件,因此我們首先需要產生RTL forward ?SAIF文件。產生RTL ?forward ?SAIF文件的流程如下:

?

RTL ?forward ?SAIF文件是由power compiler (包含在design compiler中)產生的,根據流程,我們知道,主要設置一些變量,然后讀入RTL設計(RTL.v設計),接著讀出SAIF文件就可以了。相應的腳本如下所示:

set ?power_preserve_rtl-hier_names ?true

read_verilog ??"sub.v top. v"

rtl2saif ?-output ?fwd_ rtl.saif

一個示例RTL ?forward ?SAIF文件里面的部分內容如下所示:

(SAIFILE

(SAIFVERSION "2 .0")

(DIRECTION "forward")

(DESIGN)

(DATE "Wed May 12 18:31:19 2004

(VENDOR "Synopsys,Inc")

(PROGRAM NAME "rtl2saif")

(VERSION“1 .0")

(DIVIDER/)

(INSTANCE top

????(PORT

????(address\15\ address\15\)

????(address\14\ address\14\)

????(address\13\ address\13\)

????(address\12\ address\12\)

????(address\11\ address\11\)

????(address\10\ address\10\)

??······

我們可以看到,文件里面包含設計中一系列綜合不變的物體。在后續仿真中,仿真器只監視這些物體的開關行為。

?

②RTL?backward?SAIF文件的產生

下面是產生RTL backward SAIF文件的流程:

?

從上圖中,我們知道,產生RTL backward SAIF文件,需要在仿真器輸入testbench測試平臺文件、RTL.v設計、RTL forward SAIF文件,然后使用VCS產生RTL forward SAIF文件時,需要在testbench調用PLI監測節點的翻轉率。下面我們就來介紹一下這幾個部分。

·首先是PLI。使用VCS產生SAIF文件,需要用到程序設計語言接口(programming?language interface,PLI)。通過PLI監測節點的翻轉,得到節點的翻轉率。主要需要下面的系統任務:

$set_gate_level_monitoring ??( on|off|rtl_on);

$set_toggle_region ??(obj);

$read_ rtl_ saif(rtl_saif_file_name,tb_pathname);

$read_ lib_ saif(lib_saif_file_name);

$toggle_start;

$toggle_stop;

$toggle_reset();

$toggle_report(file_name,type,unit);

· RTL.v就是設計源文件了,然后RTL forward SAIF文件在前面也講過了,這里就從略。

· 最后是testbench。testbench中調用RTL設計、調用一下上述的PLI系統函數、調用RTL forward SAIF文件等。一個簡單的示例testbench文件如下所示:

module ?testbench;

top instl (a, b, c,s);//例化頂層設計

initial ?begin

??????$read_rtl_saif ("myrtl.saif")

??????$set_toggle_region ?(u1);

??????$toggle_start;

??????#120 ?a=0;

??????#STEP ?in_a=temp_in_a;

?······

??????$toggle_stop;

??????$toggle_report("rtl.saif",1.0e-9,"top");

end

endmodule

上面的測試平臺中,用了系統任務程序$read_rtl_saif ("myrtl. saif"),該命令讀入綜合不變物體文件——RTL?forward?SAIF。因此,仿真時,仿真器僅僅監視這些綜合不變物體的開關行為。向量中$set_toggle_region (u1)命令選擇要監視的模塊。$toggle_start和$toggle_stop命令用于控制監視的起始和終止時間。$toggle_report("rtl. saif",1. 0e-9,"top")命令輸出SAIF信息到指定的文件。

一起都準備就緒了,下面就可以使用VCS運行仿真:

vcs ?-R ??rtl. v ?testbench. v

注意,這里我們進行的是RTL設計文件的仿真,仿真完成后,就可以得到rtl.saif?文件,這個文件就是RTL?backward?SAIF文件。

?

③功耗的分析

對RTL代碼仿真后,所得到的RTL Backward SAIF文件包含了設計中綜合不變物體的開關行為信息。進行功耗分析時,分析工具通過其內部仿真器把綜合不變物體的翻轉率傳播下去,從而得到其他所有節點的翻轉率,進行門級電路的功耗分析。得到了RTL backward SAIF文件之后,我們根據前面的功耗分析的流程(從輸入輸出關系看),就可以分析功耗了:

?

這里的開關活動文件就是RTL backward SAIF文件了。然后在power compiler中利用RTL backward SAIF文件進行功耗分析的流程如下所示:

?

一個相應的示例腳本如下所示:

set ?target_library ?my. db

set ?link_library ?"* ?$target_library"

read_verilog ??mynetlist.v

current_design top

link

read_ saif ?-input ?rtl.saif ?-inst ?testbench/top

report_power

利用RTL backward SAIF文件分析功耗的過程就是上面這個樣子了。上面的流程和腳本適用于前版圖(pre-layout)的設計,沒有用到寄生參數文件。連線的RC參數使用工藝庫里的線負載模型。如果是后版圖(post-layout)的設計,要盡量使用寄生參數文件,提高功耗分析的精確度。

從上面我們就知道,利用RTL backward SAIF文件分析功耗的流程就是:

power compiler 產生 RTL forward SAIF文件 ——》VCS仿真產生RTL ?backward SAIF文件 ——》power compiler 進行分析功耗。

?

(4)SAIF--GATE分析法

前面介紹了RTL backward SAIF文件分析功耗的方法和流程,下面介紹一下Gate backward SAIF文件分析功耗的方法和流程,這個與RTL backward SAIF文件的很類似。

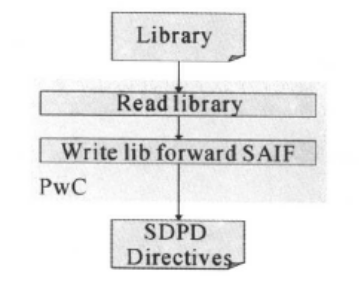

①library ?forward ?SAIF 文件(簡稱為 庫SAIF文件)

庫SAIF文件是包含SDPD(電路狀態路徑)信息的SAIF文件。Gate backward SAIF文件的生成需要庫SAIF文件,該文件可以通過power compiler生成,流程如下所示:

?

?

對應該流程的一個示例腳本如下所示:

read_db ?mylib.db

lib2saif ?-output ?mylib. saif ?-lib_pathname ??mylib.db

示例庫SAIF文件的部分內容如下所示:

(SAIFILE

(SAIFVERSION "2.0" "lib")

(DIRECTION "forward")

(DESIGN)

(DATE "Mon May 10 15:40:19 2004"

(VENDOR "Synopsys,Inc")

(PROGRAM NAME "lib2saif")

(DIVIDER / )

(LIBRARY "ssc_core_typ"

??(MODULE "and2al"

??????(PORT

????????(Y

??????????(COND A RISE FALL (IOPATH B)

????????????COND B RISE FALL(IOPATH A)

????????????COND DEFAULT)

????????)

······

庫SAIF文件中包含了SDPD信息。有了庫SAIF文件,仿真時,仿真器會根據庫中的SDPD信息,監視節點的開關行為。

?

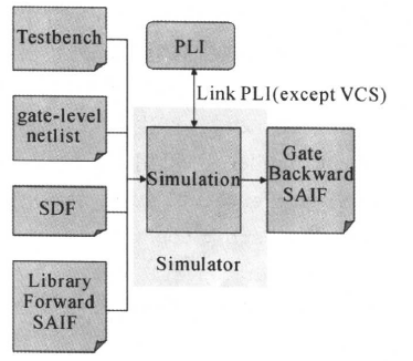

②Gate Backward SAIF文件的生成

下面是產生gate backward SAIF文件的流程:

?

從上圖中我們可以看到,產生gate backward SAIF需要testbench測試平臺、門級網表、標準延時格式(standard delay format)文件SDF、庫SAIF文件。其中SDF文件反標了門級網表中的RC延時參數等,可以更為準確地得到線網的延時。

testbench的示例內容如下所示:

module testbench;

top instl (a, b, c,s);

initial

$sdf_annotate("my.sdf",dut)

initial begin

$read_lib_saif ("mylib.saif");

$set_toggle_region (u1);

$toggle_start;

#120 ?a=0;

#STEP ?in_ a=temp_in_a;

······

$toggle_stop;

$toggle-report("gate.saif",1.0e-9,"top")

end

endmodule//testbench

testbench測試平臺主要是調用門級網表、SDF文件、庫SAIF文件。testbench中,用$sdf_annotate("my. sdf", dut)命令作SDF標記,以保證時序的正確性,從而得到正確的翻轉數目。$ read_lib_saif ("mylib. saif")命令讀取庫SAIF文件中的SDPD信息。仿真器只監視在SAIF文件里列出的SDPD開關行為。$ set_toggle_region (u1)命令選擇要監視的模塊。$ toggle_start和$toggle_stop命令控制開始和結束時間。$ toggle_report("gate. saif",1. 0e-9, "top")命令把SAIF輸出到指定的文件。

萬事俱備,只欠仿真,接下來就是使用VCS進行仿真了:

vcs ??-R ??top.v ??testbench. v

注意,這里的仿真是對門級網表的仿真,也就是說這里的top.v是門級網表。產生的示例gate forward SAIF文件的部分內容如下所示:

(SAIFILE

(SAIFVERSION "2 .0")

(DIRECTION ?"backward")

(DESIGN)

(DATE ?"Mon May 17 02:33:48 2006")

(VENDOR "Synopsys,Inc")

(PROGRAM_NAME ?"VCS-Scirocco-MX Power Compiler")

(VERSION "1 .0")

(DIVIDER / )

(TIMESCALE ?1 ?ns)

(DURATION ?10000.00)

(INSTANCE tb

(INSTANCE top

??(NET

????(z\3\

????????(T0 6488) (T1 3493) (TX 18)

????????(TC 26) (IG 0)

????)

······

(z\32\

??? ?(T0 6488) (T1 3493) (TX 18)

???????? (TC 26)(IG 0)

?????? )

???? ······

)

(INSTANCE U3

??(PORT

??(Y

??????(TO 4989) (T1 5005) (TX 6)

??????(COND((D1 * !DO)|(! D1*D0)) (RISE)

??????????(IOPATH S (TC 22 )(IG 0)

????????????)

??????COND((D1*!DO)}(!D1,DO))

??????????( IOPATH ?S ?(TC ?21)(IG 0) (FALL)

???????????)

??COND DEFAULT (TC 0)(IG 0)

??)

?······

Gate Backward SAIF文件是通過對門級網表進行仿真所得到的。如果設計很大,仿真需要的時間很長。好處是精確度很高。VCS所產生的Gate Backward SAIF文件中包含了一些或所有連線的開關行為和單元的開關行為。這些開關行為分別以上升和下降表示,與狀態和路徑有關。用這個信息可以進行精確的功耗分析。

?

③功耗分析

有了門級網表、gate backward SAIF文件和SDF文件,就可以在power ?compiler中進行功耗分析了,分析功耗的流程圖如下所示:

?

對應的一個示例腳本文件如下所示:

set ??target_library ?mylib.db

set ?link_library " * $target_library"

read_verilog ?mynetlist.v

current_design ?top

link

read_read_parasitics ?top.spef

read_ saif -input ?mygate. saif ?-inst ?tb/top

report_power

上面的流程和腳本適用于后版圖(post-layout)的設計,spef文件在做完版圖后產生。使用寄生參數文件,提高了功耗分析的精確度。如果是前版圖( pre-layout)的設計,沒有寄生參數文件,連線的RC參數使用工藝庫里的線負載模型。

最后總結一下,這里分析功耗流程為:

power compiler 產生庫SAIF文件——》VCS產生gate backward SAIF文件——》power compiler進行功耗分析。

?

?

(5)VCD轉SAIF分析法

前介紹了使用SAIF文件分析功耗的方法,這個方法都是通過VCS仿真得到相應的SAIF文件,然后進行功耗分析。下面我們介紹使用VCD文件轉換成SAIF文件的方法,然后進行功耗分析。

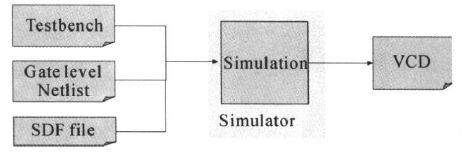

①VCD文件的產生

首先,我們在進行仿真的時候,需要通過在testbench中加入相關的系統函數,產生相應的VCD文件(和SDF文件),流程示意圖如下所示:

?

相應的一個示例testbench如下所示:

module testbench;

······

initial

??$sdf_annotate("my.sdf",dut)

initial begin

??$dumpfile("vcd.dump");

??$dumpvars;

······

endmodule

然后使用下面命令進行仿真:

vcs ?-R dut.v ?testbench.v ?+delay_mode_path

完成仿真之后,就可以得到VCD文件了。

?

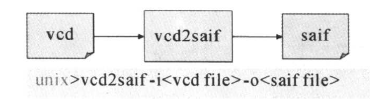

②VCD文件轉換成SAIF文件

仿真時產生的VCD文件也包含了設計中節點和連線的開關行為。在Power Compiler中,可以使用程序vcd2saif可以把VCD文件轉化為SAIF文件,如下圖所示:

?

?

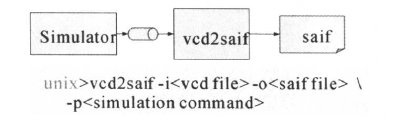

vcd2saif是在UNIX命令行使用的一個程序。vcd2saif程序也可以把VPD文件(二進制格式的VCD文件)轉化為SAIF格式的文件。如果設計很大,仿真的時間長,vcd2saif程序可以用管道傳遞的方式把VCD轉化為SAIF文件。這時vcd文件不存放在文件里,vcd通過先入先出(First-In ?First-()nt,簡稱FIFO把數據傳給vcd2saif程序,然后產生SAIF文件。轉換的SAIF文件里沒有SDPD的信息。如下圖所示:

?

有了SAIF文件之后,我們就可以像前面那樣使用SAIF文件進行功耗分析了,至于是版圖前的功耗分析還是版圖后的功耗分析,取決于功耗分析時有沒有與版圖中有關的信息,比如是SPEF文件。因此流程為:

VCS產生VCD文件——》power compiler 將VCD文件轉換為SAIF文件——》power compiler 進行分析功耗

最后,我們來說一下這里使用vcd2saif程序的好處,主要有下面三點:

1. ?VCD產生的速度快;

2. ?VCD是IEEE的標準并且適用于進行后仿真;

3. ?轉換的過程快。

?=============================================================================================

我們已經介紹四種為設計產生開關行為的方法,分別是直接設置翻轉率、RTL backward SAIF文件、gate back SAIF文件和VCD轉SAIF文件;這些方法可以混合使用,其優先次序如下所示:

?

?

用read_ saif命令標記的開關行為優先級最高;用set_switching_activity命令設置的開關行為優先級次之;優先級最低的是用默認的變量power_default_toggle_rate指定的翻轉率。

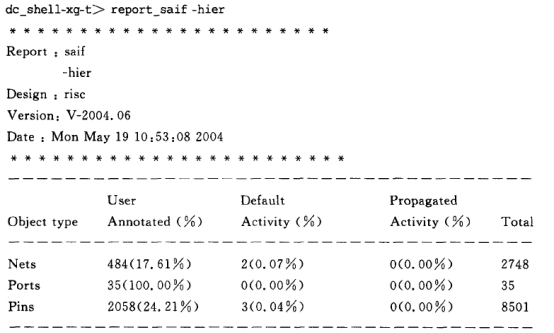

????開關行為可以被清除,使用“reset_switching_activity”命令可以清除所有被標記的翻轉率和通過傳輸得到的翻轉率。用report_saif可以顯示讀入saif文件后設計中的開關行為信息。一個完整的SAIF文件,"user annotated”應該是100%。如果SAIF不完整,那么默認的翻轉率將附加到輸入端和黑盒子的輸出端。翻轉率通過零延遲仿真傳輸下去,這樣就可以計算出設計的功耗。

使用report_saif命令的一個例子如下:

?

?

與開關行為有關的命令有:

merge_saif #合并SAIF文件

read_sai f #讀backward SAIF文件

report_saif #報告開關行為的信息

rtl2saif #產生RTL forward SAIF文件

write_ saif #寫出一個backward SAIF文件

lib2saif #產生library forward SAIF文件

propagate_switching_activity #傳輸功耗清除

reset_switching_activity #清除開關行為和/或翻轉率

set_switching_activity #在指定的物體上設置開關行為

?

?

?

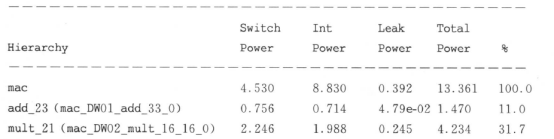

(6)功耗分析報告

我們是通過分析功耗報告(report_power命令產生)來查看設計功耗的,一個功耗報告的示例部分內容如下所示:

Cell ?Internal ?Power=883.0439 mW(66%)

Net ?Switching Power=453.0173 mW(34%)

Total ?Dynamic ?Power=1 .3361 W(100%)

Cell Leakage Power = 391.5133 nW

其中第一項為內部短路功耗,第二項為開關功耗,合起來為動態功耗;最后一項為靜態功耗,也就是泄漏功耗。如果要報告設計中每個模塊和單元的功耗,在report_power命令后加選項 -hier,例如: ?report_power ?-hier,產生的報告如下所示:

?

系統與架構級低功耗設計)

——MFC是一個編程框架)

RTL級低功耗設計)

)

門級電路低功耗設計優化)

)