APB(Advanced Peripheral Bus)

1、APB的概述與特點

APB主要用于低帶寬的周邊外設之間的連接,例如UART、1284等,它的總線架構不像AHB支持多個主模塊,在APB里面唯一的主模塊就是APB 橋。其特性包括:兩個時鐘周期傳輸;無需等待周期和回應信號;控制邏輯簡單,只有四個控制信號。

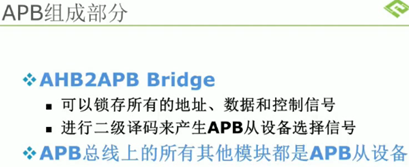

2、APB的組成部分

3、 APB的數據傳輸

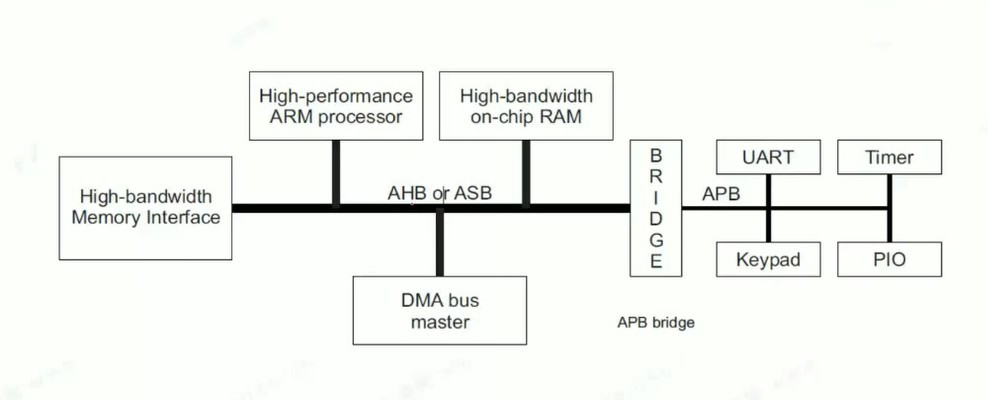

APB上的傳輸可以用如下圖所示的狀態圖來說明。

?

- 系統初始化為IDLE狀態,此時沒有傳輸操作,也沒有選中任何從模塊。

- 當有傳輸要進行時,PSELx=1,PENABLE=0,系統進入SETUP狀態,并只會在SETUP 狀態停留一個周期。當PCLK的下一個上升沿時到來時,系統進入ENABLE 狀態。

- 系統進入ENABLE狀態時,維持之前在SETUP 狀態的PADDR、PSEL、PWRITE不變,并將PENABLE置為1。傳輸也只會在ENABLE狀態維持一個周期,在經過SETUP與ENABLE狀態之后就已完成。

- 之后如果沒有傳輸要進行,就進入IDLE狀態等待;如果有連續的傳輸,則進入SETUP狀態。

4、傳輸時序

4.1、Write

寫傳輸分為不帶等待信號的寫,和帶等待信號的寫:

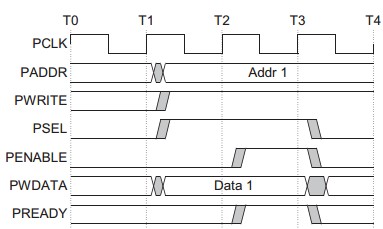

無等待狀態

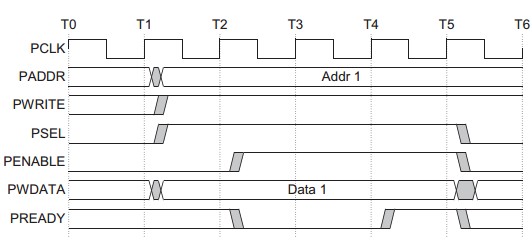

下圖顯示了一個基本的無等待狀態的寫傳輸。

- T1 時刻 APB 將地址信息 PADDR 和寫的數據 PWDATA 準備好,拉高 PWRITE 表示進入寫,同時拉高 PSEL,從 IDLE 進入 SETUP

- T2 時刻也就是下一個時鐘周期拉高 PENABLE,使得狀態進入 ACCESS

- T3 時刻檢測到 PREADY 被拉高,也就是說 Slave 已經正確接收到數據,傳輸完成;PENABLE 拉低,PSEL 拉低

有等待狀態

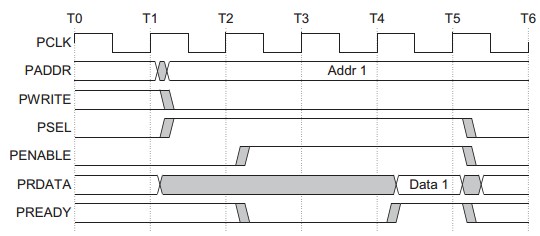

下圖展示了?PREADY?信號是如何擴展了從器件的傳輸。

- T1 時刻 APB 將地址信息 PADDR 和寫的數據 PWDATA 準備好,同時拉高 PSEL,從 IDLE 進入 SETUP

- T2 時刻也就是下一個時鐘周期拉高 PENABLE,使得狀態進入 ACCESS

- T3 時刻檢測到 PREADY 為 0,也就是說 Slave 還沒有接收完數據,所以在此刻,PADDR 地址信號、PWRITE 數據方向信號、PSEL 片選信號、PENABLE 使能信號以及PWDATA 數據必須保持,以便 Slave 能夠繼續采樣。

- T4 時刻 PREADY 依然 為 0,所以還是保持不變

- T5 時刻,PREADY 為 1,說明 Slave 已經正確接收到數據,傳輸完成;PENABLE 拉低,PSEL 拉低

注意:即便是傳輸結束了,Address 和 data 信號也不會立即改變,直到下一次傳輸才會刷新新的地址和數據信號,這樣做的原因是減少功耗;

4.2、Read

讀數據和寫的流程幾乎差不多,也分為了等待和非等待

無等待狀態

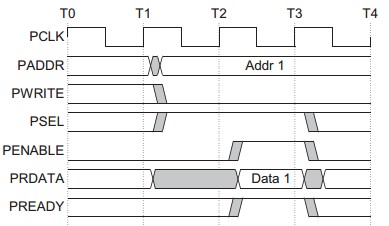

同非等待寫一樣,圖示如下:

- T1 時刻 APB 將地址信息 PADDR 準備好,拉低 PWRITE 表示進入讀,同時拉高 PSEL,從 IDLE 進入 SETUP

- T2 時刻也就是下一個時鐘周期拉高 PENABLE,使得狀態進入 ACCESS

- T3 時刻檢測到 PREADY 被拉高,也就是說 Slave 已經完成收據發送,PRDATA 上就是來自 Slave 的數據,傳輸完成;PENABLE 拉低,PSEL 拉低

有等待狀態

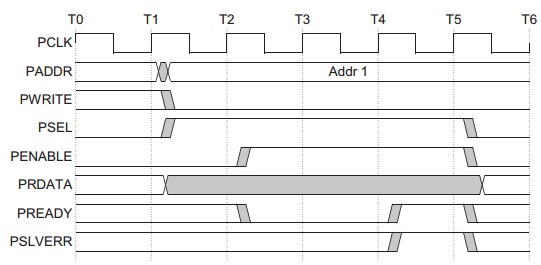

加等待的讀時序如下:

時序過程和上述一樣,只不過 PREADY 被拉低了兩個周期,真正從 Slave 讀的數據到 T5 時刻才真正有效;這里不在多說;

4.3、Error Respond

在讀和寫的過程,可能出現錯誤,錯誤通過 PSLVERR 信號來指明;

APB外圍設備不要求必須支持PSLVERR引腳,當不使用該引腳時,應被置低

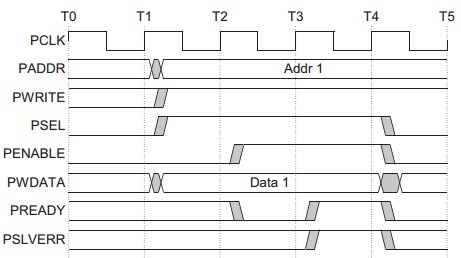

寫失敗后時序

下面這個是寫失敗后的時序:

可以看到,在寫失敗后,PSLERR 信號被拉高了

讀失敗后時序

下面這個是讀失敗后的時序:

讀失敗后,PRDATA 上的數據不再有效

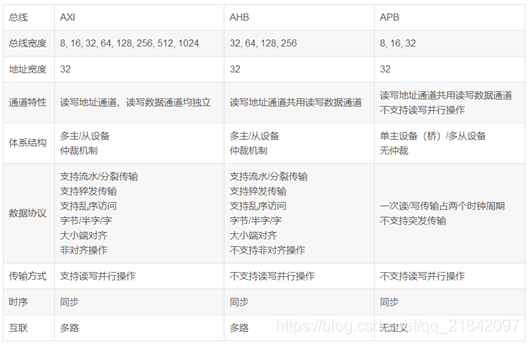

5、對比

)

)

== 5)的問題...)