????????隨著技術的發展,數字電路的集成度越來越高,設計也越來越復雜。很少有系統會只工作在同一個時鐘頻率。一個系統中往往會存在多個時鐘,這些時鐘之間有可能是同步的,也有可能是異步的。如果一個系統中,異步時鐘之間存在信號通道,則就會存在CDC(clock domain crossing)問題。

????????SpyGlass CDC分析使你能夠識別設計中的CDC問題。SpyGlass CDC tool是一種 Formal Check Methodology工具, 相比寫case跑仿真來找CDC問題, 靠SpgGlass能更早,更全,更快的發現CDC問題. 它能夠:

- 管理多時鐘域設計

- 系統地處理CDC問題

- 檢查和報告任何不同步的信號: 時鐘和復位

????????當SOC design涉及的clock domain太多,用到很多第三方IP,及涉及人員水平參差不齊時, 用SpyGlass CDC來做檢查來保證RTL質量是十分必要的.

一、基本流程

????????在工程的block-level和SOC 集成的兩個不同階段, 所適用的CDC Goal也是有所不同的。Block-Level關心的是模塊內部, 只有模塊內檢查沒問題后才能做deliver. 而SOC集成主要關心的是模塊間interface的CDC問題。

1、block level

????????

????????各個步驟的說明如下:

(1)Creating SpyGlass CDC Setup:指定constraints(SGDC file)、parameters 及其他指定用于該project的定義來精準運行SpyGlass CDC檢查。

????????可以使用‘sdc2sgdc’ 命令來將 block-level SDC 轉化成相應的SGDC 約束文件。運行 “cdc_setup_check”goal 能夠生成constraints, 但生成的constraint一定要designer仔細review下再用。運行‘cdc_setup’后工具可以理解整個design的architecture, 解決一些block-box的問題,并自動生成‘autoclock.sgdc’及autoreset.sgdc作為 constraint的base來使用。 合理設置parameter可以極大的減少CDC error/warning的數量。

(2)Verifying SpgGlass CDC Setup: :檢查setup的正確性和完整性。在進行下一步時一定要修掉該stage報的violation,如確保所有flip-flop都有時鐘。“set_case_analysis”參數合適定義來確保多時鐘源的flip-flop有指定的時鐘選擇。時鐘的周期,有效沿及domain都需要合適定義。

(3)Performing Clocks and Reset Integrity Checks:修掉時鐘和復位不完整定義的問題,確保時鐘和復位都被合理定義,并且確保clock/reset沒有glitch和race。

(4)Performing Block-Level CDC Verification: 要修掉所有的violations, error和warning都要review,必要時可以waive掉。 清理violation是有先后優先級順序的。優先級如下:

- Ac_sync_group Rule violations; rule Ac_unsync01(for scalar unsync) 和 Ac_unsync02(for vector data unsync),增加constraint或設置cdc_false_path, 不要靠waive來修,也可以定義static,quasi-static來解決.?

- Convergence violations: rule Ac_conv01,Ac_conv02,Ac_conv03,Ac_conv04 and Ac_conv05.

- Glitch violations: Ac_glitch* 和 Clock_glitch*

- Data hold violation: rule Ac_cdc01, 表明 signal/data從快時鐘到慢時鐘發送時hold不住。

- Data hold issues in synchronized data crossing: rule Ac_datahold01a

- Violations related to data correlation and race conditions: Rule Ac_cdc08, Ac_conv01 and Ac_conv02

- Violations related to reset synchronization and deassertion: Rule Ar_unsync01, Ar_sync01,Ar_asyncdeassert01,Ar_syncdessert01,Reset_sync02

- violations related to FIFO recognition and verification: Rule Ac_fifo01, SpgGlass可以識別通常的FIFO結構。 也可以在constraint file(SGDC)中指明fifo。

(5)Performing SOC-Level CDC Verification:在soc level進行CDC檢查,可以發現所有structural issues。

(6)Signing-off SpyGlass CDC Verification:檢查報告,清干凈問題和sign-off 。

2、SOC level

????????不同于block level flow, 在Hierarchy Verify Flow中使用abstract view來專注于模塊邊界的問題,從而減少CDC verify的運行時間。block owner deliver 已經verified的模塊給SOC集成team,SOC integration team在abstract view上不用再擔心block內的問題。如果有些block 是不可用的,可以為這些block產生abstract views, 從top-level移植constraints到block-level,考慮添加‘ip_block' constrain 到這些block.

二、流程介紹

????????在執行SpyGlass CDC 分析之前,需要檢查必要的先決條件。進行SpyGlass CDC分析的先決條件如下:????????

- 成功運行design-read流程

- 確保設計包含最少數量的非預期的black box

- 在設計中為實例化的技術庫單元提供相應的技術庫(.lib)

- 在設計中指定有關時鐘的信息,以及復位信息(如果可能的話)

????????建議在開始運行SpyGlass CDC之前,從設計規范、IPs或芯片引線收集這些信息。如果沒有這些信息,SpyGlass CDC也能夠提供自動檢測時鐘和復位,但是會推斷出額外的時鐘和復位,最好是能夠預先明確所有的時鐘和復位信息。

1、CDC setup

????????創建設置意味著在執行CDC驗證之前指定設計信息,例如時鐘、重置和停止模塊。設置的質量決定了SpyGlass CDC分析的質量。錯誤或不完整的設置可能會導致許多違例或掩蓋一個真正的設計錯誤。

????????可以通過以下流程建立SpyGlass CDC設置:

- 將時鐘生成模塊指定為black box

- 為設計指定時鐘和復位

- 為設計生成時鐘和復位

- 使用設置管理器

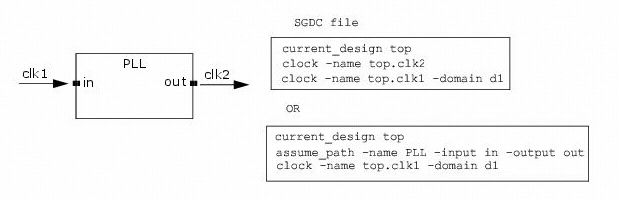

1)?將時鐘生成模塊指定為black box

????????對時鐘生成模塊(比如PLL)的內部執行SpyGlass CDC分析非常復雜,而且對整體SpyGlass CDC分析幾乎沒有價值。將這些塊標記為黑盒子,除非你有詳細的SGDC約束來定義這些模塊的時鐘特性。標記PLL時鐘生成模塊為black boxes的方法是,在project file中設置如下命令:

set_option stop <blocks>????????一旦你設置這些模塊為black boxes:

- 將時鐘約束定義在這些模塊的輸出pin上

- 將輸出時鐘和輸入定義為同一個時鐘域,除非兩者之間沒有相位關系

2)?為設計指定時鐘和復位

????????如果知道設計中的時鐘和復位,可以執行以下步驟來指定他們:

????????在SGDC中定義CLOCK和RESET的約束:

clock -name “clk_sys”reset -name “rst_n” –value 0? ? ? ? 在此流程還需要檢查約束的完整性:

- 通過運行SpyGlass CDC 方法的Goals來分析設計

- 檢查The Clock-Reset-Summary Report.

- 在The Clock-Reset-Summary Report 的Section D: Cases not checked for clock domain crossings Section里面列出了unconstrained clocks.

- 修改SGDC來指定The Clock-Reset-Summary Report里列出的時鐘信號;

- 修改SGDC后重復步驟2;

3)為設計生成時鐘和復位

????????如果不知道設計中的時鐘和復位,可以執行以下步驟來生成:

1. 運行cdc_setup?goal:這個步驟產生了autoclocks.sgdc和autoresets.sgdc兩個SGDC文件,包含了推斷的時鐘和復位。

2. 檢查和修改生成的SGDC文件:這些文件可能包括一些除了真正的時鐘和復位的控制信號。因此,你必須檢查這些文件中的每個推斷的時鐘和復位,并刪除不是真正的時鐘和復位信號。建議查看Setup_clock01和Reset_info01規則信息,以查看這樣的推斷信號。

3. 在SpyGlass中指定修改過的autoclocks.sgdc 和 autoresets.sgdc文件,并通過運行相應的Goal來分析設計。默認情況下,autoclocks.sgdc文件中生成的clock 假定為一個單獨的時鐘域。在這種情況下,CDC Verification Rules?報告了對每對時鐘信號之間的時鐘域交叉的違例。

????????但是,工具可能會將設計中的一些時鐘信號視為來自同一域。在這種情況下,工具會認為觸發器之間的數據傳輸沒有同步問題。我們可以通過約束中的clock 關鍵字來修改時鐘域的信息。通過修改clock的-domain參數為同一個值來指定所有相同時鐘域的clock到同一個時鐘域。注意-domain的參數可以是有效的字符串或者時鐘名。

2、Verifying SpgGlass CDC Setup

????????Setup的主要目標是保證clock和reset被正確定義,必須保證所以error都被修復了,才能進行下一步,不然后續會有很多意想不到的錯誤。通過運行cdc_setup_check來進行。

3、Performing Clocks and Reset Integrity Checks

????????這個步驟必須確保時鐘和復位被正確定義,并且它們沒有glitches、競爭和其他故障。

????????通過運行clock_reset_integrity goal來修復時鐘和復位的完整性。

4、Performing CDC Verification

????????CDC驗證是指在設計中檢測CDC問題。

要執行CDC驗證,請執行以下步驟:

- 設置所需的參數(parameters)

- 運行Goals,例如cdc_verify和cdc_verify_struct,以檢測大量的CDC問題。

????????最初可能會發現大量違反CDC的情況。以一種系統的方式來處理它們是很重要的,這樣就可以快速地處理一些需要考慮的問題。

????????下列列出了大多數重要的違例種類

1)未同步的跨時鐘域問題 (Unsynchronized Crossings Issues)

????????首先,通過查看Ac_unsync01?和Ac_unsync02來檢查未同步的跨時鐘域問題。

????????未同步就進行跨時鐘域設計會產生亞穩態,這是最基本的CDC問題。? ? ? ??

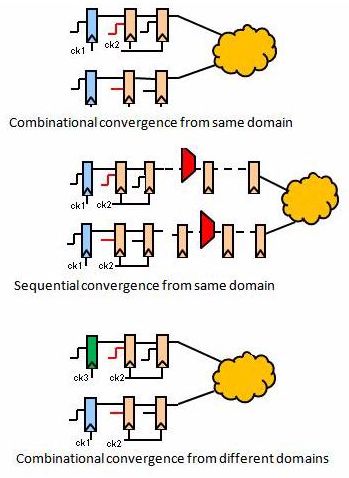

?2)?聚合問題(Convergence Issues)

????????聚合問題發生在多個信號(可能是同一個時鐘域也可以是不同的時鐘域)從一個時鐘域跨到另一個相同的時鐘域,但是這些信號是分開同步的。這樣你在使用這些同步過的信號的時候,就不能確定他們是不是同時有效,這樣有可能就有問題。幾種情況如下:

????????有關此類違規類型的信息,一般查看Ac_conv01、Ac_conv02、Ac_conv03、Ac_conv04和Ac_conv05。

?3)復位同步問題

????????對于此類問題,請檢查違反Ar_*規則的情況。這些rules報告同步異步復位信號的違規行為。

????????由于復位通常是單比特信號,你可能希望在Ac_sync01下報告它們。但是復位的同步往往不同,比如常見的異步復位同步釋放,輸入是拉高的。

????????例如,下圖顯示了一個復位同步釋放:

?????????有關這些違規的信息,請參見Ar_asyncdeassert01、Ar_syncdeassert01、Ar_sync01和Ar_unsync01。

4)毛刺問題

????????檢查通過Ac_glitch*或Clock_glitch*規則報告的所有違例。

????????這些規則突出了容易出現毛刺的邏輯,這些邏輯可能導致與同步問題非常類似的問題。

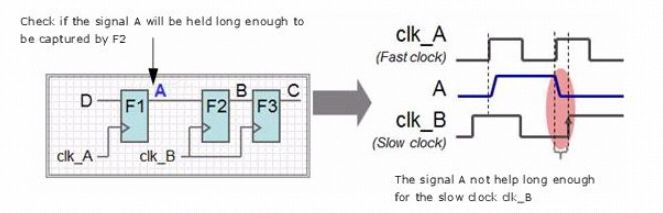

5)跨時鐘信號寬度錯誤(Signal Width Errors in Synchronized Control Crossings)

????????請檢查Ac_cdc01?rule 違例。

????????這種違例通常發生在信號從快時鐘穿越到慢時鐘,信號在慢時鐘還沒采樣到的時候已經發生變化。下圖是信號寬度問題的例子:

6)數據跨時鐘的保持時間問題

????????請檢查Ac_datahold01a?違例。

????????在使用同步器,但功能不正確的情況下,會出現此類違規報告的信號。考慮如下的情況:

????????上圖是一種不正確的跨時鐘同步器的情況。這里,數據在enable有效的時候發生了變化。

5、調試CDC問題

????????在調試CDC問題之前,需要保證setup是正確的。

????????在正常規模的設計上跑SpyGlass CDC,一般會有大量的違例。大部分違例是因為:

- 錯誤或者不完備的setup

- 配置信號,通常不應報告為CDC錯誤

????????注意:千萬不要通過waiving的方式解決CDC的問題,這樣十分危險,可能wave掉了真正的CDC問題。每一條waver都必須反復check。

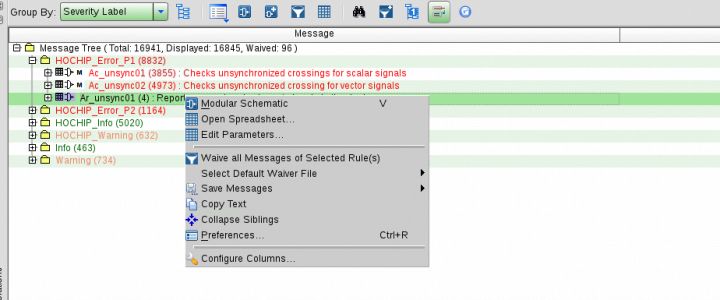

1)使用電子表(Using Spreadsheets)

????????當存在許多違規行為時,這些違規行為中的很大一部分是由一小部分的根本原因造成的。

????????分析它們的推薦方法是使用電子表格查看器。執行以下步驟來使用電子表格查看器調試大部分的違規:

1. 打開電子表查看器

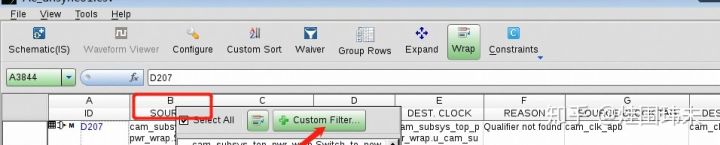

????????通過右鍵單擊違例標題(rule的大類,比如Ar_unsync01)并從快捷菜單中選擇電子表格查看器選項來打開電子表格。如下圖所示:

2. 篩選和排序數據

????????在電子表格視圖中使用篩選和排序來區分共同因素和違例。要過濾或排序數據,右鍵單擊列標題并從快捷菜單中選擇一個適當的選項,如下圖所示:

????????每一列單擊可以排序,右鍵可以過濾:

3. 檢查常見原因或者來源

????????在電子表格中查找常見原因或常見來源。這些很可能指向一個單一的根本原因。

4. 根據源來進行過濾

????????如果您正在使用靜態信號的命名方法,請在電子表格中按源名稱進行篩選。比如篩選所有的配置寄存器。例如,下圖顯示了如何為源指定過濾條件(_cfg):

?????????查看過濾后的列表并解決根本原因,以消除大量違例。

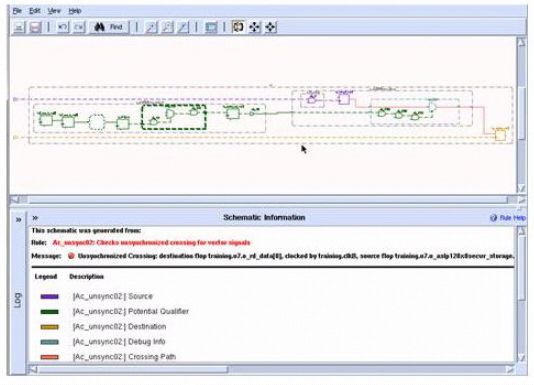

2)使用增量示意圖(Incremental Schematic)

????????示意圖使你能夠理解和隔離沖突的根本原因。

????????你可以查看電子表格中出現的多個相關違規的示意圖。為此,請執行以下步驟:

1.通過按下<Ctrl>鍵盤鍵在電子表格中選擇違規。

2.執行下列操作之一,打開增量示意圖:

- 單擊電子表格中某一行的Schematic列中的鏈接。

- 單擊電子表格工具欄中的增量示意圖按鈕。

????????也可以右鍵直接選擇Incremental Schematic

????????下圖為增量示意圖:????????

?3)在示意圖中查看調試數據

????????在示意圖中調試SpyGlass CDC解決違例時,以下信息非常有用:

- clock 路徑中的net的時鐘域信息

- reset 路徑中的net的復位域信息

- 數據或者控制信號的時鐘域信息

- 數據或者控制信息的準靜態信息

????????注意:必須將enable_debug_data參數的值設置為yes,才能查看SpyGlass CDC解決方案規則的上述調試數據。

4)基于實例來過濾違例

????????在處理大型設計時,設計師會被分配特定的設計實例。在這種情況下,設計師需要關注特定實例中報告的違規情況。為了幫助設計人員快速定位特定實例上的違規,SpyGlass CDC提供了基于實例的過濾機制。在此機制中,設計人員可以基于實例篩選違規。

5)解決多種CDC共同的違例問題

????????在大量的SpyGlass CDC違例中,大多數是以下情況:

- 不正確的設置

- 可以安全忽略的明顯問題

????????本節描述了以下很多違例行為常見的根本原因:

- Crossing發生或者結束于black box

- 錯誤的Case Analysis設置

- 源Flip-Flops產生靜態信號

- 噪聲

????????在關注rule相關的問題之前,應該首先考慮解決上述問題。解決了上述問題并重新運行SpyGlass CDC之后,您應該會看到更小、更易于管理的問題集。

????????注意:處理CDC問題時,千萬不要通過waving。如果你采用這種方法,就有可能掩蓋一個真正的問題。

(1)Crossing發生或者結束于black box

????????SpyGlass CDC分析依據如下:

- 能夠通過路徑進行跟蹤

- 一定程度的功能性理解

????????在black box的上游和下游都無法實現上述目標。

????????要消除這個問題,特定的約束為SpyGlass CDC提供一個部分模型,如下所述:

- 使用以下方法為black box的輸入輸出分配一個域:

- 對black box輸出使用abstract_port約束

- 對black box輸入使用signal_in_domain約束

- 使用assume_path約束對從black box輸入到輸出建模為直通路徑。

(2)錯誤的Case Analysis設置

????????檢查否正確地設置了set_case_analysis約束。

????????例如,你可能會看到錯誤的原因是,所有的功能模式和所有的測試模式都是同時激活的,而實際上這些模式中的許多模式永遠不會同時激活。要把test相關的信號用set_case_analysis約束。

(3)源Flip-Flops產生靜態信號

????????如果源觸發器產生一個靜態信號,可能不需要同步。比如說配置信號,這些信號通常在開機/啟動時設置,然后不再更改。可以從芯片架構師獲得關于哪些信號屬于這種情況,并使用準靜態約束quasi_static?來約束這些信號。

(4)噪聲(Noise)

????????在SpyGlass CDC驗證的主要挑戰之一是管理大量的違規。你可以通過特定的設置和設置檢查步驟來降低這些“噪聲”的干擾。

學習筆記整理系列三)

:線程池+并發編程+分布式設計+中間件)

)

)