隨著現代處理器技術的發展,在互連領域中,使用高速差分總線替代并行總線是大勢所趨。與單端并行信號相比,高速差分信號可以使用更高的時鐘頻率,從而使用更少的信號線,完成之前需要許多單端并行數據信號才能達到的總線帶寬。

PCI總線使用并行總線結構,在同一條總線上的所有外部設備共享總線帶寬,而PCIe總線使用了高速差分總線,并采用端到端的連接方式,因此在每一條PCIe鏈路中只能連接兩個設備。這使得PCIe與PCI總線采用的拓撲結構有所不同。PCIe總線除了在連接方式上與PCI總線不同之外,還使用了一些在網絡通信中使用的技術,如支持多種數據路由方式,基于多通路的數據傳遞方式,和基于報文的數據傳送方式,并充分考慮了在數據傳送中出現服務質量QoS (Quality of Service)問題。

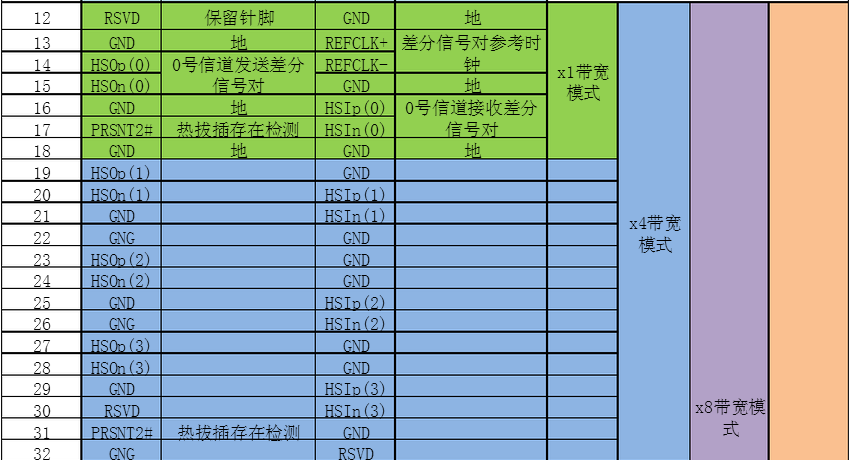

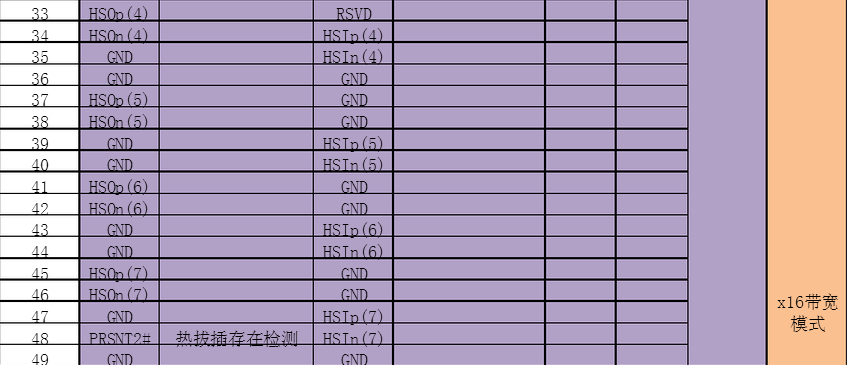

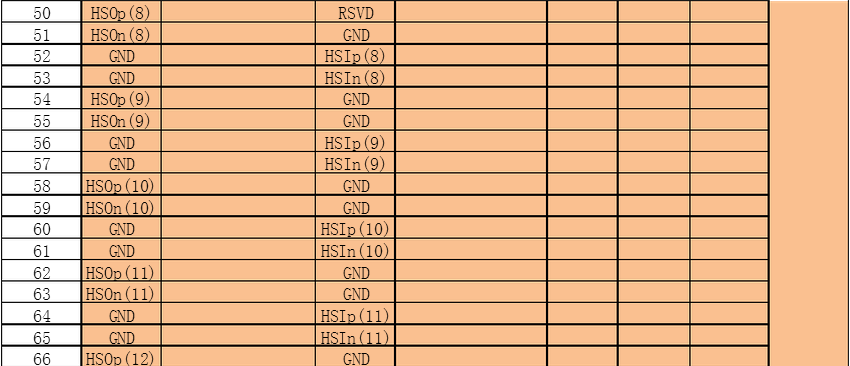

? PCIe引腳定義如下,有4種接口尺寸,每種接口的1到11對引腳都是一樣的,剩下的是差分數據線和時鐘,數據線數量不同對應的PCIe尺寸也不一樣,X1的PCIe板子可以插在X4的插槽上。

![[luoguP2774] 方格取數問題(最大點權獨立集)](http://pic.xiahunao.cn/[luoguP2774] 方格取數問題(最大點權獨立集))

)

方法詳解)