-

接地必須是一個低阻抗連接,以使回流電流不受干擾地流回各自的源。接地面連接盡量短且直。使用過孔連接接地線時,應并聯多個過孔,以減小對地阻抗。

-

混合信號布局有時包含在一個位置捆綁在一起的單獨的模擬和數字地平面;但是,當模擬、數字和電源組件放置得當時,不需要分離接平面。元器件的適當放置將模擬、數字和電源電路劃分到不同的PCB區域,以防止數字返回電流耦合到敏感的模擬電路中。

-

為了獲得最佳性能,將整個PCB層專用于接地平面,并且不要在該層上路由任何其他信號走線。然而,根據特定形狀因素的限制,單一地平面可能是不可能的。如果需要分離地平面,則在ADC處進行連接。不要在多個位置連接單獨的接地面,因為這種配置會產生接地回路。模擬和數字接地采用單一平面,避免了接地環路。

-

如果應用中需要隔離,則隔離ADC和控制器之間的數字信號,或提供從控制器到其余系統的隔離。如果使用外部晶體提供ADC時鐘,則使用短直接走線將晶體和負載電容器直接放置到ADC引腳上。

-

電源引腳必須用低esr陶瓷電容器旁路。使用短的、直接的走線將旁路電容器盡可能靠近電源引腳。為了獲得最佳性能,在旁路電容器的接地側連接上使用低阻抗連接。流動的供應電流通過旁路電容引腳,然后到供應引腳,使旁路最有效(也稱為開爾文連接)。如果多個adc在同一PCB板上,請使用寬電源走線或專用電源平面,以盡量減少adc之間串擾的可能性。

-

如果模擬輸入使用外部濾波,盡可能使用c0g型陶瓷電容器。C0G電容器具有性能穩定、低噪聲等特點。理想情況下,將差分信號成對布線,以盡量減少走線之間的環路面積。對于ADC CAPP和CAPN引腳,使用短直接走線將4.7-nF C0G電容放置在引腳附近。將數字電路走線(如時鐘信號)從所有模擬引腳上引開。注意,內部參考輸出返回與AVSS電源共享相同的引腳。為盡量減少電源走線和參考回波走線之間的耦合,應將兩條走線分開布線;理想情況下,作為AVSS引腳的星形連接。

-

重要的是串行接口的SCLK輸入沒有噪聲和故障。即使使用相對較慢的SCLK頻率,短的數字信號上升和下降時間也可能導致過度的振鈴和噪聲。為了獲得最佳性能,請保持數字信號走線短,根據需要使用終端電阻,并確保所有數字信號直接在地平面上方布線,盡量減少過孔的使用。

-

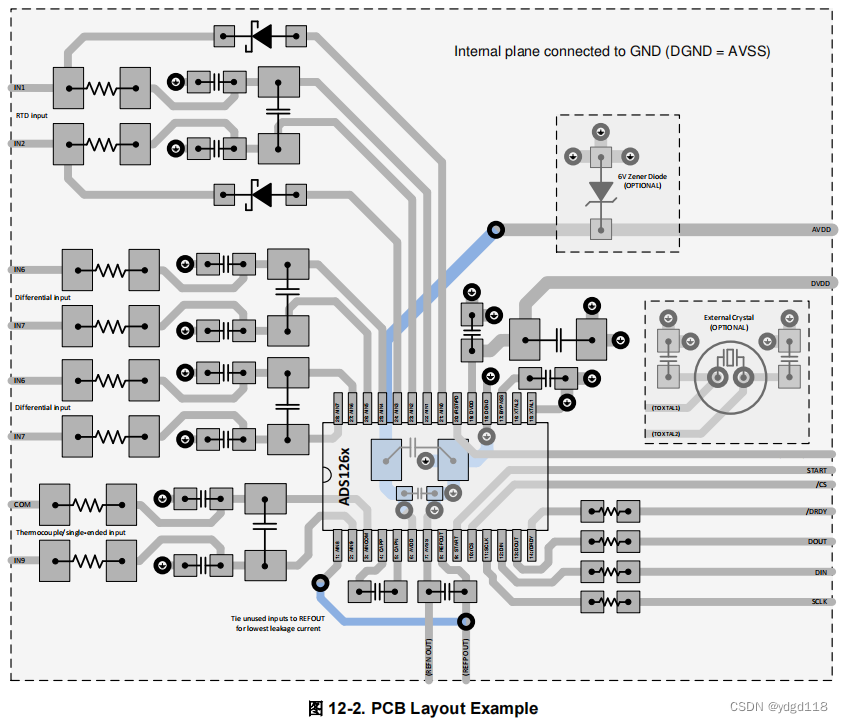

布局示例:

圖12-2是ADS1262和ADS1263的示例布局,至少需要三個PCB層。示例電路顯示為單個模擬電源(5 V)連接和外部晶體振蕩器。在本例中,內層用于接地平面,外層用于信號和電源走線。如果使用四層PCB,則將額外的內層專用于路由電源走線。ADC的方向從左到右顯示,以盡量減少模擬和數字信號走線的交叉。PCB劃分為模擬信號從左走,數字信號從右下走,電源從右上走。模擬電源旁路電容放置在底層與ADC相對的位置,以使參考和PGA輸出電容更靠近ADC。

圖12-2是ADS1262和ADS1263的示例布局,至少需要三個PCB層。示例電路顯示為單個模擬電源(5 V)連接和外部晶體振蕩器。在本例中,內層用于接地平面,外層用于信號和電源走線。如果使用四層PCB,則將額外的內層專用于路由電源走線。ADC的方向從左到右顯示,以盡量減少模擬和數字信號走線的交叉。PCB劃分為模擬信號從左走,數字信號從右下走,電源從右上走。模擬電源旁路電容放置在底層與ADC相對的位置,以使參考和PGA輸出電容更靠近ADC。

)

)