專欄前言

本專欄的內容主要是記錄本人學習Verilog過程中的一些知識點,刷題網站用的是牛客網

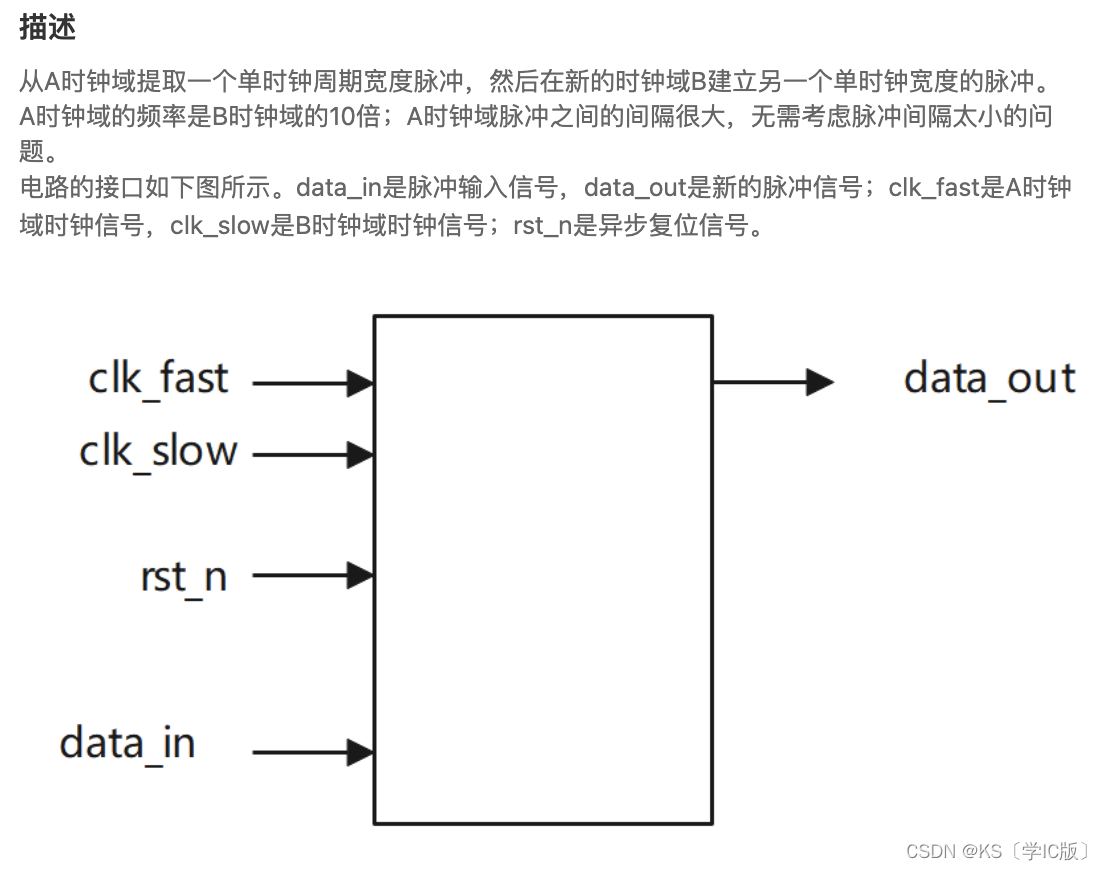

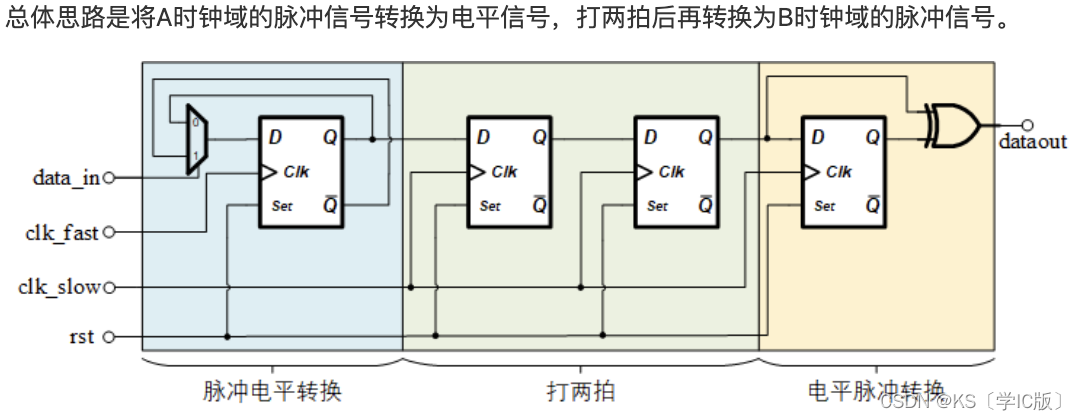

`timescale 1ns/1nsmodule pulse_detect(input clk_fast , input clk_slow , input rst_n ,input data_in ,output dataout

);reg data_level, data_level1, data_level2, data_level3 ; // 脈沖信號轉電平信號always @ (posedge clk_fast or negedge rst_n) begin if (~rst_n) data_level <= 0 ; else data_level <= data_in ? ~data_level : data_level ; // datain是一個單周期的脈沖信號,這樣可以轉換成高電平或者低電平信號。電平信號更容易做跨時鐘域處理end// 電平信號打兩拍再轉為脈沖信號,跨時鐘域傳輸,打拍減小亞穩態概率always @ (posedge clk_slow or negedge rst_n) begin if (~rst_n) begin data_level1 <= 0 ; data_level2 <= 0 ; data_level3 <= 0 ; endelse begin data_level1 <= data_level ; data_level2 <= data_level1 ;data_level3 <= data_level2 ; endend// 前后兩個時鐘周期的值不一致時,異或會把輸出拉高,也就等同于把跳變轉變成了電平assign dataout = data_level3 ^ data_level2 ;endmodule

一定數量的行)

和庫(Library)的區別)

企業項目如何使用jwt?)

:信息流控制之IOC容器)