在Verilog中使用任務task

- 1,任務目的

- 2,RTL代碼,交換

- 3,測試代碼

- 4,波形顯示

1,任務目的

(1)掌握任務在verilog模塊設計中的應用;

(2)學會在電平敏感列表的always中使用拼接操作、任務和阻塞賦值等語句,并生成復雜組合邏輯的高級方法。

當我們希望能夠將一些信號進行運算并輸出多個結果時,采用函數結構就顯得很不方便,但是采用任務結構在這方面優勢則十分突出。任務本身并不返回計算值,但它通過類似c語言中的形參和實參的數據交換,非常容易地實現運算結果的調用。

此外,還常利用任務來包裝模塊設計中的許多復雜任務的過程,將許多復雜的操作步驟用一個命名清晰易懂的任務隱藏起來,大大提高程序的可讀性。

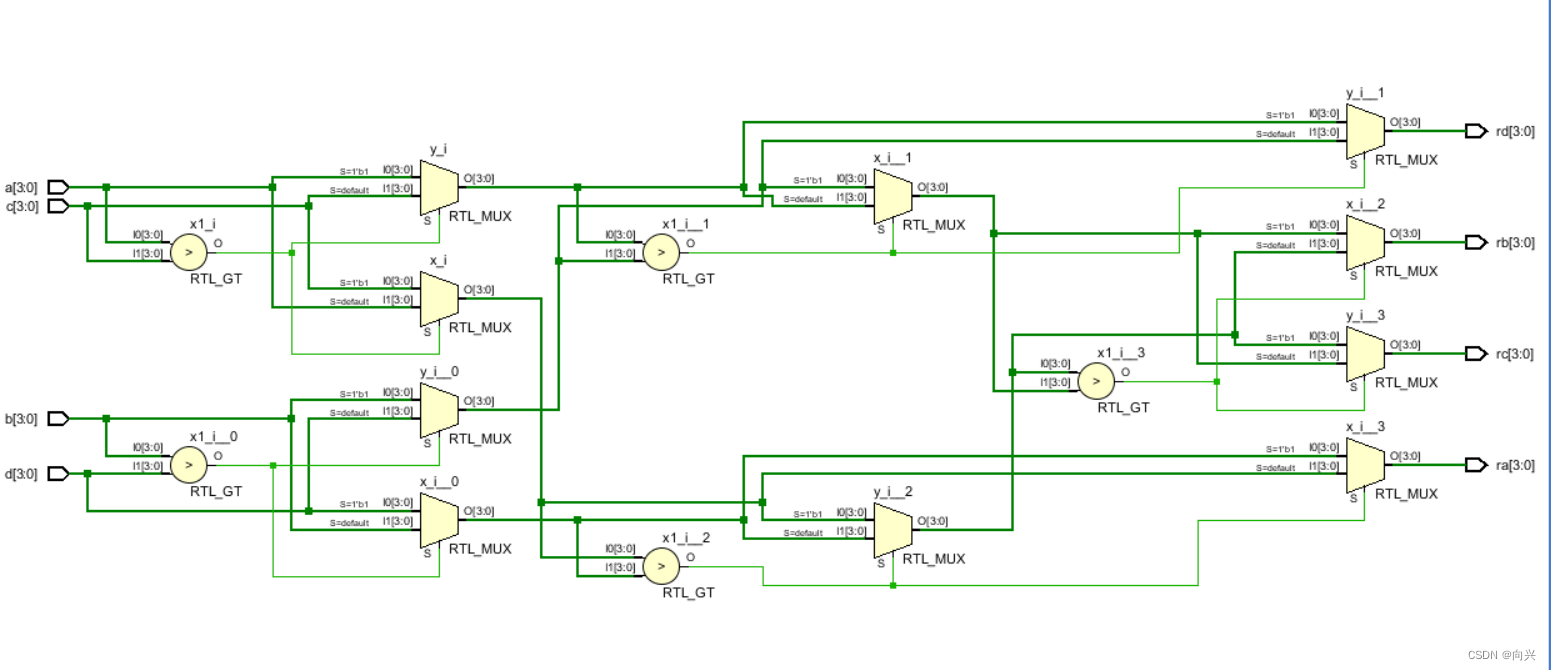

2,RTL代碼,交換

// 在verilog中 使用任務 task

module sort4(

ra, rb, rc, rd,

a, b, c, d

);input [3:0] a, b, c, d;

output reg [3:0] ra, rb, rc, rd;reg [3:0] va, vb, vc, vd;always@(a or b or c or d) begin{va, vb, vc, vd} = {a, b, c, d};sort2(va, vc); // va, vc 互換sort2(vb, vd); // vb, vd 互換sort2(va, vb); // va, vb 互換sort2(vc, vd); // vc, vd 互換sort2(vb, vc); // vb, vc 互換{ra, rb, rc, rd} = {va, vb, vc, vd};

endtask sort2;

inout [3:0] x, y;

reg [3:0] tmp;if(x > y) begintmp = x; // x與y變量的內容互換,要求順序執行,則采用阻塞賦值方式x = y;y = tmp;end

endtaskendmodule

3,測試代碼

// 測試代碼

module sort4_top;

reg [3:0] a, b, c, d;

wire [3:0] ra, rb, rc, rd;initial begina = 0; b = 0; c = 0; d = 0;repeat(50)

begin

#100 a = {$random}%15;b = {$random}%15;c = {$random}%15;d = {$random}%15;

end#100 $stop;

endsort4 u_sort4(

.a (a),

.b (b),

.c (c),

.d (d),

.ra (ra),

.rb (rb),

.rc (rc),

.rd (rd)

);endmodule

4,波形顯示

)

匹配規則語法和多行日志匹配設置)