專欄前言

本專欄的內容主要是記錄本人學習Verilog過程中的一些知識點,刷題網站用的是牛客網

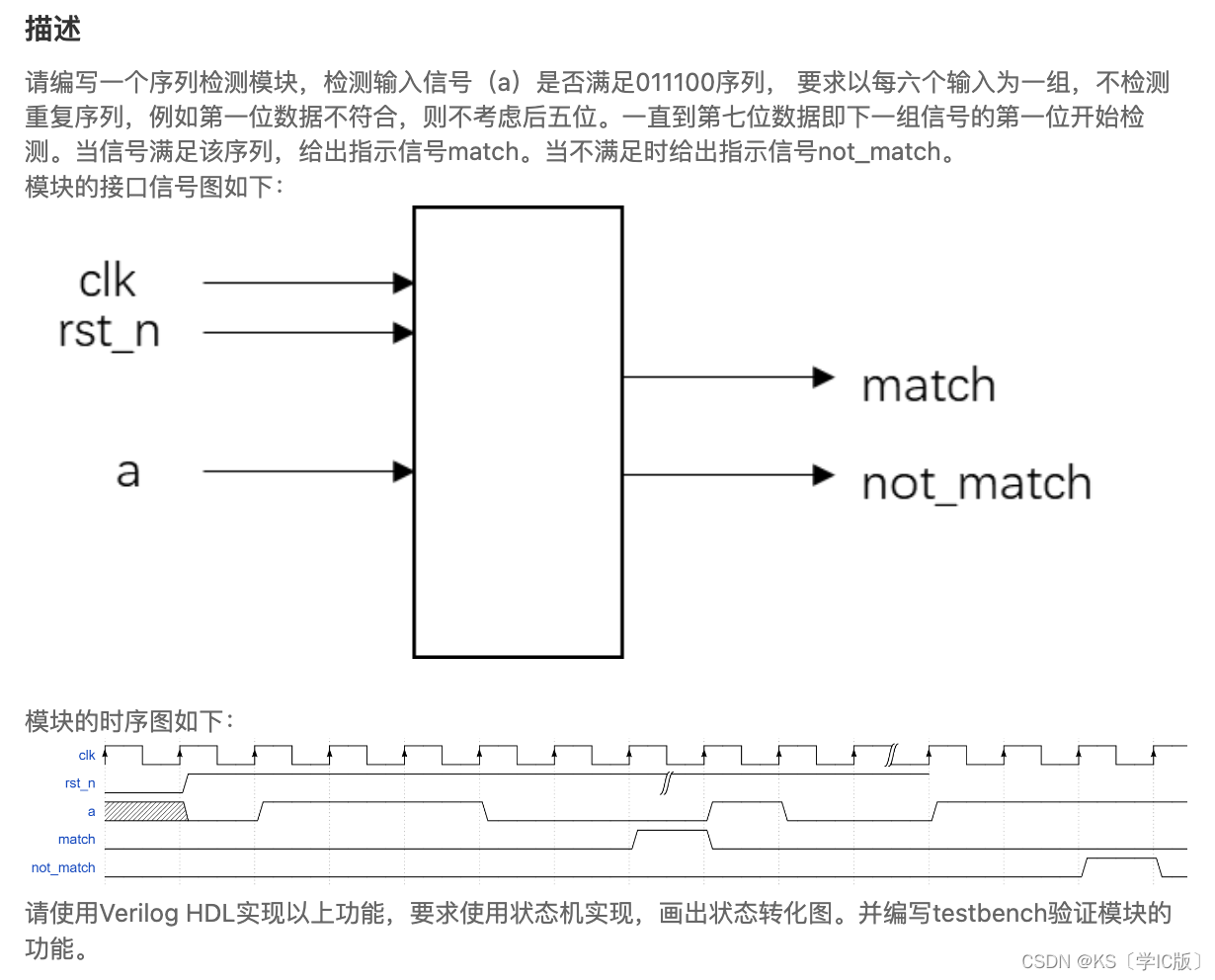

????????題目要求檢測a的序列,a為單bit輸入,每個時刻可能具有不同的值, 當連續的六個輸入值符合目標序列表示序列匹配,當六個輸入值的一個或多個不符合則表示序列不匹配。

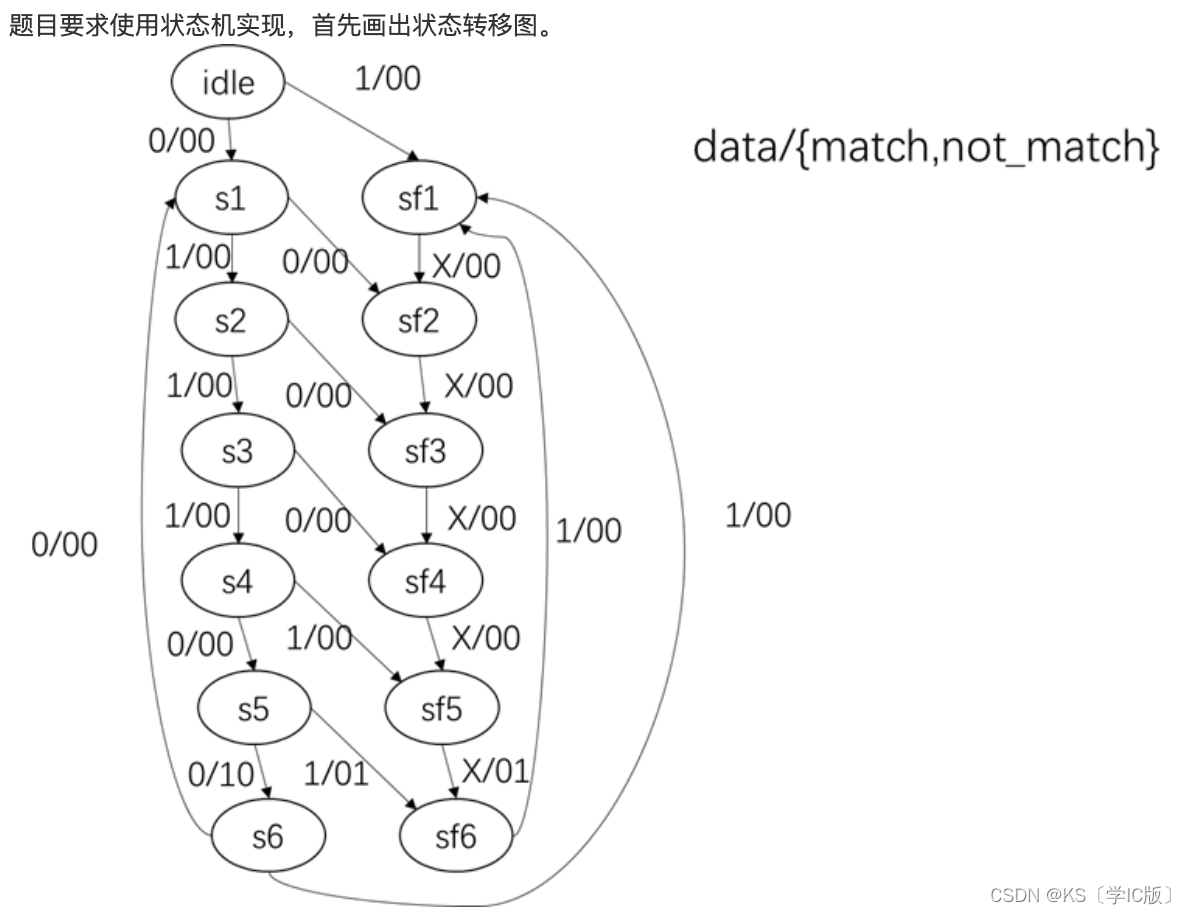

????????值得注意的是:題目要求以六位數據為一組,不同于常見的序列檢測,要求檢測重復序列,在畫狀態轉移圖時要注意,例如第一位不匹配,不應該返回到初始狀態去進行第一位的判斷,因為此時的輸入是第二位數值,題目要求不對該數值做判斷,而需要等到六個時鐘周期之后,即第七位數據(第二組數值的第一位)再判斷是否匹配目標序列的第一位。

`timescale 1ns/1ns

module sequence_detect(input clk,input rst_n,input data,output reg match,output reg not_match);// 011100reg [3:0] pstate, nstate ; // 當前狀態、下一狀態parameter idle = 4'b0,s1 = 4'd1,s2 = 4'd2,s3 = 4'd3,s4 = 4'd4,s5 = 4'd5,s6 = 4'd6,sf1 = 4'd7, sf2 = 4'd8,sf3 = 4'd9, sf4 = 4'd10,sf5 = 4'd11, sf6 = 4'd12 ;always @ (posedge clk or negedge rst_n) begin if (~rst_n) pstate <= idle ; else pstate <= nstate ; endalways @ (pstate or data) begin // 對應狀態轉移圖case (pstate) idle : if (data == 0) nstate = s1 ; //0else nstate = sf1 ; s1 : nstate = data ? s2 : sf2 ; //1s2 : nstate = data ? s3 : sf3 ; //1s3 : nstate = data ? s4 : sf4 ; //1s4 : nstate = data ? sf5 : s5 ; //0s5 : nstate = data ? sf6 : s6 ; //0s6 : nstate = data ? sf1 : s1 ; sf1 : nstate = sf2 ;sf2 : nstate = sf3 ;sf3 : nstate = sf4 ;sf4 : nstate = sf5 ;sf5 : nstate = sf6 ;sf6 : nstate = data ? sf1 : s1 ;default :nstate = idle ; endcaseendalways @ (pstate or data or rst_n) begin // 輸出if (!rst_n) begin match <= 1'b0 ; not_match <= 1'b0 ; endelse if (pstate == s6) begin match <= 1'b1 ;not_match <= 1'b0 ; endelse if (pstate == sf6) begin match <= 1'b0 ; not_match <= 1'b1 ; endelse begin match <= 1'b0 ; not_match <= 1'b0 ; endendendmodule

)

)

)